ServerWorks HEsl: DDR bandwidth without DDR SDRAM

by Anand Lal Shimpi on February 7, 2001 8:16 AM EST- Posted in

- CPUs

Connecting it all together

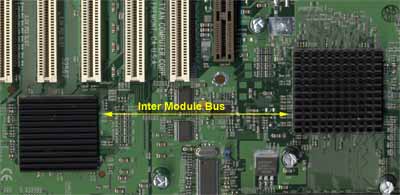

With a two 64-bit PCI buses running at 33 and 66MHz, there is a clear need for a high-bandwidth connection from the 64-bit PCI Bridge to the North Bridge. As you can probably guess, ServerWorks was already on the ball when they developed what they like to call the "Inter Module Bus" or IMB for short.

The IMB is a path from the North Bridge to the NB6555IO Bridge 2.0 which is essentially the 64-bit PCI Bridge which controls all of the 64-bit PCI slots on a HEsl board. With a 64-bit PCI bus running at 66MHz offering 533MB/s of bandwidth and another 64-bit PCI bus running at 33MHz offering a theoretical maximum of 266MB/s of bandwidth, this IMB has to be pretty quick in order to avoid creating a performance bottleneck. However since 64-bit PCI devices still aren't to the point where they are requiring 533MB/s of bandwidth the bus does not have to be quite that fast.

The trade-off ServerWorks made was to make the IMB a 16-bit wide bus capable of transferring at up to 1GB/s meaning that it is clocked at an incredible 500MHz. This narrow but very fast bus is reminiscent of the most recent trends in the PC hardware industry towards more serialized operation. From things like Intel's Hub Architecture (266MB/s, 8-bit interlink bus like the IMB) and RDRAM to the forthcoming Serial ATA specification, ServerWorks' IMB is also a very serialized protocol.

|

Bus Link Comparison | ||||||

|

Architecture |

Max. Transfer Rate | |||||

|

Intel Hub |

266MB/s | |||||

|

VIA V-Link |

266MB/s | |||||

|

ServerWorks 'IMB' |

1GB/s | |||||

Although ServerWorks wouldn't divulge too much information on it, they claim that there is some sort of an intelligent caching mechanism present to help manage the available bandwidth. There is a strong sense of secrecy about a lot of the technology behind the ServerWorks chipsets mainly because of fears that in this highly competitive industry the technology that they have worked so hard to build can be copied so very easily if too much is disclosed.

With all of this, the HEsl's South Bridge isn't even necessary other than to provide support for the 32-bit PCI bus and any IDE hard drives that may be used. The South Bridge does claim support for up to 4 USB ports.

0 Comments

View All Comments