Original Link: https://www.anandtech.com/show/1961

Spring IDF 2006: Introducing Intel's new Core processors

by Anand Lal Shimpi on March 7, 2006 12:06 PM EST- Posted in

- Trade Shows

Justin Rattner kicked off Intel's Spring Developer Forum with a talk about Energy Efficiency, inevitably involving a discussion about Conroe, Merom and Woodcrest.

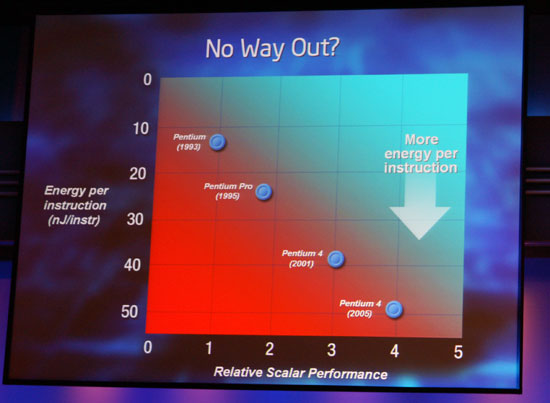

This slide below is particularly interesting as it is the first time Intel has actually disclosed this sort of information. The chart plots the amount of energy required to execute a single instruction as a function of processor performance. Obviously, the higher the performance, the lower the efficiency.

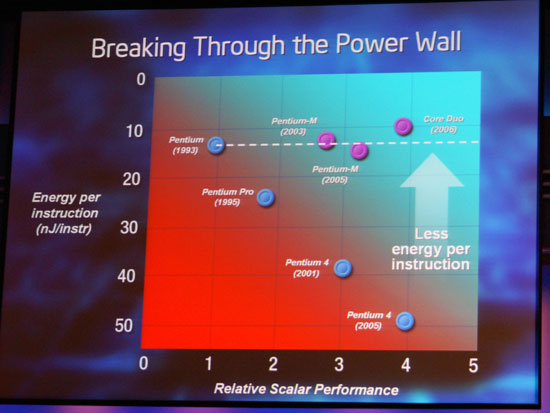

The next version of the slide includes the work from the Israel Design Center, more specifically the Pentium M and Core Duo.

The Pentium M was actually able to match the energy efficiency of the original Pentium processor. Succeeding generations of the Pentium M continued the trend, offering energy efficiency of the original Pentium while offering performance competitive with the Pentium 4 processor.

Introducing the Core Micro-Architecture

As expected, Justin Rattner announced the official name of Intel's next-generation micro-architecture: Core.

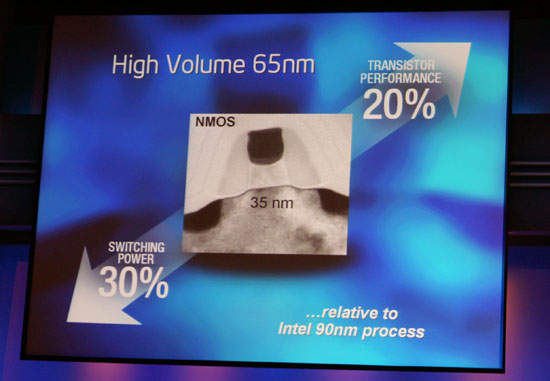

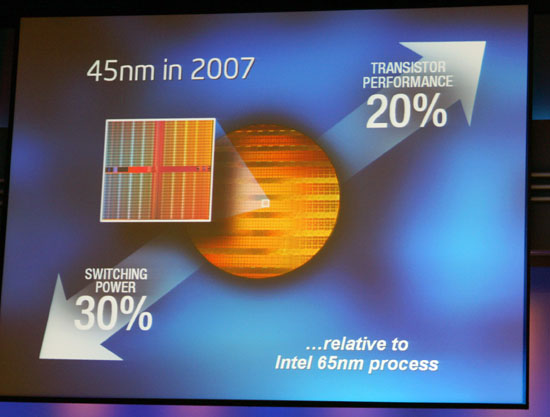

All of the Core based products will be based on Intel's 65nm manufacturing process, which we've already seen with the 65nm Core Duo and Core Solo based microprocessors. Intel claims that their 65nm manufacturing process offers 20% faster switching and 30% lower power.

Rattner also mentioned that by the middle of 2007 Intel would begin their transition to a 45nm manufacturing process.

Single Cycle SSE and Macro-Fusion in Core

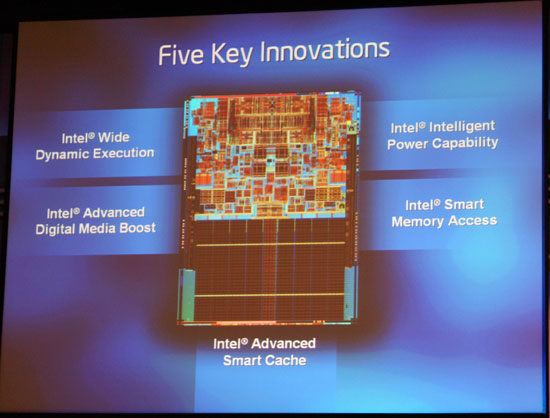

Not spending any time beating around the bush, Justin Rattner immediately jumped into the five key innovations in Intel's new Core micro-architecture.

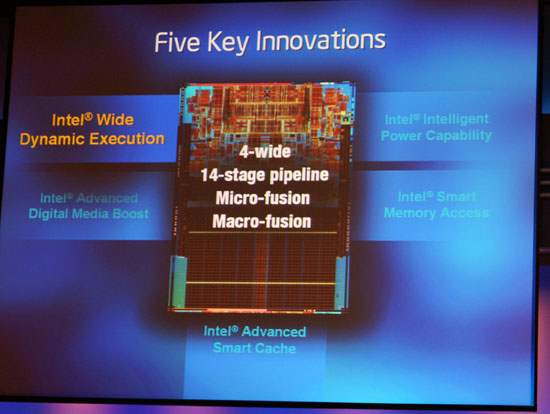

The 4-issue core and 14-stage pipeline were both disclosed at the last IDF and we already knew that the Pentium M's micro-ops fusion would make its way into Conroe, but what's new here is the support for macro fusion. While micro-ops fusion will allow decoded instructions to be sent down the pipe together (as "fused" instructions), macro fusion will allow x86 instructions (before the decode stage) to be fused together and sent down as a single instruction. The example of this that Rattner gave was that Compare and Jump instructions now become a single instruction in the pipeline thanks to Macro-fusion.

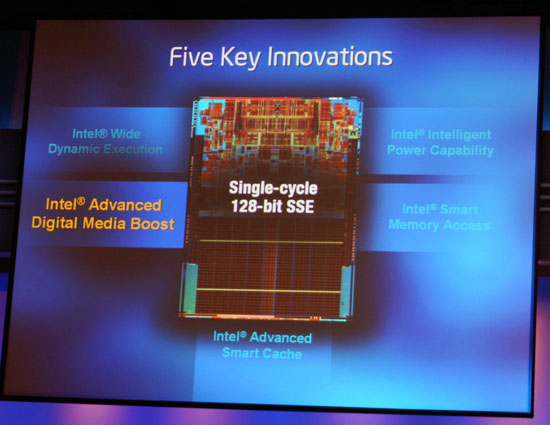

The next major feature of the Core micro-architecture is that now all 128-bit SSE instructions will execute in a single cycle. The single cycle throughput for all SSE instructions should offer some pretty hefty gains in any applications that make extensive use of SSE. We've confirmed that this applies to all SSEn instructions (SSE1/SSE2/SSE3). Updated: Intel clarified the single-cycle SSE item for us. The throughput (not latency) of all SSE instructions is now 1 cycle, whereas in the past it was generally a 2 cycle throughput. The increase in throughput will result in some pretty hefty performance gains in SSE optimized encoding applications.

Conroe, Merom and Woodcrest - General Performance Expectations

While we'll get a better idea of performance of Conroe, Merom and Woodcrest later today, Rattner did share some high level numbers:

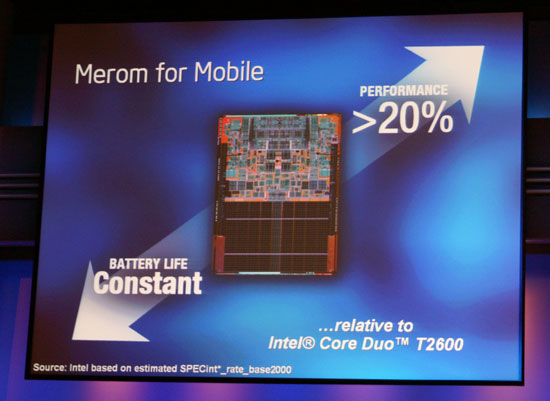

Merom offers 20% higher performance at a constant battery life compared to the Core Duo T2600.

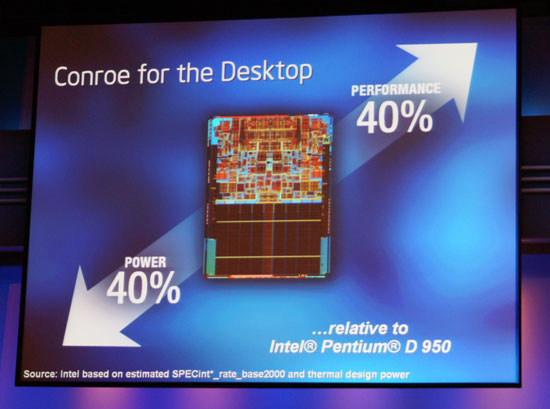

Conroe offers a 40% increase in performance with a 40% decrease in power compared to the Pentium D 950.

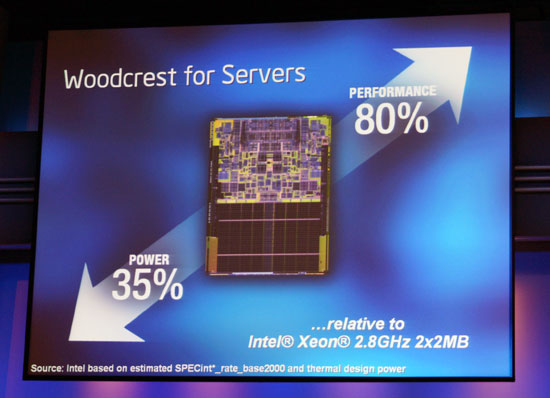

Woodcrest sees an 80% increase in performance and a 35% decrease in power compared to a Xeon 2.8GHz with two 2MB caches.

Obviously we've got no clue under what circumstances these figures were measured, but the numbers are exciting nonetheless.

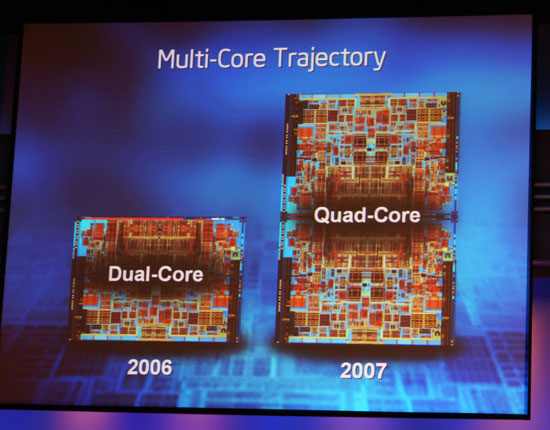

Both AMD and Intel have announced that they would have quad-core processors in 2007, however Rattner mentioned that there's no reason to expect 8-core processors in 2008 but rather further improvements on the ILP level to each one of those 2 or 4 cores.

The final focus on energy in Rattner's keynote was about the platform. Although currently the power consumption balance between the CPU and the rest of the platform (chipset, memory, display) is about 50/50, with the new Core processors only about 1/3 of the total system power consumption ends up being used by the CPU - meaning that platform power consumption now ends up being a limiting factor.

Pat Gelsinger's keynote has just begun, we'll be reporting on that next...