Intel's Haswell Architecture Analyzed: Building a New PC and a New Intel

by Anand Lal Shimpi on October 5, 2012 2:45 AM ESTHaswell Media Engine: QuickSync the Third

Although we still have one more generation to go before QuickSync can apparently deliver close to x86 image quality, Haswell doesn't shy away from improving its media engine.

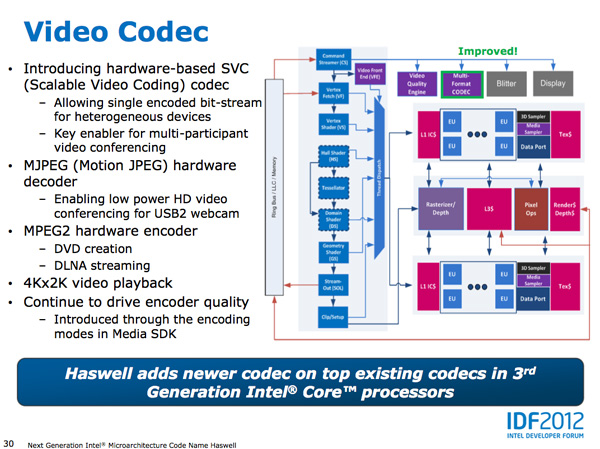

First and foremost is hardware support for the SVC (Scalable Video Coding) codec. The idea behind SVC is to take one high resolution bitstream from which lower quality versions can be derived. There are huge implications for SVC in applications that have varied bandwidth levels and/or decode capabilities.

Haswell also adds a hardware motion JPEG decoder, and MPEG2 hardware encoder.

Ivy Bridge will be getting 4K video playback support later this year, Haswell should obviously ship with it.

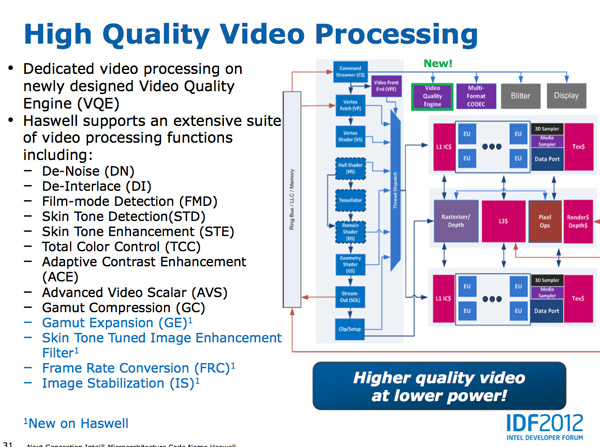

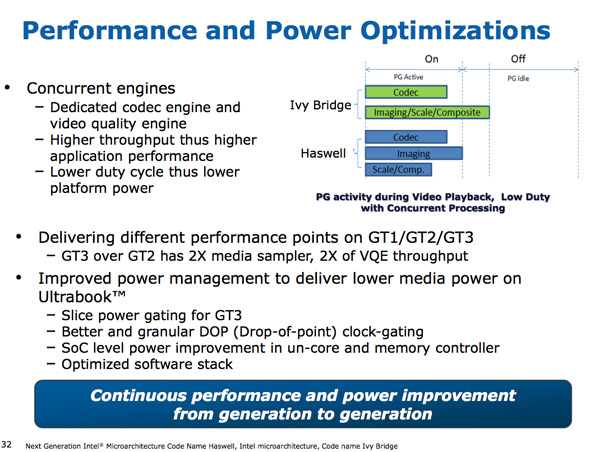

Finally there's a greater focus on image quality this generation, although as I mentioned before I'm not sure we'll see official support in a lot of the open source video codecs until Broadwell comes by. With added EUs we'll obviously see QuickSync performance improve, but I don't have data as to how much faster it'll be compared to Ivy Bridge.

245 Comments

View All Comments

kukreknecmi - Friday, October 5, 2012 - link

I hope i know it right. L3 on SB/IB doest used by GPU. L3 still servers as cache on system via memory controller. If GPU nneds to acess to memory, it sends request to memory controller. L3 is not directly accessable to GPU as a texture cache etc.On IB, they added a 512k cache which is seperated to half, 256k of it is used as texture system as backfeeding and other 256k half is used for other things.Article implies that L3 cache on IB is used as a texture buffer like on ordinary graphic cards. Only on Haswell L3 cache will be accessable and can be used as a some kind of GPU specific buffer.

Kevin G - Friday, October 5, 2012 - link

The confusing thing is that consumer Ivy Bridge parts have a L3 cache just for the GPU which is separate memory than the L3 cache that the CPU uses. The Ivy Bridge GPU's can use the CPU's L3 cache as the GPU's L4 cache to a degree.To confuse things further, the CPU side really has four levels of cache too. There is the small 1.5 KB micro-uop cache for instructions which comes before the 32 KB L1 instruction cache.

mayankleoboy1 - Friday, October 5, 2012 - link

From the article, its not very clear : Which platform (DT, Mobile, ultra mobile) will have the integrated voltage regulators/controllers ?Ryan Smith - Friday, October 5, 2012 - link

Ultra Mobile.Anand Lal Shimpi - Friday, October 5, 2012 - link

It's not clear how much of the VR circuitry gets integrated into Haswell or necessarily which parts will have it and which ones won't. Ultra mobile is a shoe in, but I've even heard of desktop parts getting it as well. We'll have to wait and see.DanNeely - Friday, October 5, 2012 - link

Rats. Reading the article I was hoping that Intel had decided to only bake the VRMs into their ultra-mobile parts. Better VRMs are an important factor in high end OCing; with desktop boards not cramped for space I really hope Intel keeps them off the package.Peanutsrevenge - Friday, October 5, 2012 - link

Seconded.However, I wonder whether the VRMs on high end mobos will still be an option, where the on package VRMs will simply extend the capabilities?

But given Intels recent distaste for overclocking, it wouldn't suprise me if we'll soon see CPUs completely locked from overclocking completely or only on E series, high profit chips.

Homeles - Saturday, October 6, 2012 - link

"However, I wonder whether the VRMs on high end mobos will still be an option, where the on package VRMs will simply extend the capabilities?"Bingo.

Homeles - Saturday, October 6, 2012 - link

Low end motherboards won't need them. High end overclocking boards will have them in addition to the ones on package.tuxRoller - Friday, October 5, 2012 - link

Using lvds reclocking you can reduce idle screen induced wakeups to 30 (ditto for the memory controller if the cpu supports self refresh for the sram ).eDP may allow even less.