Intel's Haswell Architecture Analyzed: Building a New PC and a New Intel

by Anand Lal Shimpi on October 5, 2012 2:45 AM ESTDecoupled L3 Cache

With Nehalem Intel introduced an on-die L3 cache behind a smaller, low latency private L2 cache. At the time, Intel maintained two separate clock domains for the CPU (core + uncore) and a third for what was, at the time, an off-die integrated graphics core. The core clock referred to the CPU cores, while the uncore clock controlled the speed of the L3 cache. Intel believed that its L3 cache wasn't incredibly latency sensitive and could run at a lower frequency and burn less power. Core CPU performance typically mattered more to most workloads than L3 cache performance, so Intel was ok with the tradeoff.

In Sandy Bridge, Intel revised its beliefs and moved to a single clock domain for the core and uncore, while keeping a separate clock for the now on-die processor graphics core. Intel now felt that race to sleep was a better philosophy for dealing with the L3 cache and it would rather keep things simple by running everything at the same frequency. Obviously there are performance benefits, but there was one major downside: with the CPU cores and L3 cache running in lockstep, there was concern over what would happen if the GPU ever needed to access the L3 cache while the CPU (and thus L3 cache) was in a low frequency state. The options were either to force the CPU and L3 cache into a higher frequency state together, or to keep the L3 cache at a low frequency even when it was in demand to prevent waking up the CPU cores. Ivy Bridge saw the addition of a small graphics L3 cache to mitigate this situation, but ultimately giving the on-die GPU independent access to the big, primary L3 cache without worrying about power concerns was a big issue for the design team.

When it came time to define Haswell, the engineers once again went to Nehalem's three clock domains. Ronak (Nehalem & Haswell architect, insanely smart guy) tells me that the switching between designs is simply a product of the team learning more about the architecture and understanding the best balance. I think it tells me that these guys are still human and don't always have the right answer for the long term without some trial and error.

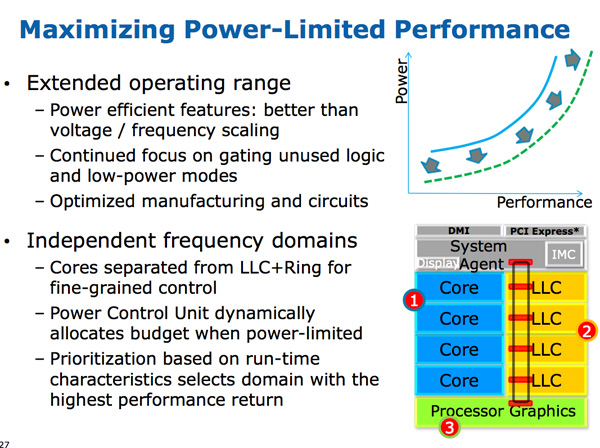

The three clock domains in Haswell are roughly the same as what they were in Nehalem, they just all happen to be on the same die. The CPU cores all run at the same frequency, the on-die GPU runs at a separate frequency and now the L3 + ring bus are in their own independent frequency domain.

Now that CPU requests to L3 cache have to cross a frequency boundary there will be a latency impact to L3 cache accesses. Sandy Bridge had an amazingly fast L3 cache, Haswell's L3 accesses will be slower.

The benefit is obviously power. If the GPU needs to fire up the ring bus to give/get data, it no longer has to drive up the CPU core frequency as well. Furthermore, Haswell's power control unit can dynamically allocate budget between all areas of the chip when power limited.

Although L3 latency is up in Haswell, there's more access bandwidth offered to each slice of the L3 cache. There are now dedicated pipes for data and non-data accesses to the last level cache.

Haswell's memory controller is also improved, with better write throughput to DRAM. Intel has been quietly telling the memory makers to push for even higher DDR3 frequencies in anticipation of Haswell.

245 Comments

View All Comments

dishayu - Friday, October 5, 2012 - link

Woah! I did not even think of that. That is VERY compelling but i can't do without unlocked multiplier, so there is no perfect processor for me still :(StevoLincolnite - Friday, October 5, 2012 - link

Or just go with a Socket 2011 Core i7 3930K like I have and do a little bit of undervolting and has no IGP's.I think the reason why the Desktop space has seen decreasing/stagnant sales is simply because allot of people see no need to upgrade.

A Core 2 Quad Q6600 @ 3.6ghz, with a decent chunk of Ram and a decent graphics card is actually fairly capable of running almost every game at maximum settings.

Heck I know people who are perfectly happy sitting with a Pentium 4 for basic web use.

I think a change needs to happen where software catches up with hardware to give people a reason to upgrade and drive sales which might reinvigorate Intel and AMD to innovate.

Windows 8 and the next generation consoles might actually help in that regard.

De_Com - Friday, October 5, 2012 - link

Well said Steve. Couldn't agree with you more.

I'm running a Core 2 Extreme QX6850 at 3.4ghz, 1066Mhz DDR2 Ram and a GTX295 and it still rocks all the newest games at or close to max settings.

Will have this system 4 years this November.(all except the GTX295, which was upgraded from a 9800 GX2), even now I'm thinking that was a waste of cash.

I've gone to upgrade at least twice each year, but can't justify it.

The only place I'd see returns is in the power costs, but hey, whats a few extra cents.....

The system meets my needs, and forking out for a similar system today would cost around the €1800 mark.

Until the software can better utilize the components I'm holding out until Summer 2013, that'll be over 4 years I've gotten out of this system. Up until 2008 I slavishly upgraded every year or 2.

lukarak - Saturday, October 6, 2012 - link

This (late) December, i will have had my i7 for 4 years, and i have not seen a single reason to upgrade. The GPU is 2.5 years old (GTX480, was 280 before that).A x58 motherboard has 6 memory slots, and now houses 24 GB of ram for virtual machines, which can go 48 GB for a reasonable price.

I just don't see the need to do anything more, and this will probably fail from old age before i would need a drastically faster machine.

xaml - Thursday, May 23, 2013 - link

"but hey, whats a few extra cents....."Sure, it's probably not your generation to take the hit, having to deal with the consequences of energy excesses.

DanNeely - Friday, October 5, 2012 - link

Is that actually an IGPless chip, or just a standard LGA1155 quadcore chip with a disabled IGP.csroc - Friday, October 5, 2012 - link

I don't mind power savings, the few times my system is idle it could certainly benefit but overall it would mean reduced consumption even under load. My system just doesn't spend enough time in idle with my Q9450.Ultimately it does seem as though the software demand for faster CPU hardware has slowed and between that and the lack of real competition, so has the development.

If it weren't for the fact that I need more RAM or wanted faster photo processing (and may start doing some video) I'd probably keep what I've got a bit longer. My Q9450 hasn't held me back from playing any games yet. The 20% OC I've been running doesn't hurt but ultimately a lot of things just aren't CPU limited anymore.

Kidster3001 - Monday, October 15, 2012 - link

If you're playing 3D games then your CPU is likely "idle" 50%-75% of the time. Idle time does not just mean when the display is off.IanCutress - Friday, October 5, 2012 - link

You may think this as a result of all the low power talk, but Haswell is doing something rather important on the peak performance side. The increase in the size of the execution engine is important - adding in another integer ALU and another load/store means that in workloads that share INT and FPU performance (think loop counters which store an INT for loop iteration then perform some FP calcs) will improve. By increasing the bandwidth available and being able to keep the two FPU fed with info means a greater throughput as long as the bandwidth and thread switching can hide any additional L3 latency. Personally I'm thinking this may be a subtle move towards more threads per core in future architectures. Some of the non x86 are abusing 8 threads/core with improvement gains, so I wonder if that would be possible here. Ideally we would like every port on the execution engine to do everything, with a single pipeline feeding it and excellent branch prediction to help with single thread speed. Smaller nodes help with that silicon real estate, or someone will stumble on a better/smaller way to actually physically create these things.Ian

DanNeely - Friday, October 5, 2012 - link

I'm curious what IBM/Oracle's high SMT designs look like on the execution port side. As long as it's business as usual I doubt Intel will ever make all the ports do everything because it would just be hogging a huge amount of die area when the odds of each thread doing all of the same instruction type constantly are very low. Smaller bursts of one type can be spread out using OOOE.