Apple iPhone 4S: Thoroughly Reviewed

by Anand Lal Shimpi & Brian Klug on October 31, 2011 7:45 PM EST- Posted in

- Smartphones

- Apple

- Mobile

- iPhone

- iPhone 4S

The Memory Interface

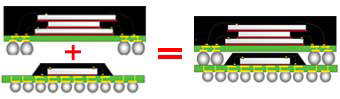

Most SoCs deployed in smartphone designs implement a package-on-package (PoP) stack of DRAM on top of the SoC package. As its name implies, PoP refers to the physical stacking of multiple packages and not layering of raw die. The SoC is typically the lowest level with its memory bus routed to pads on the top of the package. A DRAM package is then stacked on top of the SoC. Avoiding having to route high-speed DRAM lines on the PCB itself not only saves space but it further reduces memory latency.

An example of a PoP stack

The iPhone has always used a PoP configuration for its SoCs and Apple has always been kind enough to silkscreen the part number of the DRAM on the outer package of the SoC. In the past we've seen part numbers from both Samsung and Elpida on Apple SoCs. As both companies can provide similarly spec'd DRAM it makes sense for Apple to source from two suppliers in the event that one is unable to meet demand for a given period.

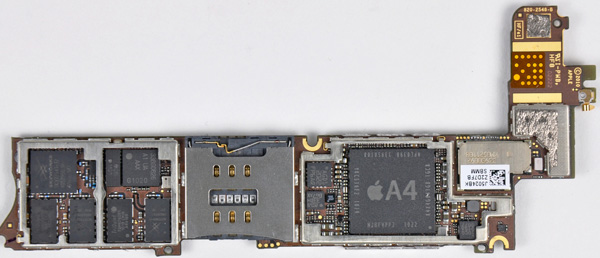

iPhone 4 mainboard, courtesy iFixit

If we look at iFixit's teardown of the iPhone 4 we see the following DRAM part number: K4X4G643G8-1GC8. Most DRAM vendors do a pretty bad job of providing public data about their part numbers used in chip stacks, so we have to do a little bit of inferring to figure out exactly what Apple used last generation.

The first three characters tell us a bit about the type of DRAM. The K means it's memory, the 4 tells us that it's DRAM and the X tells us that it's mobile DDR (aka LPDDR). The next two characters tell us the density of the DRAM, in this case 4G is translated literally to 4Gbit or 512MB. Characters 6 and 7 are also of importance - they tell us the DRAM organization. Samsung's public documentation only tells us that 16 refers to a 16-bit interface and 32 here would mean a 32-bit interface. Based on that we can safely assume that the 4Gbit DRAM on the A4 is 64-bits wide. In the mobile world a 32-bit interface typically refers to a single channel, which confirms the A4's DRAM interface is two 32-bit channels wide.

The last two characters in the part number, C8, tell us the source clock frequency of the DRAM. Samsung's datasheets tell us that C8 corresponds to a 5ns cycle time with a CAS latency of 3 clocks. Taking the inverse of that gives us 200MHz (frequency = 1 / clock period). Remember, we're talking about double data rate (DDR) SDRAM so data is transferred at both the rising and falling edges of the clock, making the effective data rate 400MHz.

All of this tells us that the iPhone 4's A4 SoC has a 64-bit wide LPDDR1 memory interface with a 400MHz data rate. Multiply all of that out and you get peak theoretical bandwidth of 3.2GB/s. DDR memory interfaces are generally 80% efficient at best so you're looking at a limit of around 2.5GB/s. To put this in perspective, the A4 has as much memory bandwidth as the original AMD Athlon 64 released in 2003.

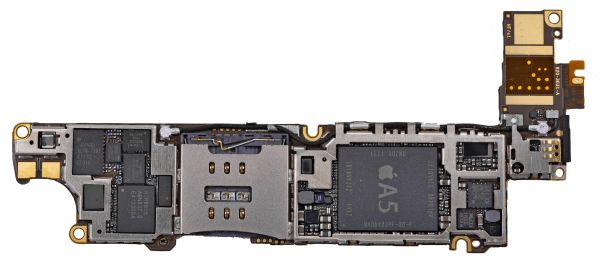

iPhone 4S mainboard, courtesy iFixit

With the A5 Apple definitely stepped up the memory interface. Once again we turn to iFixit's teardown of the iPhone 4S to lift that oh-so-precious part number: K3PE4E400B-XGC1.

The K once again tells us we're dealing with Samsung memory, while the 3P reveals there are two mobile DDR2 with 4n prefetch (aka LPDDR2-S4) DRAM die on the package. Why not a 4 this time? Technically the 4 refers to a discrete DRAM while the 3 implies a DRAM stack, obviously both are stacked DRAM so I'm not entirely sure why there's a difference here. Each of the next two E4s tell us the density of the two DRAM die. Samsung's public documentation only goes up to E3 which corresponds to a 1Gbit x32 device. Given that we know the A5 has 512MB on-package, E4 likely means 2Gbit x32 (256MB 32-bit). There are two E4 die on package which makes up the 512MB 64-bit DRAM stack.

Once again the final two characters reveal the cycle time of the DRAM: 2.5ns. The inverse of 2.5ns gives us a 400MHz clock frequency, or an 800MHz data rate (source clock frequency is actually 200MHz, but with a 4n prefetch we can transfer at effectively 800MHz). Peak bandwidth to the A5 is roughly double that of the A4: 6.4GB/s. This is as much memory bandwidth as AMD's Athlon 64 platform offered in late 2004, just 7 years later and in a much smaller form factor.

The doubling of memory bandwidth requires a sufficiently large workload to really show it. We see this in Geekbench's memory bandwidth results where the A5 doesn't appear to offer any more bandwidth than the A4 in all but one of the tests:

| Memory Bandwidth Comparison - Geekbench 2 | ||||

| Apple iPhone 4 | Apple iPhone 4S | |||

| Overall Memory Score | 593 | 700 | ||

| Read Sequential | 318.7 MB/s | 302.3 MB/s | ||

| Write Sequential | 704.9 MB/s | 809.2 MB/s | ||

| Stdlib Allocate | 1.55 Mallocs/sec | 1.55 Mallocs/sec | ||

| Stdlib Write | 1.25 GB/s | 2.54 GB/s | ||

| Stdlib Copy | 724.5 MB/s | 490.1 MB/s | ||

| Overall Stream Score | 280 | 281 | ||

| Stream Copy | 413.5 MB/s | 396.4 MB/s | ||

| Stream Scale | 313.3 MB/s | 317.4 MB/s | ||

| Stream Add | 518.0 MB/s | 527.1 MB/s | ||

| Stream Triad | 363.6 MB/s | 373.9 MB/s | ||

Memory bandwidth tests are extremely sensitive to architecture optimizations, particularly for single threaded tests like these so I wouldn't read too much into the cases where you see no gains or a drop.

The increase in raw memory bandwidth makes a lot of sense. Apple doubled the number of CPU cores on the A5, with each one even more bandwidth hungry than the single A4 core. The 4x increase in GPU compute combined with an increase in clock speeds give the A5 another big consumer of bandwidth. Add things like 1080p video capture and the memory bandwidth increase seems justified.

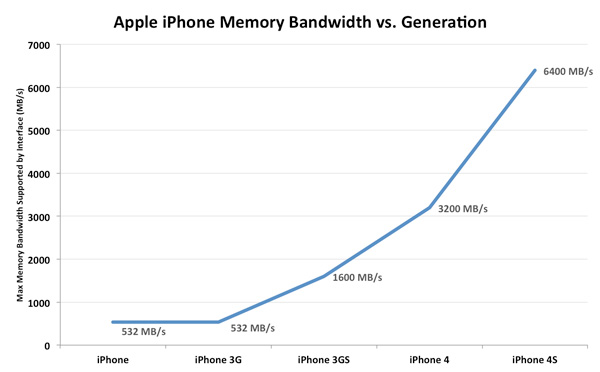

Looking back at the evolution of the iPhone's memory interface gives us an idea of just how quickly this industry has been evolving. Back in 2007 the original iPhone debuted with a 16-bit wide LPDDR-266 memory interface connected to a meager 128MB of DRAM. The 3GS delivered a huge increase in memory bandwidth by doubling the interface width and increasing the data rate to 400MHz. Scaling since then has been even more dramatic:

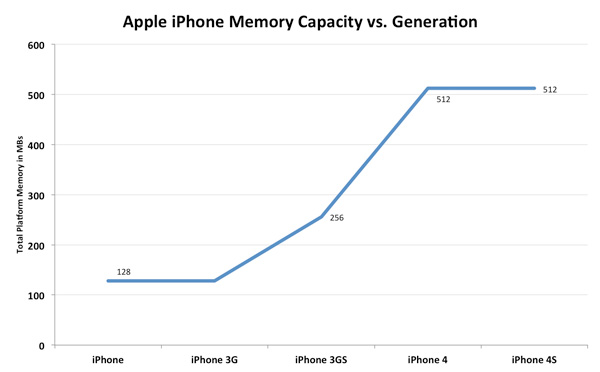

Memory capacity on the other hand has seen more of a step-function growth:

By using a mobile optimized OS Apple has been able to get around large memory requirements. The growth pattern in memory size partially illustrates the lag between introducing faster hardware and developers building truly demanding applications that require that sort of performance. Apple was able to leave the iPhone 4S at 512MB of RAM because the target for many iOS apps is still the iPhone 3GS generation. Don't be surprised to see a move to 1GB in the next iPhone release (we won't see 768MB due to the dual-channel memory requirement) as the app developer target moves to 512MB.

199 Comments

View All Comments

Davabled - Monday, October 31, 2011 - link

With Field test enabled, do numbers closer to zero indicate a better connection? (I'm referring to the numbers that replace the bars in the upper left corner)Anand Lal Shimpi - Monday, October 31, 2011 - link

Correct :)Take care,

Anand

Formul - Monday, October 31, 2011 - link

why the huge drop from iPad 2 to iPhone 4S in the GL benchmark pro? its only about 30% performance .... any explanation?Anand Lal Shimpi - Monday, October 31, 2011 - link

Because the number was incorrect :-P Fixed now :)Take care,

Anand

ZebuluniteX - Monday, October 31, 2011 - link

Great review as always Anand!In addition to the GL benchmark pro results Formul mentioned, I was also surprised to see the Motorola Droid RAZR for some reason do far better than other Gingerbread-based Android smartphones. It is listed as using different version of Android (2.3.5 vs 2.3.4 or older), but given that very similar results were shown between the iPhone 4S and Honeycomb-running Galaxy Tab 8.9 in your 'iPhone 4S Preliminary Benchmarks' article (where the 4S was a bit slower than the Galaxy Tab in SunSpider, and marginally faster in BrowserMark), I'm guess those are just mislabeled Galaxy Tab results. Is that the case?

Anand Lal Shimpi - Monday, October 31, 2011 - link

Thank you - be sure to thank Brian Klug as well, he really did the bulk of the heavy lifting here. I just popped in to talk about silicon and battery life.The RAZR numbers are what we ran at the RAZR announcement: http://www.anandtech.com/show/4981/motorola-droid-...

The improvement is likely due to an updated browser from Motorola. I included those numbers effectively as a placeholder until Ice Cream Sandwich arrives :)

Take care,

Anand

ZebuluniteX - Tuesday, November 1, 2011 - link

Ah, thanks for the clarification, I missed that article. Hmm, that's interesting that, apparently, Motorola "ported" Honeycomb or Ice Cream Sandwich's browser optimizations to Gingerbread (or at least I assume that's what happened)...I'm in the market for a smartphone, and while I was leaning towards the 4S since I already am in the Apple ecosystem via an iPod Touch 2G, before pulling the trigger I wanted to read the Anandtech take on it. The review was excellent as always - thanks again to both you and Brian!

Formul - Monday, October 31, 2011 - link

that was fast! i knew something was not right as there was no mention of this in the text :-)thanks for another great review, keep up the good work! :-)

zanon - Monday, October 31, 2011 - link

The article wrote "The expectation that Apple will always deliver more than just a hardware upgrade is likely what made Siri a 4S exclusive."While only time will tell for sure, it seems quite possible that graduated ramp up had a bigger role to play here. As you say, most of the heavy duty lifting for Siri is going on server-side, and in turn local processing needs aren't too bad. However, the natural flip side of that of course is that the server-side infrastructure is required for the service to work at all, and resources aren't unlimited there either. Even with it limited purely to 4S users, Siri still had some availability problems in the first few days as millions activated and tried to user it simultaneously. It's not hard to imagine what would have happened if every single one of the tens of millions able to upgrade to iOS 5 *also* tried to start using it immediately. Apple has built a huge data center and that's all well and good, but nothing substitutes for actual working experience when it comes to massive software services.

By limiting the initial rollout, Apple can do performance profiling, get an idea of average loads after initial "let's try it" dies down, and so forth. Staggering a rollout also means being able to plan for the general load rather then suffering the classic and well known double-bind of

A) Building for a peak load, and ending up being left with a lot of extraneous hardware that barely gets used.

B) Building for the average, then suffering from embarrassing and headline generating outages for a week or two.

It's true they could just decide to keep it 4S only, but given they are still selling the iPhone 4, and probably make plenty of profit on that now very mature device, I think there is a decent chance they'll roll it out to a wider audience down the road.

Also, a few typos:

Page 2:

I think the phrase is "pretty much par for the *course* for Apple..." rather then "par for the case".

Pg 9, WiFi:

"...newest WLAN, Bluetooth, and FM *cobo* chip" should I think be "combo".

Pg 15:

...4S, without a (big blank, presumably some sentence was supposed to go here?)

Pg 16:

"aren't simply *academical*" should be "academic".

Again, great review, thank you.

Anand Lal Shimpi - Monday, October 31, 2011 - link

That's a very good point, I will add it to the discussion. The sinister view is to assume Apple did it to differentiate, the balanced view takes into account infrastructure, which is exactly what you did here :)And thanks for the corrections :)