ASUS P5E3 Deluxe Overclocking: DDR3 Takes Front Stage

by Kris Boughton on November 20, 2007 4:00 AM EST- Posted in

- CPUs

BIOS Setup and Tweaking, Continued

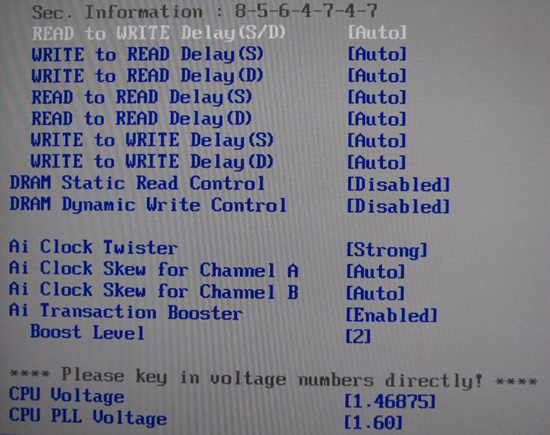

DRAM Static Read Control: Auto, Enabled, and Disabled. We were unable to affect any measurable performance change because of toggling this setting. This setting is curious by its very nature as Ai Transaction Booster (explained below) manipulates the MCH Static Read Control Delay setting directly, implying there would be no reason for this option.

DRAM Dynamic Write Control: Auto, Enabled, and Disabled. See above.

Ai Clock Twister: Auto, Light, Moderate, and Strong. This setting controls the number of memory access phases that are "pulled-in" to the next lower (higher performance) Static Read Delay value. In essence, this allows for smaller, incremental performance gains if the user is unable to achieve stability when using the next lower Static Read Delay value.

Ai Clock Skew for Channel A/B: This setting allows you to either advance or delay the signal timings for Channel A or Channel B DIMMs. Because it's not possible to locate all memory modules an equal distance from the MCH, it's important to be able to adjust signal timing to ensure all data (or requests for data) arrive at the same point at precisely the same time. When experimenting with this setting either slightly delay Channel A (since it's closer to the MCH) or advance Channel B - do not change both simultaneously unless you find you need more than 350ps (picoseconds) of total skew (highly unlikely).

Ai Transaction Booster: Auto, Enabled (Boost: 1-8), and Disabled (Relax: 1-8). This is probably one of the most important BIOS settings when it comes to extracting every possible bit of performance from the system. Setting these fields can improve total memory bandwidth up to 15% and produce a considerable reduction in access latency.

Static Read Control Delay, sometimes referred to as Performance Level, is a primary MCH "timing" value and has a rather significant impact on memory read performance as well as overall memory access latency. In case you are wondering why low access latency matters, we submit to you the following quick-and-dirty response: improved memory latency (courtesy of the Integrated Memory Controller/IMC) is the primary reason that AMD Athlon 64 chips have performed so well. Latency is one of the few areas where AMD maintains a lead over Intel, and Intel will move to an IMC design late next year (starting with Nehalem).

Much like primary memory timings, this MCH "timing" is measured in clock cycles and is relative to the base transmission frequency (2 x FSB). This explains why Static Read Control Delay should increase as FSB rates rise. Similar to memory timings, maintaining a lower value longer with the proper application of MCH voltage can lead to improved performance. In other words, "boosting" the Ai Transaction level may require a higher MCH voltage than would be otherwise required if a more relaxed level were set.

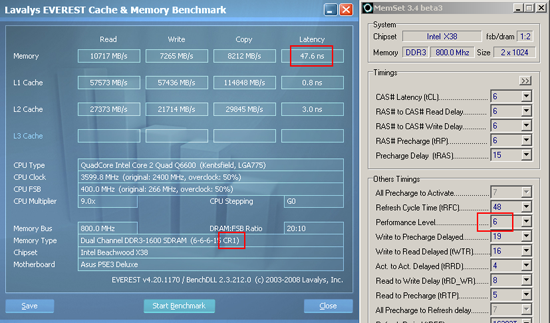

Because these settings effectively apply an offset to the default value it can sometimes be difficult to confirm exactly what is going on - it is almost like flying blind. Thankfully, a wonderful tool exists that reads and reports "Performance Level" from within Windows, allowing us to verify that the board is operating as intended. Memset 3.4 (beta 3), available as freeware, can be found through a simple search using your favorite search engine. Here we see Performance Level, as reported by Memset 3.4, as well as Command Rate and memory latency from EVEREST 4.20.

Auto allows the BIOS to set the values automatically which, through simple experimentation and observation, has been simplified to the following relationship: Static Read Control Delay (default) = tCL. Knowing this makes adjusting the value rather simple. Keep in mind that workable values are in the range of 1-3 (boost or relax) only; selecting values from 4 through 8 will always result in a POST failure.

For example, with memory set to DDR-1600 6-6-6-15, the BIOS will establish a default Static Read Control Delay of 6. Setting Ai Transaction Booster to Enabled with a Boost Level of 1 results in a final Static Read Control Delay setting of 6 - 1 = 5. Alternatively, selecting Disabled with a Relax Level of 1 results in a final value of 6 + 1 = 7. Just like in the case of memory timings, lower is tighter (higher performance).

Finally, a simple rule to keep in mind when setting Static Read Control Delay - 4 requires a CAS Latency (tCL) of 6 or lower, 5 requires a tCL of 7 or lower, and 6 requires a tCL of 8 or lower. There are no other known limitations at this time.

CPU Voltage: Maximum of 1.7000V. Our experience with the ASUS P5E3 Deluxe has shown a rather large voltage offset when it comes to VCore. For example, setting 1.4675V in the BIOS results in an in-Windows idle voltage of ~1.4250V by DMM. Under load we see the voltage settle out as low as 1.39V. While we understand the need and requirement for VDroop, a total difference in programmed BIOS voltage to full-load voltage of more than 0.07V is excessive. Keep this in mind when setting this value if you already know the minimum voltage your CPU needs for stable operation or utilize the load-line calibration setting listed below to reduce VDroop.

CPU PLL Voltage: Maximum of 2.78V. Out of all the voltages the user can manipulate this one is by far the most dangerous. Maximum vCPUpll, as established by Intel, is 1.60V (default for this board) making 2.78V a whopping ~75% over specification! (As an aside, this would be the equivalent of subjecting your 65nm CPU to a core voltage of over 2.5V). Exercise extreme caution when utilizing higher values as setting this value too high can result in the CPUs "losing cores" after being subjected to voltage in excess of ~2.0V. The good news is that we did not see an increase in overclocking potential with voltages above 1.68V.

DRAM Static Read Control: Auto, Enabled, and Disabled. We were unable to affect any measurable performance change because of toggling this setting. This setting is curious by its very nature as Ai Transaction Booster (explained below) manipulates the MCH Static Read Control Delay setting directly, implying there would be no reason for this option.

DRAM Dynamic Write Control: Auto, Enabled, and Disabled. See above.

Ai Clock Twister: Auto, Light, Moderate, and Strong. This setting controls the number of memory access phases that are "pulled-in" to the next lower (higher performance) Static Read Delay value. In essence, this allows for smaller, incremental performance gains if the user is unable to achieve stability when using the next lower Static Read Delay value.

Ai Clock Skew for Channel A/B: This setting allows you to either advance or delay the signal timings for Channel A or Channel B DIMMs. Because it's not possible to locate all memory modules an equal distance from the MCH, it's important to be able to adjust signal timing to ensure all data (or requests for data) arrive at the same point at precisely the same time. When experimenting with this setting either slightly delay Channel A (since it's closer to the MCH) or advance Channel B - do not change both simultaneously unless you find you need more than 350ps (picoseconds) of total skew (highly unlikely).

Ai Transaction Booster: Auto, Enabled (Boost: 1-8), and Disabled (Relax: 1-8). This is probably one of the most important BIOS settings when it comes to extracting every possible bit of performance from the system. Setting these fields can improve total memory bandwidth up to 15% and produce a considerable reduction in access latency.

Static Read Control Delay, sometimes referred to as Performance Level, is a primary MCH "timing" value and has a rather significant impact on memory read performance as well as overall memory access latency. In case you are wondering why low access latency matters, we submit to you the following quick-and-dirty response: improved memory latency (courtesy of the Integrated Memory Controller/IMC) is the primary reason that AMD Athlon 64 chips have performed so well. Latency is one of the few areas where AMD maintains a lead over Intel, and Intel will move to an IMC design late next year (starting with Nehalem).

Much like primary memory timings, this MCH "timing" is measured in clock cycles and is relative to the base transmission frequency (2 x FSB). This explains why Static Read Control Delay should increase as FSB rates rise. Similar to memory timings, maintaining a lower value longer with the proper application of MCH voltage can lead to improved performance. In other words, "boosting" the Ai Transaction level may require a higher MCH voltage than would be otherwise required if a more relaxed level were set.

Because these settings effectively apply an offset to the default value it can sometimes be difficult to confirm exactly what is going on - it is almost like flying blind. Thankfully, a wonderful tool exists that reads and reports "Performance Level" from within Windows, allowing us to verify that the board is operating as intended. Memset 3.4 (beta 3), available as freeware, can be found through a simple search using your favorite search engine. Here we see Performance Level, as reported by Memset 3.4, as well as Command Rate and memory latency from EVEREST 4.20.

|

Auto allows the BIOS to set the values automatically which, through simple experimentation and observation, has been simplified to the following relationship: Static Read Control Delay (default) = tCL. Knowing this makes adjusting the value rather simple. Keep in mind that workable values are in the range of 1-3 (boost or relax) only; selecting values from 4 through 8 will always result in a POST failure.

For example, with memory set to DDR-1600 6-6-6-15, the BIOS will establish a default Static Read Control Delay of 6. Setting Ai Transaction Booster to Enabled with a Boost Level of 1 results in a final Static Read Control Delay setting of 6 - 1 = 5. Alternatively, selecting Disabled with a Relax Level of 1 results in a final value of 6 + 1 = 7. Just like in the case of memory timings, lower is tighter (higher performance).

Finally, a simple rule to keep in mind when setting Static Read Control Delay - 4 requires a CAS Latency (tCL) of 6 or lower, 5 requires a tCL of 7 or lower, and 6 requires a tCL of 8 or lower. There are no other known limitations at this time.

CPU Voltage: Maximum of 1.7000V. Our experience with the ASUS P5E3 Deluxe has shown a rather large voltage offset when it comes to VCore. For example, setting 1.4675V in the BIOS results in an in-Windows idle voltage of ~1.4250V by DMM. Under load we see the voltage settle out as low as 1.39V. While we understand the need and requirement for VDroop, a total difference in programmed BIOS voltage to full-load voltage of more than 0.07V is excessive. Keep this in mind when setting this value if you already know the minimum voltage your CPU needs for stable operation or utilize the load-line calibration setting listed below to reduce VDroop.

CPU PLL Voltage: Maximum of 2.78V. Out of all the voltages the user can manipulate this one is by far the most dangerous. Maximum vCPUpll, as established by Intel, is 1.60V (default for this board) making 2.78V a whopping ~75% over specification! (As an aside, this would be the equivalent of subjecting your 65nm CPU to a core voltage of over 2.5V). Exercise extreme caution when utilizing higher values as setting this value too high can result in the CPUs "losing cores" after being subjected to voltage in excess of ~2.0V. The good news is that we did not see an increase in overclocking potential with voltages above 1.68V.

25 Comments

View All Comments

Owls - Tuesday, November 20, 2007 - link

DDR2 is hardly "inferior". When comparing 4GB of DDR3 vs 4GB of DDR2, I can build a whole new computer with what I'd have spent on DDR3. It just doesn't make sense right now no matter how you cut it.. and only having 1GB of ram now?TA152H - Tuesday, November 20, 2007 - link

I run most of my machines with 512 MB, so 1 GB is hardly a problem.There are some things you need more memory than 1 GB for.

When I see stuff like "It doesn't make sense no matter how you cut it", I instantly think you're an idiot. You're probably not, but that statement is absurd. There is always a group that the cost of the most expensive, and fastest parts, makes sense. The cost of memory is trivial compared to the cost of salaries, for example, and spending $500 to help someone work faster pays for itself very quickly.

I think the main problem is that most people do not understand that more memory does not always make things faster. I deal with this all the time.

AnnihilatorX - Tuesday, November 20, 2007 - link

Correct me if I am wrongThe increase in FPS you see going from 400x9 to 465x9 is nearly 100% due to increase in CPU frequency

The performance increase of a 465x9 RAM running at 2:1 memory divider would be less than 5% higher than a similar configuration of 465x9 with slower RAM running at lower divider ratios.

That would mean there is no sense to buy a premium DDR3 for $500 extra for what you can do with less than 5% performance sacrifice with the dirt cheap DDR2 RAM.

snarfbot - Sunday, November 25, 2007 - link

no everything you said is correct.the thing that really gets me though, is that pc6400 ddr2 is commonly capable of reaching 485mhz at lower timings. so whats so great about ddr3?

on a p35 you can easily reach the same speed with cheap memory, at cas 5, sometimes even cas 4 with good overclockable ram.

so basically the only benefit that ddr3 has going for it is the lower voltage required, and of course lower temps, not worth the premium. period.

Aivas47a - Tuesday, November 20, 2007 - link

This is one of the best, detailed overclocking guides I've ever seen. Excellent job! I'm especially glad to have the mystery of Transaction Booster, Skew, and Clock Twister in the Asus bios explained.Now, if you guys could just prepare a guide for memory subtimings, the treatise would be complete. :)

Thanks very much for this.