Fusion

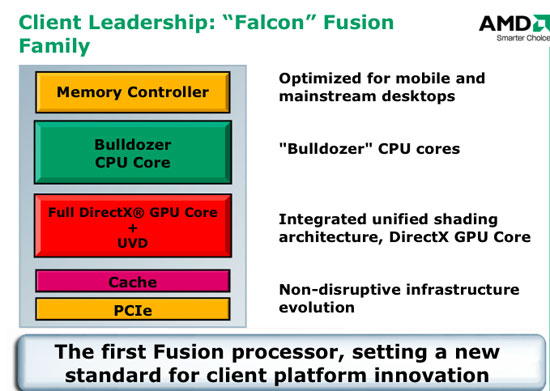

Remember Fusion? The whole reason for the ATI acquisition? Well, AMD gave us a little more information on its plans for the first Fusion CPUs.The first Fusion CPUs belong to a family of chips codenamed Falcon; note that Falcon refers to the Fusion CPU family and not the CPU or GPU cores themselves. Contrary to popular belief, the first Fusion CPUs will be built of a single die. On this die you will find the following components: a shared memory controller, Bulldozer or Bobcat based CPU cores, a DirectX GPU core with UVD support, a shared cache (shared between the CPU and GPU), and a PCIe controller - all on the same die.

For a one-die solution, the feature list for Falcon is pretty impressive. Let's discuss what we know:

The shared memory controller will most likely support DDR3 given the 2009 - 2010 launch timeframe for Fusion, and obviously it will be used by both the CPU and GPU portions of the die. We've already discussed the Bulldozer and Bobcat cores; you can expect the desktop/notebook Falcon chips to use Bulldozer cores while the smallest Ultra Mobile PCs, high performance smart phones and CE devices to use Bobcat based Falcon processors.

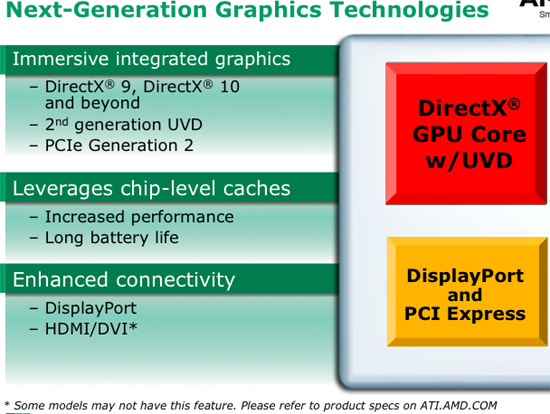

AMD just lists the graphics core as being a "Full DirectX GPU", but fails to attach any DX revision to the support sheet. AMD did mention that the GPU core would be a unified shader architecture, but we suspect that lower end Falcon CPUs may not support everything required by DX9/DX10.

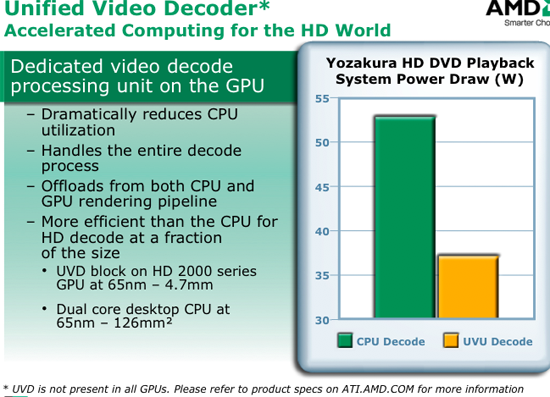

The integrated UVD support will eliminate the need for an external graphics card just to decode high bitrate H.264 video. UVD only ends up being around 4.7 mm^2 of today's 65nm GPU die yet it is several orders of magnitude more efficient than the x86 CPU core at decoding H.264, highlighting the importance of its integration onto the CPU die itself. Given how powerful and efficient UVD is, we can't help but wonder how long it will take for AMD to include it in all of its CPUs. We may have to wait for a unified instruction set between the CPU/GPU before we get that sort of granular integration though.

The last item on the M-Space stack is the on-die PCIe 2.0 controller, which AMD said would support a minimum of 16 lanes externally. With an integrated PCIe controller, the only other chip needed is an external South Bridge that can connect via PCIe to the CPU itself.

The on-die PCIe controller won't kill the add-in GPU market, as you will be able to simply pop in an external graphics card if necessary. You can then either disable the on-die graphics or switch between the two as your usage demands change. In notebooks, AMD expects systems with discrete graphics to swap between it and the on-die GPU on the fly depending on usage.

31 Comments

View All Comments

Imaginer - Thursday, July 26, 2007 - link

It better be as good as "The Empire Strikes Back"! :D