Fusion

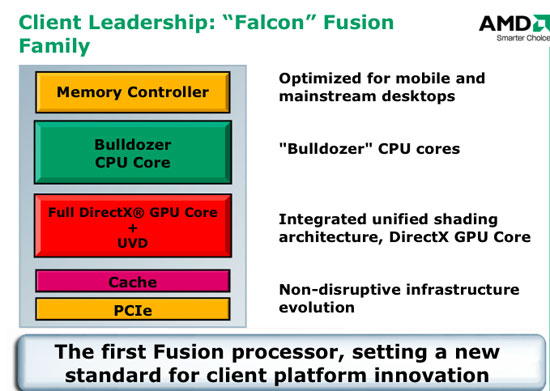

Remember Fusion? The whole reason for the ATI acquisition? Well, AMD gave us a little more information on its plans for the first Fusion CPUs.The first Fusion CPUs belong to a family of chips codenamed Falcon; note that Falcon refers to the Fusion CPU family and not the CPU or GPU cores themselves. Contrary to popular belief, the first Fusion CPUs will be built of a single die. On this die you will find the following components: a shared memory controller, Bulldozer or Bobcat based CPU cores, a DirectX GPU core with UVD support, a shared cache (shared between the CPU and GPU), and a PCIe controller - all on the same die.

For a one-die solution, the feature list for Falcon is pretty impressive. Let's discuss what we know:

The shared memory controller will most likely support DDR3 given the 2009 - 2010 launch timeframe for Fusion, and obviously it will be used by both the CPU and GPU portions of the die. We've already discussed the Bulldozer and Bobcat cores; you can expect the desktop/notebook Falcon chips to use Bulldozer cores while the smallest Ultra Mobile PCs, high performance smart phones and CE devices to use Bobcat based Falcon processors.

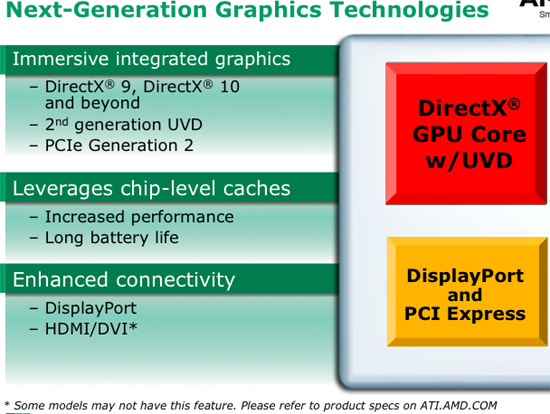

AMD just lists the graphics core as being a "Full DirectX GPU", but fails to attach any DX revision to the support sheet. AMD did mention that the GPU core would be a unified shader architecture, but we suspect that lower end Falcon CPUs may not support everything required by DX9/DX10.

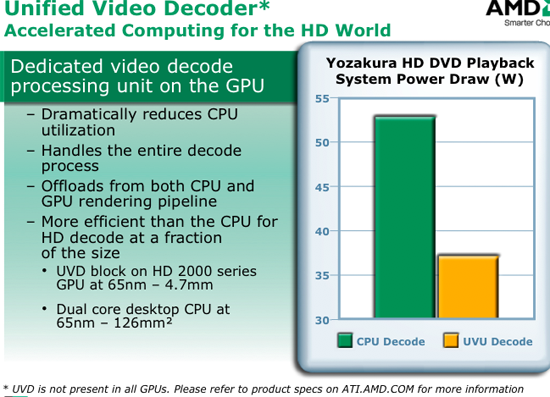

The integrated UVD support will eliminate the need for an external graphics card just to decode high bitrate H.264 video. UVD only ends up being around 4.7 mm^2 of today's 65nm GPU die yet it is several orders of magnitude more efficient than the x86 CPU core at decoding H.264, highlighting the importance of its integration onto the CPU die itself. Given how powerful and efficient UVD is, we can't help but wonder how long it will take for AMD to include it in all of its CPUs. We may have to wait for a unified instruction set between the CPU/GPU before we get that sort of granular integration though.

The last item on the M-Space stack is the on-die PCIe 2.0 controller, which AMD said would support a minimum of 16 lanes externally. With an integrated PCIe controller, the only other chip needed is an external South Bridge that can connect via PCIe to the CPU itself.

The on-die PCIe controller won't kill the add-in GPU market, as you will be able to simply pop in an external graphics card if necessary. You can then either disable the on-die graphics or switch between the two as your usage demands change. In notebooks, AMD expects systems with discrete graphics to swap between it and the on-die GPU on the fly depending on usage.

31 Comments

View All Comments

kilkennycat - Friday, July 27, 2007 - link

Highly likely that nVidia will solve this problem at both high and low end with their next family of GPUs. Stay tuned for the end of 2007. The first part out of the chute is also likely not to be the highest end but that which replaces the 8800GTS at a price close to $200 with full HD hardware decode... nVidia is very well aware of the cost-performance hole left by both AMD/ATI and themselves in their current GPU line.strikeback03 - Friday, July 27, 2007 - link

with that Phenom demo box, I think they have finally found use for a 1000W+ power supplySpoelie - Friday, July 27, 2007 - link

Given the size of the heatsink on the cpu, I'd venture power consumption is inline with other engineering samples, 120w or less max TDPSpoelie - Friday, July 27, 2007 - link

Oh my bad, you're right when taking the three 2900XTs in consideration.Where's my edit button :(

Spoelie - Friday, July 27, 2007 - link

At least 2 times in the article, the text builds up anticipation for a graph, but it never comes, the most telling example is on page 6, but one or two pages before it it happened also. Both graphs are supposed to be from Intel.Justin Case - Monday, August 13, 2007 - link

Exactly. They say "Two years ago Intel used the following chart to illustrate the need for multi-core CPUs", and then the image is an AMD slide, not an Intel graph.Omega215D - Thursday, July 26, 2007 - link

If they plan to integrate an on die PCIe controller on the CPU how would this affect overclocking?Regs - Friday, July 27, 2007 - link

I'd imagine just like how it was when AMD intergrated the memory controller, mobo makers will just have to add more bios options.yacoub - Thursday, July 26, 2007 - link

While paging through the article, the thing that stood out most to me was the AMD graphic on page 5 supposedly demonstrating how much more performance Bulldozer is going to offer without a single number on the graph. I guess they want us to measure its performance increases in pixels. hehe :)LTG - Thursday, July 26, 2007 - link

Anand you're really good at distilling out the bottom line from massive amounts of marketing talk and slide ware.