Understanding the Cell Microprocessor

by Anand Lal Shimpi on March 17, 2005 12:05 AM EST- Posted in

- CPUs

Cell’s Dynamic Logic

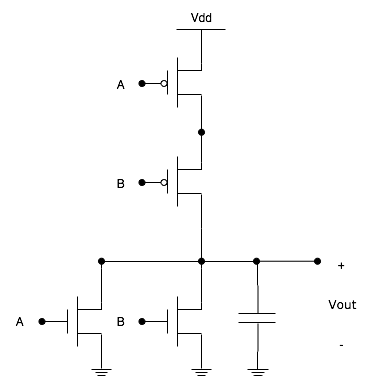

Although it’s beyond the scope of this article, one of the major problems with static CMOS circuits are the p-type transistors, and the fact that for every n-type transistor, you also must use a p-type transistor.There is an alternative known as dynamic or pseudo-NMOS logic, which gets around the problems of static CMOS while achieving the same functionality. Let’s take a look at that static CMOS NOR gate again:

Thus, the NOR gate outputs a 1 only if all inputs are 0, which is exactly how a NOR gate should function.

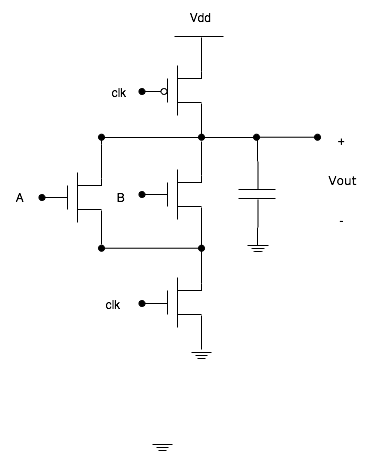

Now, let’s take a look at a pseudo-NMOS implementation of the same NOR gate:

Cell’s implementation goes one step further. The p-type transistor at the top of the circuit and the n-type transistor at the bottom are clocked on non-overlapping phases, meaning that the two clocks aren’t high/low at the same time.

The way in which the gate here works is as follows: inputs are first applied to the logic in between the clock fed transistors. The top transistor’s gate is closed allowing the logic transistors to charge up. The gate is then opened and the lower transistor’s gate is closed to drain the logic transistors to ground. The charge that remains is the output of the circuit.

What’s important about this is that since power is only consumed during two non-overlapping phases, overall power consumption is lower than static CMOS. The downside is that clock signal routing becomes much more difficult.

The other benefit is lower transistor count. In the example of the 2-input NOR gate, our static CMOS design used 4 transistors, while our pseudo-NMOS implementation used 4 transistors as well. But for a 3-input NOR gate, the static CMOS implementation requires 6 transistors, while the pseudo-NMOS implementation requires 5. The reasoning is that for a CMOS circuit, you have 1 p-type transistor for every n-type, while in a pseudo-NMOS circuit you only have two additional transistors beyond the bare minimum required to implement the logic function. For a 100-input NOR gate (unrealistic, but a good example), a static CMOS implementation would require 200 transistors, while a pseudo-NMOS implementation would only require 102.

By making more efficient use of transistors and lowering power consumption, Cell’s pseudo-NMOS logic design enables higher clock frequencies. The added cost is in the manufacturing and design stages:

- As we mentioned before, clock routing becomes increasingly difficult with pseudo-NMOS designs similar to that used in Cell. The clock trees required for Cell are probably fairly complex, but given IBM’s expertise in the field, it’s not an insurmountable problem.

- Designing pseudo-NMOS logic isn’t easy, and there are no widely available libraries from which to pull circuit designs. Once again, given IBM’s size and expertise, this isn’t much of an issue, but it does act as a barrier for entry of smaller chip manufacturers.

- Manufacturing such high speed dynamic logic circuits often requires techniques like SOI, but once again, not a problem for IBM given that they have been working on SOI for quite some time now. There’s no surprise that Cell is manufactured on a 90nm SOI process.

70 Comments

View All Comments

WishIKnewComputers - Thursday, March 17, 2005 - link

Well, I dont really see the Cell 'breaking' in any way. Between being in the PS3, IBM servers/supercomputers, and Sony and Toshiba electronics, the chip will be all over the place.As for it showing up in PCs... no it wont happen anytime soon, but I really dont think it's intended to at this point. Workstation and playstations are its main concern, and smartly so. The Cell in its first generation isnt cut out for superior general tasking, obviously, but when those things start pumping out (and they will... the PS2 has sold what, 80 million units?), there will likely be different and more advanced versions. And if some of those are changed for enhanced general purposing somehow or another, then they could have shot at entering the PC world. As for taking on Intel, though... I dont think IBM is even considering that. If I had to guess, if they wanted to be in a PC, they would have OS X adapted to Cell and IBM would have these things in Apples.

But no matter which way they go, is it me or does IBM seem light-years ahead of Intel? After looking at Intel's future plans, it seems that they are trying to move towards what IBM is doing now. So is the Cell a processor just ahead of its time, or has Intel just gotten behind?

AnnihilatorX - Thursday, March 17, 2005 - link

This article is seriously a kill for a child like me. I appreciate it though. Well done Anandtechravedave - Thursday, March 17, 2005 - link

I can't wait to see what devlopers thing of the cell & the SDK's for it. I have a feeling thats what will kill the cell or make it successfull.microbrew - Thursday, March 17, 2005 - link

"System on a Chip (SoC)"What will make or break the Cell is the tools available, especially the operating system and libraries.

I would like to see what they're doing in terms of marketing the chip to consumer electronics, telecom, military and other embedded applications. I could see the Cell as a viable alternative to the usual mixures of PowerPcs, ARMs and DSPs.

I also agree with Final Words; I don't see the Cell breaking into the consumer PC market any time soon either.

Locut0s - Thursday, March 17, 2005 - link

#17 Yeah that was a bit too harsh I agree.Eug - Thursday, March 17, 2005 - link

I'm just wondering how well a dual-core PPE-based 4+ GHz chip would do in general purpose (desktop) code.And I also wonder how cool/hot such a chip would be. The Xbox 2's CPU is probably a 3-core PPE, but it runs at 3 GHz, and we don't have power specs for it anyway.

Filibuster - Thursday, March 17, 2005 - link

#11 (well, everyone should if they haven't before) read the Arstechnica article on PS2 vs PC - static applications vs dynamic media. Cell is taking it to the next level.http://arstechnica.com/articles/paedia/cpu/ps2vspc...

Very nice article Anand!

Googer - Thursday, March 17, 2005 - link

Besides a release date, is there any news or knowledge of a Linux Kit for Playstation 3 like there was for PS2? Does anyone KNOW OF Either?Illissius - Thursday, March 17, 2005 - link

Damn. Awesome article. If I hadn't known the site and author beforehand, I would've guessed Ars and Hannibal. Seems he isn't the only one with a talent for these kinds of articles ;)You should do more of them.

scrotemaninov - Thursday, March 17, 2005 - link

#22: This is just a guess so don't rely on this. The POWER5 has 2way SMT. Each cycle it fetches 8 instructions from the L1I cache. All instructions fetched per cycle are for the same thread so it alternates (round robin). It also has capabilities for setting the thread priority so that you effectively run with 1 thread and it just fetches 8 instructions per cycle for the one running thread.I would expect the PPE to be similar to this, fetching 2 instructions for the same thread each cycle. The POWER5 has load balancing stuff in there too - if one thread keeps missing in L2 then the other thread gets more instructions decoded in order to keep the CPU functional unit utilisation up. I've no idea whether this kind of stuff has made it over into the PPE, I'd be a little surprised if it has, especially seeing as this is in-order anyway so it's not like you're going to be aiming for high utilisations rates.