The Ice Lake Benchmark Preview: Inside Intel's 10nm

by Dr. Ian Cutress on August 1, 2019 9:00 AM EST- Posted in

- CPUs

- Intel

- GPUs

- 10nm

- Core

- Ice Lake

- Cannon Lake

- Sunny Cove

- 10th Gen Core

Section by Andrei Frumusanu

SPEC2017 and SPEC2006 Results (15W)

SPEC2017 and SPEC2006 is a series of standardized tests used to probe the overall performance between different systems, different architectures, different microarchitectures, and setups. The code has to be compiled, and then the results can be submitted to an online database for comparsion. It covers a range of integer and floating point workloads, and can be very optimized for each CPU, so it is important to check how the benchmarks are being compiled and run.

We run the tests in a harness built through Windows Subsystem for Linux, developed by our own Andrei Frumusanu. WSL has some odd quirks, with one test not running due to a WSL fixed stack size, but for like-for-like testing is good enough. SPEC2006 is deprecated in favor of 2017, but remains an interesting comparison point in our data. Because our scores aren’t official submissions, as per SPEC guidelines we have to declare them as internal estimates from our part.

For compilers, we use LLVM both for C/C++ and Fortan tests, and for Fortran we’re using the Flang compiler. The rationale of using LLVM over GCC is better cross-platform comparisons to platforms that have only have LLVM support and future articles where we’ll investigate this aspect more. We’re not considering closed-sourced compilers such as MSVC or ICC.

clang version 8.0.0-svn350067-1~exp1+0~20181226174230.701~1.gbp6019f2 (trunk)

clang version 7.0.1 (ssh://git@github.com/flang-compiler/flang-driver.git

24bd54da5c41af04838bbe7b68f830840d47fc03)-Ofast -fomit-frame-pointer

-march=x86-64

-mtune=core-avx2

-mfma -mavx -mavx2

Our compiler flags are straightforward, with basic –Ofast and relevant ISA switches to allow for AVX2 instructions. Despite ICL supporting AVX-512, we have not currently implemented it, as it requires a much greater level of finesse with instruction packing. The best AVX-512 software uses hand-crafted intrinsics to provide the instructions, as per our 3PDM AVX-512 test later in the review.

For these comparisons, we will be picking out CPUs from across our dataset to provide context. Some of these might be higher power processors, it should be noted.

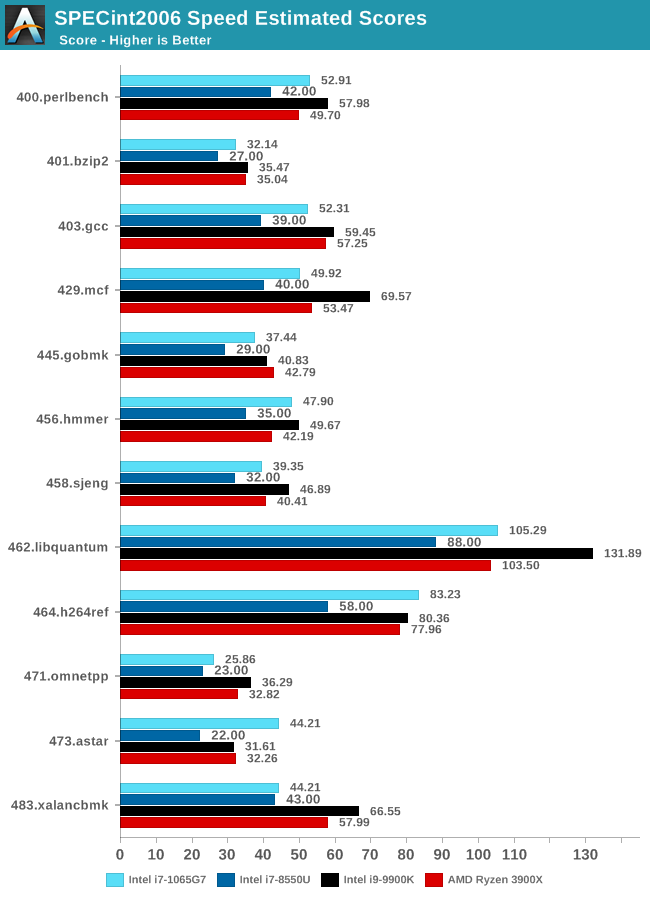

SPECint2006

Amongst SPECint2006, the one benchmark that really stands out beyond all the rest is the 473.astar. Here the new Sunny Cove core is showcasing some exceptional IPC gains, nearly doubling the performance over the 8550U even though it’s clocked 100MHz lower. The benchmark is extremely branch misprediction sensitive, and the only conclusion we can get to rationalise this increase is that the new branch predictors on Sunny Cove are doing an outstanding job and represent a massive improvement over Skylake.

456.hmmer and 464.h264ref are very execution bound and have the highest actual instructions per clock metrics in this suite. Here it’s very possible that Sunny Cove’s vastly increased out-of-order window is able to extract a lot more ILP out of the program and thus gain significant increases in IPC. It’s impressive that the 3.9GHz core here manages to match and outpace the 9900K’s 5GHz Skylake core.

Other benchmarks here which are limited by other µarch characteristics have various increases depending on the workload. Sunny Cove doubled L2 cache should certainly help with workloads like 403.gcc and others. However because we’re also memory latency limited on this platform the increases aren’t quite as large as we’d expect from a desktop variant of ICL.

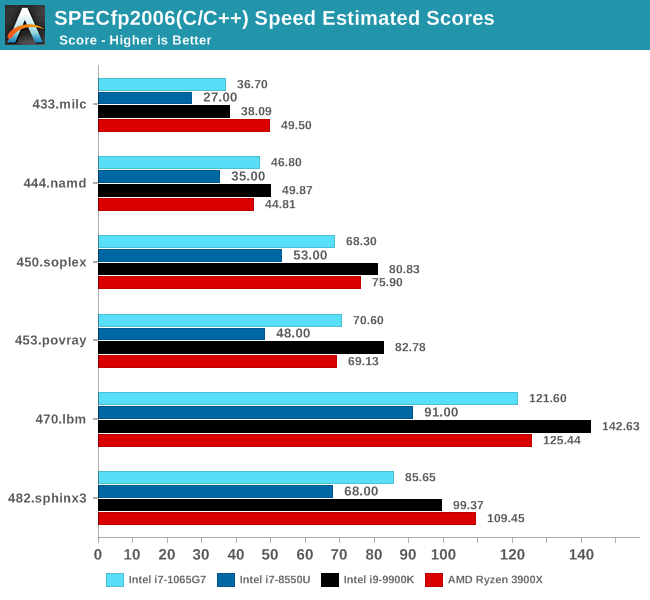

In SPECfp2006, Sunny Cove’s wider out-of-order window can again be seen in tests such as 453.povray as the core is posting some impressive gains over the 8550U at similar clocks. 470.lbm is also instruction window as well as data store heavy – the core’s doubled store bandwidth here certainly helps it.

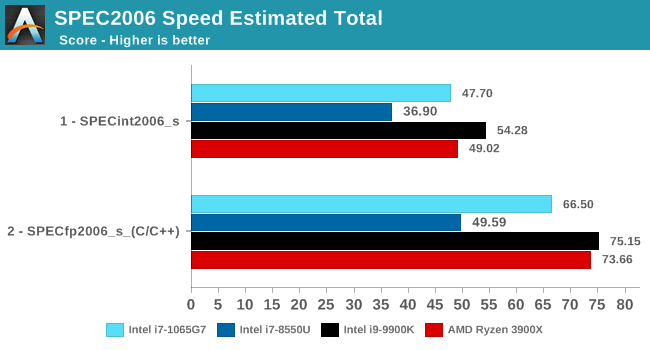

Overall in SPEC2006, the new i7-1065G7 beats a similarly clocked i7-8550U by a hefty 29% in the int suite and 34% in the fp suite. Of course this performance gap will be a lot smaller against 9th gen mobile H-parts at higher clocks, but these are also higher TDP products.

The 1065G7 comes quite close to the fastest desktop parts, however it’s likely it’ll need a desktop memory subsystem in order to catch up in total peak absolute performance.

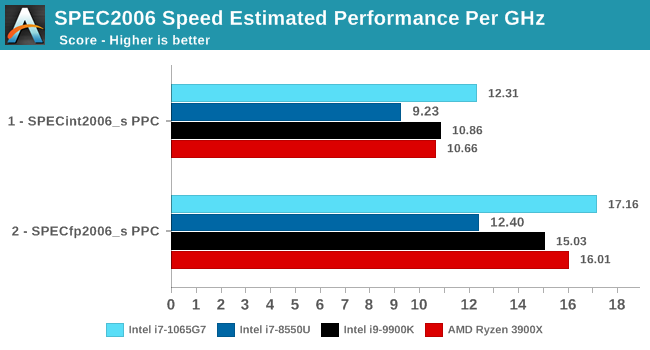

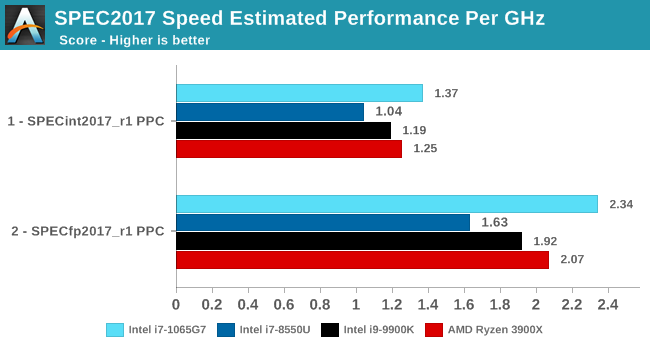

Performance per clock increases on the new Sunny Cove architecture are outstandingly good. IPC increases against the mobile Skylake are 33 and 38% in the integer and fp suites, though we also have to keep in d mind these figures go beyond just the Sunny Cove architecture and also include improvements through the new LPDDR4X memory controllers.

Against a 9900K, although apples and oranges, we’re seeing 13% and 14% IPC increases. These figures likely would be higher on an eventual desktop Sunny Cove part.

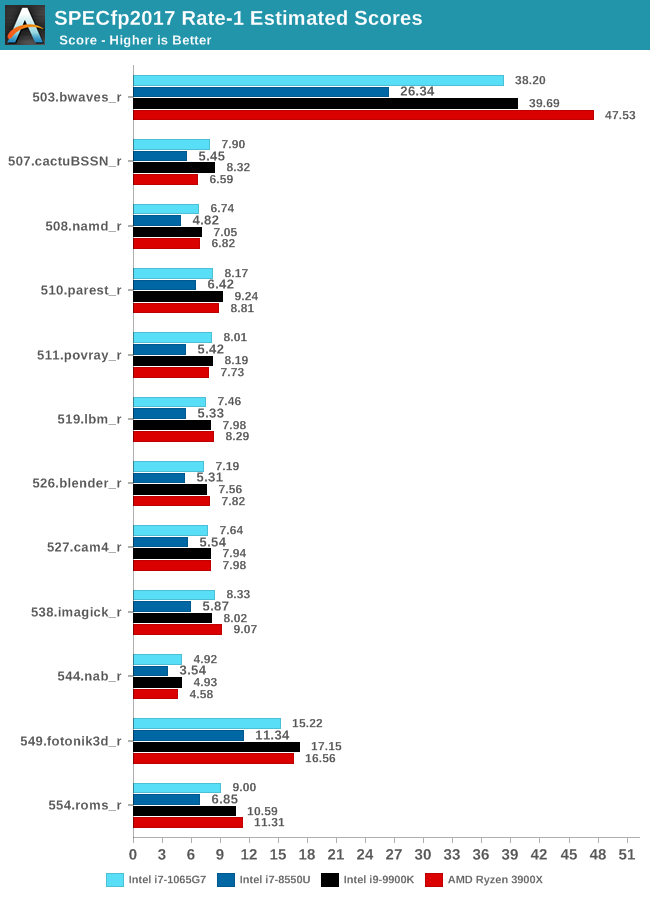

SPEC2017

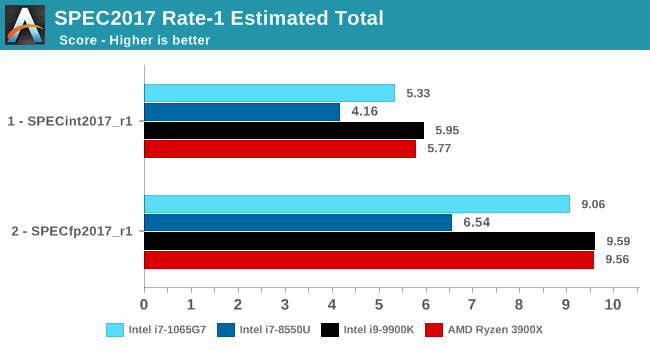

The SPEC2017 results look similar to the 2006 ones. Against the 8550U, we’re seeing grand performance uplifts, just shy of the best desktop processors.

Here the IPC increase also look extremely solid. In the SPECin2017 suite the Ice Lake part achieves a 14% increase over the 9900K, however we also see a very impressive 21% increase in the fp suite.

Overall in the 2017 suite, we’re seeing a 19% increase in IPC over the 9900K, which roughly matches Intel’s advertised metric of 18% IPC increase.

261 Comments

View All Comments

rangerdavid - Friday, August 2, 2019 - link

What Moizy said. Ian, you are quite fair and diplomatic in your responses. And if you are in some kind of Intel marketing conspiracy, for heaven's sake, I hope you are getting a good cut! Buy yourself something pretty, fella... (grin)0ldman79 - Friday, August 2, 2019 - link

Rock on man.Well said.

Sailor23M - Monday, August 5, 2019 - link

+1 Moizy thanks. I really do not have the time to go searching and collecting all the leaks out there, so this article was well timed for me and at a high level lets me know what to expect from these chips.close - Monday, August 5, 2019 - link

@Moizy: I guess props to AT if this turns out to be the real situation.Curious what happens if we have another "oh our puff piece didn't notice they were using a sub 0 chiller under the table" kind of situation. Last time there was an anemic "oh, yeah, Intel could have been more straight forward" type reaction. So you can understand why people are skeptical about results that can't be independently validated, even (especially? ...given past experiences) if they come from AT.

tijag - Thursday, August 1, 2019 - link

You sir are a first rate obtuse troll.chowmanga - Thursday, August 1, 2019 - link

Would you say there was a difference between getting a product in advance and getting one when the rest of the press gets one?Moizy - Thursday, August 1, 2019 - link

To me, the only meaningful difference is timing. The unsound logic of the argument is a) Intel invites a few select press to a preview event months before availability, b) the select few press are flattered by the privilege and develop positively biased feelings toward Intel, therefore c) they report positively biased, flawed findings due to the privilege.It's true that inviting a select few to the event could psychologically influence those few, making them slightly less objective than they may have otherwise been. But Ian's reporting isn't built on subjective opinions on Icy Lake, 10nm, and Intel. His reporting is built on his objective testing, using his standardized benchmarks. So even if Ian's view of Intel and Icy Lake were a little swayed by this privilege (which I doubt they were, he's not a new kid on the block, he deals with PR and Marketing and the like all the time), for this to translate into flawed, biased reporting, Ian would need to purposefully alter his standardized benchmarks in order to produced positively biased results. There is zero evidence that he did that here, and there is zero precedence to him doing that in the past, so the original logic is extremely flawed.

uberDoward - Friday, August 2, 2019 - link

Based on the fact (as Ian mentioned at the beginning of the article) it DOES sound like others that were invited came unprepared, and willing to just spout Intel's rhetoric without objective measurements. Kudos to Ian for arriving prepared!Santoval - Friday, August 2, 2019 - link

You are ranting but saying nothing substantial or even anything that makes sense. "Conflict of interest"? Really? In what way exactly, do you think they gifted Ian and the other AnandTech editors a few hundreds of Intel shares each? Maybe they gave them free vacations to Bali just to "thank" them? Or free top-end Intel based laptops and Intel SSDs for the next 5 years?These examples *would* be conflicts of interest. Previewing an Ice Lake reference design while pointing out an entire list of caveats and limitations is not an example of a conflict of interest. "Professional distance" does not mean declining a product preview (why on Earth should they?), it means keeping an equal distance from all the companies the products of which you preview.

bcronce - Friday, August 2, 2019 - link

I learned a lot. Like trade-offs between latency and throughput in several different ways. Or increase in cache-hits vs latency.