AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTDeciphering the New Cache Hierarchy

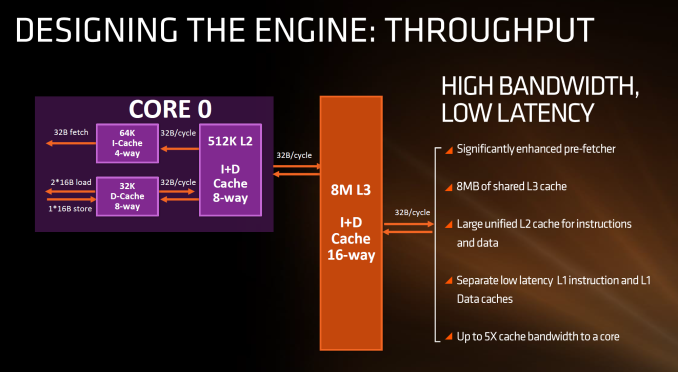

The cache hierarchy is a significant deviation from recent previous AMD designs, and most likely to its advantage. The L1 data cache is both double in size and increased in associativity compared to Bulldozer, as well as being write-back rather than write-through. It also uses an asymmetric load/store implementation, identifying that loads happen more often than stores in the critical paths of most work flows. The instruction cache is no longer shared between two cores as well as doubling in associativity, which should decrease the proportion of cache misses. AMD states that both the L1-D and L1-I are low latency, with details to come.

The L2 cache sits at half a megabyte per core with 8-way associativity, which is double that of Intel’s Skylake which has 256 KB/core and is only 4-way. On the other hand, Intel’s L3/LLC on their high-end Skylake SKUs is at 2 MB/core or 8 MB/CPU, whereas Zen will feature 1 MB/core and both are at 16-way associativity.

Edit 7:18am: Actually, the slide above is being slightly evasive in its description. It doesn't say how many cores the L3 cache is stretched over, or if there is a common LLC between all cores in the chip. However, we have recieved information from a source (which can't be confirmed via public AMD documents) that states that Zen will feature two sets of 8MB L3 cache between two groups of four cores each, giving 16 MB of L3 total. This would means 2 MB/core, but it also implies that there is no last-level unified cache in silicon across all cores, which Intel has. The reasons behind something like this is typically to do with modularity, and being able to scale a core design from low core counts to high core counts. But it would still leave a Zen core with the same L3 cache per core as Intel.

| Cache Levels | ||||

| Bulldozer FX-8150 |

Zen | Broadwell-E i7-6950X |

Skylake i7-6700K |

|

| L1 Instruction | 64 KB 2-way per module |

64 KB 4-way | 32 KB 8-way | 32 KB 8-way |

| L1 Data | 16 KB 4-way Write Through |

32 KB 8-way Write Back |

32 KB 8-way Write-Back |

32 KB 8-way Write-Back |

| L2 | 2 MB 16-way per module |

512 KB 8-way | 256 KB 8-way | 256 KB 4-way |

| L3 | 1 MB/core 64-way |

1 or 2 MB/core ? 16-way |

2.5 MB/core 16/20-way |

2 MB/core 16-way |

What this means, between the L2 and the L3, is that AMD is putting more lower level cache nearer the core than Intel, and as it is low level it becomes separate to each core which can potentially improve single thread performance. The downside of bigger and lower (but separate) caches is how each of the cores will perform snoop in each other’s large caches to ensure clean data is being passed around and that old data in L3 is not out-of-date. AMD’s big headline number overall is that Zen will offer up to 5x cache bandwidth to a core over previous designs.

216 Comments

View All Comments

FMinus - Thursday, August 18, 2016 - link

He's right tho. AMD was a licensee of Intel to produce bulk Intel products, because intel couldn't keep up with the demand. Then AMD reverse engineered Intels products and brought their own line out and Intel didn't like that, thus they broke the agreement, which in the end didn't help much since AMD had already all they needed.That being said, what AMD did anyone would, so it's just business as per usual. Then they actually stepped up and made great own CPUs to combat intel and made a great dual core and AMD64. AMD did a lot for computing, but the early days were pretty much a contractor and pirate.

I wish them all the best with Zen and future, and I hope they get Vega right, by that I mean don't fucking gimp the chip by power delivery, cause you can't get that under control, everyone knows nvidia is ahead in that game, just give a great performing GPU on the market and let it eat 250W if need be.

Nagorak - Thursday, August 18, 2016 - link

Yeah, they matched Intel on the CPU front, and Intel responded by abusing their stronger market position to limit AMD's gains. I'll be happy to get an AMD processor back in my machine just based on principle.Klimax - Saturday, August 20, 2016 - link

Correction: IBM forced Intel to license number of CPU manufactures. (At least two suppliers, similar to rule sued by militaries) And there was lawsuit or two. Fun stuff.looncraz - Thursday, August 18, 2016 - link

Maybe you are too young to remember, but AMD has historically been a primary driver in processor innovation.They created the first native multi-core dies, broke the Ghz barrier, first to debut dynamic clock speeds, invented the seamless x64 transition and AMD64 instruction set, created CMT, created HSA, created the APU, and so much more. And I'm only focusing on CPUs, here.

Intel uses a great deal of AMD tech, and vice-versa.

smilingcrow - Thursday, August 18, 2016 - link

I used to buy AMD exclusively but they have been second rate for 10 years now.I don't buy innovations I buy products and AMD have really struggled for a decade to offer decent products unless your main criteria is value.

Value is fine but for mobile products where power consumption is very important and for workstations where performance is king AMD have had nothing to compete.

I'm very glad that Zen is looking as if it will compete at the higher end although I think they will find it harder to compete with Core M.

Just because I don't view AMD through ten year old rose tinted glasses doesn't mean I don't want them to succeed.

I have been feeling confident for Zen as an 8c/16t chips for ages but it's how it does as a 4c/8t chip that may well be more important in the consumer space unless the 8c/16c chip is unusually cheap for its performance level which it could even be.

Some people here can't tell the difference between someone who is critical of AMD's failings and an Intel fanboy. Intel have their issues but they have delivered decent chips in the decade that AMD fell into disarray. I'm not loyal to incompetent companies.

Nagorak - Thursday, August 18, 2016 - link

It's been hard for anyone to stick with AMD for the last decade. Phenom and Phenom II came up short, and then Bulldozer turned out to be a total disaster. In retrospect AMD should have tossed Bulldozer in the trash and started work on a new processor design immediately. Trying to iterate on that failed design is what almost killed AMD.Gigaplex - Thursday, August 18, 2016 - link

"Created the APU".That's not entirely accurate. Intel was actually first to market with their "APU" type CPUs, even though AMD announced theirs first.

KPOM - Friday, August 19, 2016 - link

These days ARM (soon SoftBank) is the company that keeps Intel management up at night. Intel missed the boat on mobile.Kevin G - Saturday, August 20, 2016 - link

The first dual core chip was POWER4 from IBM.Dynamic clock speeds existed in mobile (think ARM/MIPS) designs back in the 90's.

Seamless x86 transition could be credited to Transmeta for thei VLIW based Crusoe line of chips running x86 code. Runner up could be the FX32! emulator that ran unmodifed x86 Windows binaries in Alpha based hardware back in the 90's.

CMT was done beforehand in Sun's Niagra chip. There designs even before that did unit sharing for CMT.

Elements of HSA came from 3Dlabs and their cards supporting a unified virtual address space.

Integrating a CPU and GPU was first done by Intel though they never shipped it due to relaying on a flawed RDRAM to SDRAM buffer chip:

http://m.theregister.co.uk/2007/02/06/forgotten_te...

Thus the only innovation on your list is the 1 Ghz clock rate for a CPU, which isn't that innovative.

Klimax - Saturday, August 20, 2016 - link

Sorry, wrong. Multicores weren't AMD''s invention, dynamic clock speeds were parallel execution, x64 transition si AMD win only thanks to Microsoft who killed Intel's own development, CMT is not AMD¨s invention (and I would say it is nothing to be proud of), HSA is just label for preexisting technologies, APU was done before AMD's own (in fact, Intel had APU-like chip in late 80s),. AMD didn't invent much as most of technologies were bought in previous acquisitions like HyperTransport (See DEC Alpha)Sorry, to tell you, but what you posit is pure fantasy. AMD inveted very few things and fewer of them were of much importance or use.