AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTDeciphering the New Cache Hierarchy

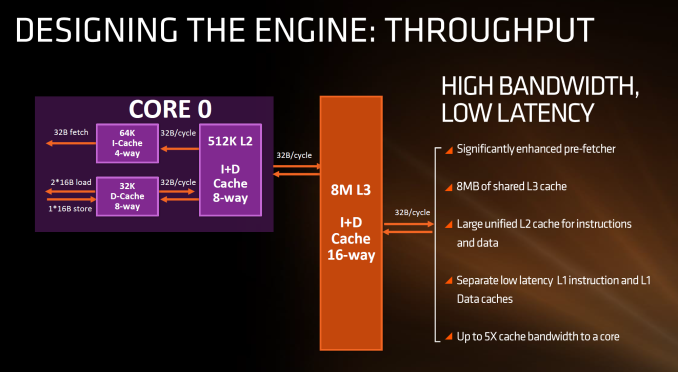

The cache hierarchy is a significant deviation from recent previous AMD designs, and most likely to its advantage. The L1 data cache is both double in size and increased in associativity compared to Bulldozer, as well as being write-back rather than write-through. It also uses an asymmetric load/store implementation, identifying that loads happen more often than stores in the critical paths of most work flows. The instruction cache is no longer shared between two cores as well as doubling in associativity, which should decrease the proportion of cache misses. AMD states that both the L1-D and L1-I are low latency, with details to come.

The L2 cache sits at half a megabyte per core with 8-way associativity, which is double that of Intel’s Skylake which has 256 KB/core and is only 4-way. On the other hand, Intel’s L3/LLC on their high-end Skylake SKUs is at 2 MB/core or 8 MB/CPU, whereas Zen will feature 1 MB/core and both are at 16-way associativity.

Edit 7:18am: Actually, the slide above is being slightly evasive in its description. It doesn't say how many cores the L3 cache is stretched over, or if there is a common LLC between all cores in the chip. However, we have recieved information from a source (which can't be confirmed via public AMD documents) that states that Zen will feature two sets of 8MB L3 cache between two groups of four cores each, giving 16 MB of L3 total. This would means 2 MB/core, but it also implies that there is no last-level unified cache in silicon across all cores, which Intel has. The reasons behind something like this is typically to do with modularity, and being able to scale a core design from low core counts to high core counts. But it would still leave a Zen core with the same L3 cache per core as Intel.

| Cache Levels | ||||

| Bulldozer FX-8150 |

Zen | Broadwell-E i7-6950X |

Skylake i7-6700K |

|

| L1 Instruction | 64 KB 2-way per module |

64 KB 4-way | 32 KB 8-way | 32 KB 8-way |

| L1 Data | 16 KB 4-way Write Through |

32 KB 8-way Write Back |

32 KB 8-way Write-Back |

32 KB 8-way Write-Back |

| L2 | 2 MB 16-way per module |

512 KB 8-way | 256 KB 8-way | 256 KB 4-way |

| L3 | 1 MB/core 64-way |

1 or 2 MB/core ? 16-way |

2.5 MB/core 16/20-way |

2 MB/core 16-way |

What this means, between the L2 and the L3, is that AMD is putting more lower level cache nearer the core than Intel, and as it is low level it becomes separate to each core which can potentially improve single thread performance. The downside of bigger and lower (but separate) caches is how each of the cores will perform snoop in each other’s large caches to ensure clean data is being passed around and that old data in L3 is not out-of-date. AMD’s big headline number overall is that Zen will offer up to 5x cache bandwidth to a core over previous designs.

216 Comments

View All Comments

patel21 - Friday, August 19, 2016 - link

Actually whom are you asking these questions ?Peichen - Friday, August 19, 2016 - link

Lets hope this isn't another one of AMD's empty claim that we've all seen like 8 times over the last 10 years on both CPU, GPU and the nonsense APU.The stock tripled over the last 12 months but that's only if Zen can deliver. If Zen is another <fill in AMD product for the last 10 years>, AMD will be a dollar stock again.

mxnerd - Friday, August 19, 2016 - link

Wow. AMD stock climbs 12.5% after the news.jihe - Friday, August 19, 2016 - link

I pray to god this is a worthwhile processorjust4U - Friday, August 19, 2016 - link

All it really needs to be is competitive on the performance front. It doesn't need to beat Intel but hey if it can well shoot.. that would be interesting. Not expecting that or even hoping for it since I think that would be unrealistic.cocochanel - Friday, August 19, 2016 - link

If Zen is good enough, it'll take some market share away from Intel, but not much since Intel CPU's are pretty much state of the art. However, the real advantages will come with their APU's (Zen + Polaris). The upcoming PlayStation Neo and Xbox Scorpio will use them. AMD will also go after mobile since they have no completion there with their APU's. Intel has some powerful iGPU's but they are nowhere near AMD APU's in performance. With the node disadvantage gone away, performance and power consumption should be up there. I know the desktop diehards will disagree, but desktops sales have been falling for years. Likely causes are a move by many to mobile devices and cheap, powerful gaming consoles. I don't see that trend changing. The ARM ecosystem is also rolling along and now it's beginning to creep into so far, exclusive x86 server markets. VR will also force ARM designers to come up with more powerful hardware. The next 5-10 years should be interesting.Michael Bay - Friday, August 19, 2016 - link

Problem is, mobile itself has reached saturation and isn`t so attractive anymore. Plus, what AMD is to go there with, x86? Intel tried already.Node disadvantage will come back at some point, simply because it`s a matter of survival for intel.

Where things should get interesting is the server side. ARM is hardly a threat, but AMD might have a good product here with GPU+CPU compute, likely at lower price.

cocochanel - Friday, August 19, 2016 - link

My mistake. By mobile, I meant laptops and not tablets. It's still a big market.Intel regaining node advantage ? Mmm, from I have seen in tech reports ( and I am not a big expert ), both 10nm and 7nm will be a tough nut to crack and will cost huge amounts. Compared to years past, Intel is now up against big giants ( Samsung and TSMC ) who are making billions every year selling tons of ARM SoC and have the deep pockets needed for new nodes. The South Koreans and the Chinese are a smart bunch. I mean, look at the SSD market. Intel had a lock on that until Samsung decided that one was too many. Remember Thunderbold ? Nice tech, but now the market is moving away from it. Sadly, even for mighty Intel, the landscape has changed.

I hope you're right about the server market. AMD can use any sales they can get, but then again, Intel has a lock on that and they will get aggressive and mean if necessary ( it's big bucks, you know).

ARM not a threat ? Architecturally speaking, they have advantages, after all, x86 is a dinosaur and ARM business model is one of their biggest strengths. But you're right, the installed base for x86 is huge and it will take time. There are some big names, however ( Qualcomm and others ) pouring some serious money in it.

Should be interesting.

Michael Bay - Saturday, August 20, 2016 - link

x86 is a very functional dinosaur with A LOT of companies standing behind it. ARM can license all they want, to actually break in and make those huge server monies, you need a full sw/hw/oem stack.I`d look at IBM`s last hooray POWER thing as the real competitor for intel right now, with AMD hopefully coming in soon as well.

BillBear - Saturday, August 20, 2016 - link

Google has announced their intention to open up competition in the server space by fully adopting IBM's POWER chips over their entire server software/hardware stack and is working with AMD and others to make sure they can do the same thing with the ARM based server chips in development.Competition is a good thing.