AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTSimultaneous Multi-Threading

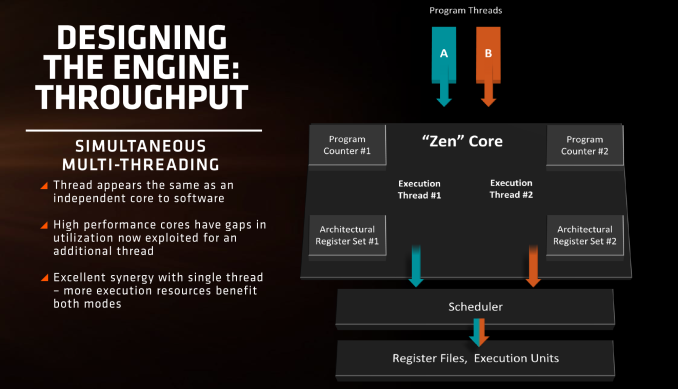

On Zen, each core will be able to support two threads in what is called ‘simulatenous multi-threading’. Intel has supported their version of SMT for a number of years, and other CPU manufacturers like IBM support up to 8 threads per core on their POWER8 platform designs. Building a core to be able to use multiple threads can be tough, as it requires a lot of resources to make sure that the threads do not block each other by consuming all the cache and buffers in play. But AMD will equip Zen with SMT which means we will see 8C/16T parts hitting the market.

Unlike Bulldozer, where having a shared FP unit between two threads was an issue for floating point performance, Zen’s design is more akin to Intel’s in that each thread will appear as an independent core and there is not that resource limitation that BD had. With sufficient resources, SMT will allow the core instructions per clock to improve, however it will be interesting to see what workloads will benefit and which ones will not.

Timeframe and Availability

At the presentation, it was given that Zen will be available in volume in 2017. As the AM4 platform will share a socket with Bristol Ridge, users are likely to see Bristol Ridge systems from AMD’s main OEM partners, like Dell and others, enter the market before separate Zen CPUs will hit the market for DIY builders. It’s a matter of principle that almost no consumer focused semiconductor company releases a product for the sale season, and Q1 features such events as CES, which gives a pretty clear indication of when we can expect to get our hands on one.

It’s worth noting that AMD said that as we get closer to launch, further details will come as well as deeper information about the design. It was also mentioned that the marketing strategy is also currently being determined, such that Zen may not actually be the retail product name for the line of processors (we already have Summit Ridge as the platform codename, but that could change for retail as well).

Wrap Up

AMD has gone much further into their core design than I expected this week. When we were told we had a briefing, and there were 200-odd press and analysts in the room, I was expecting to hear some high level puff about the brand and a reiteration of their commitment to the high end. To actually get some slides detailing parts of the microarchitecture, even at a basic cache level, was quite surprising and it somewhat means that AMD might have stolen the show with the news this week.

We’ve got another couple of pieces detailing some of the AMD internal/live benchmark numbers during the presentation, as well as the dual socket server platform, the 32-core Naples server CPU, and what we saw at the event in terms of motherboard design.

216 Comments

View All Comments

Ro_Ja - Thursday, August 18, 2016 - link

I just want Zen and hope people who are waiting for it won't be disappointed.MrSpadge - Thursday, August 18, 2016 - link

"Unlike Bulldozer, where having a shared FP unit between two threads was an issue for floating point performance, Zen’s design is more akin to Intel’s in that each thread will appear as an independent core and there is not that resource limitation that BD had. With sufficient resources, SMT will allow the core instructions per clock to improve"Ian, this section makes no sense! The reason Bulldozer and kids were slow was not the module design, but simply the cores being too weak. What helps Zen is not SMT but rather the fatter cores and the power optimization. If Zen had only 2 FP execution units, the maximum FP throughput per clock would be the same as for Bulldozer, independent of whether 1 or 2 threads run on a core / module. Or similarly if a Bulldozer module would have gotten 4 FPUs.

Nagorak - Thursday, August 18, 2016 - link

As I understand it the issue was that for many purposes Bulldozer cores were really only dual core, not four true cores.TheinsanegamerN - Friday, August 19, 2016 - link

bulldozer had one FPU (a weaksauce FPU at that) for two cores, zen will have one FPU per core, the way intel does it.jjj - Thursday, August 18, 2016 - link

You list Broadwell-E L3$ at 1.5MB per core but they got 2.5.AMD with less cache and likely 2 mem chans might get away with substantially lower power and smaller die as well as lower BOM for system builders and only a minor perf penalty in consumer.

SunnyNW - Thursday, August 18, 2016 - link

Seems they wanted some press since this week and since they have a Zen presentation at Hot Chips next week anyway the timing doesnt hurt.SunnyNW - Thursday, August 18, 2016 - link

Wow that got sent ALL wrong lol....With them presenting at Hot Chips next week anyway grabbing some press this week doesnt hurt.

extide - Thursday, August 18, 2016 - link

OMG, SO excited for this. Gotta say that the FinFet GPU's and Zen are some of the most anticipated releases in a long time! I remember when I used to get excited about Intel releasing new arch's but these days that's so boring!SunnyNW - Thursday, August 18, 2016 - link

"We’ve got another couple of pieces detailing some of the AMD internal/live benchmark numbers during the presentation, as well as the dual socket server platform, the 32-core Naples server CPU, and what we saw at the event in terms of motherboard design. "Please hurry up and publish these benchmark numbers!! :)

SunnyNW - Thursday, August 18, 2016 - link

NICE!!https://www.youtube.com/watch?v=oQS8s7TOXsE