IEDM 2019

I’ve constantly stated for the last two years that the next battleground in performance for the semiconductor market is going to be in the interconnect – whether we’re speaking about on chip with new manufacturing technologies or new topologies, or between chips with new communication standards or connectivity paradigms that shake up both bandwidth and efficiency. Moving from monolithic designs to chiplets and stacked silicon requires a fundamental shift in thinking that most of the industry is not yet ready for, from silicon engineers to vendors who design the software that enables silicon engineers to do their thing. You might not be surprised that Intel has a whole department dedicated to these new interconnect and packaging technologies. Ramune Nagisetty works across Intel's broad range...

Kioxia: 3D Stacked Storage Class Memory, like 3D XPoint, Isn’t the Future

One of the key battlegrounds of the next decade is going to be storage: density, speed, and demand. Naturally all the major players in the space want to promote...

23 by Dr. Ian Cutress on 12/30/2019Early TSMC 5nm Test Chip Yields 80%, HVM Coming in H1 2020

Today at the IEEE IEDM Conference, TSMC is presenting a paper giving an overview of the initial results it has achieved on its 5nm process. This process is going...

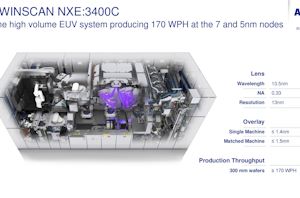

64 by Dr. Ian Cutress on 12/11/2019EUV Wafers Processed and TwinScan Machine Uptime: A Quick Look

One of the interesting elements that came out of some of our discussions at the IEDM conference this year revolve around the present deployment of EUV. Currently only one...

29 by Dr. Ian Cutress on 12/11/2019Intel: Lakefield in 2020, Possible 5G on Foveros

At the IEEE International Electron Devices Meeting (IEDM) 2019, Intel had two package integration presentations, one on its Omni-Directional Interconnect and one on its 3D stacking Foveros technology. In...

37 by Dr. Ian Cutress on 12/11/2019