Intel's Medfield & Atom Z2460 Arrive for Smartphones: It's Finally Here

by Anand Lal Shimpi on January 10, 2012 8:00 PM ESTThe CPU

Medfield is the platform, Penwell is the SoC and the CPU inside Penwell is codenamed Saltwell. It's honestly not much different than the Bonnell core used in the original Atom, although it does have some tweaks for both power and performance.

Almost five years ago I wrote a piece on the architecture of Intel's Atom. Luckily (for me, not Intel), Atom's architecture hasn't really changed over the years so you can still look back at that article and have a good idea of what is at the core of Medfield/Penwell. Atom is still a dual-issue, in-order architecture with Hyper Threading support. The integer pipeline is sixteen stages long, significantly deeper than the Cortex A9's. The longer pipeline was introduced to help reduce Atom's power consumption by lengthening some of the decode stages and increasing cache latency to avoid burning through the core's power budget. Atom's architects, similar to those who worked on Nehalem, had the same 2:1 mandate: every new feature added to the processor's design had to deliver at least a 2% increase in performance for every 1% increase in power consumption.

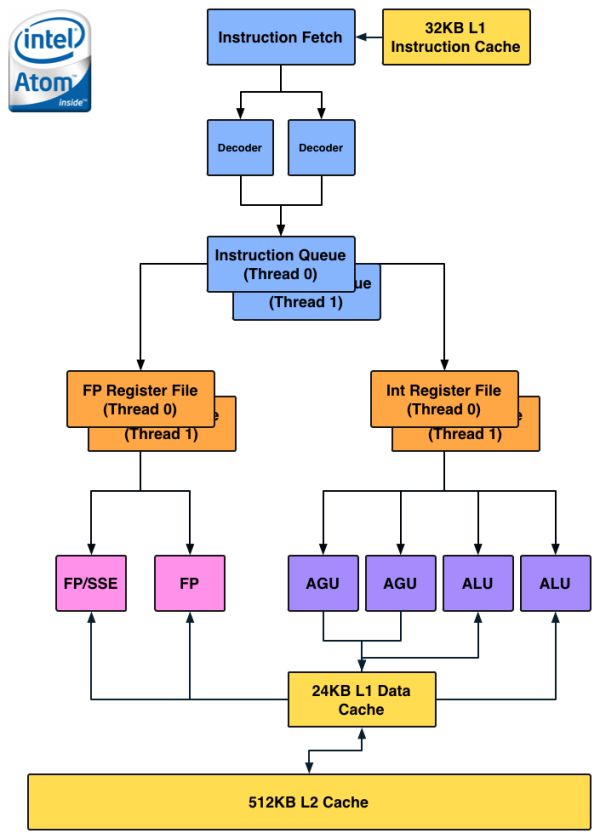

Atom is a very narrow core as the diagram below will show:

There are no dedicated integer multiply or divide units, that's all shared with the FP hardware. Intel duplicated some resources (e.g. register files, queues) to enable Hyper Threading support, but stopped short of increasing execution hardware to drive up efficiency. The tradeoff seems to have worked because Intel is able to deliver performance better than a dual-core Cortex A9 from a single HT enabled core. Intel also lucks out because while Android is very well threaded, not all tasks will continually peg both cores in a dual-core A9 machine. At higher clock speeds (1.5GHz+) and with heavy multi-threaded workloads, it's possible that a dual-core Cortex A9 could outperform (or at least equal) Medfield but I don't believe that's a realistic scenario.

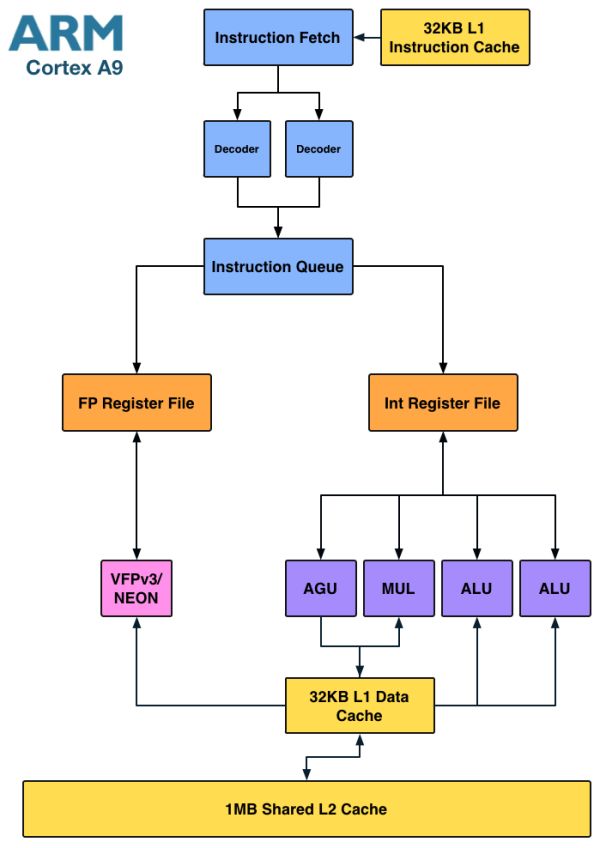

Architecturally the Cortex A9 doesn't look very different from Atom:

Here we see a dedicated integer multiply unit (shared with one of the ALU ports) but only a single port for FP/NEON. It's clear that the difference between Atom and the Cortex A9 isn't as obvious at the high level. Instead it's the lower level architectural decisions that gives Intel a performance advantage.

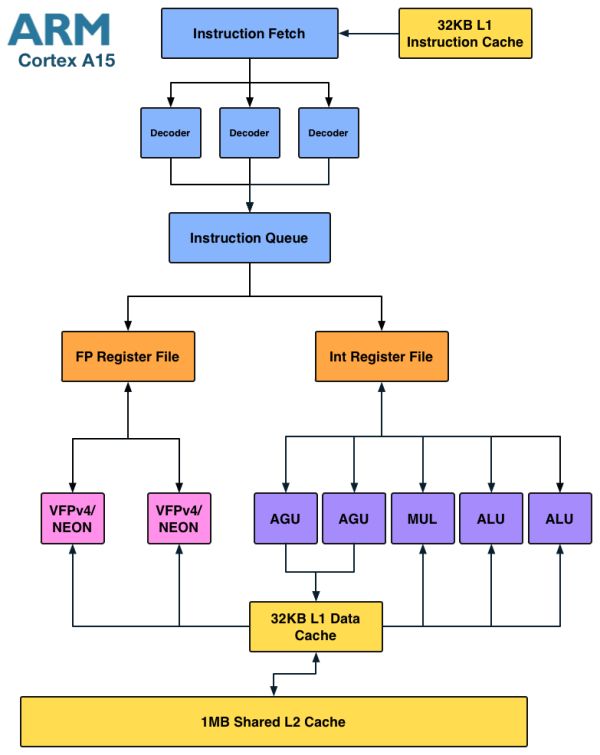

Where Intel is in trouble is if you look at the Cortex A15:

The A15 is a far more modern design, also out of order but much wider than A9. I fully expect that something A15-class can outperform Medfield, especially if the former is in a dual-core configuration. Krait falls under the A15-class umbrella so I believe Medfield has the potential to lose its CPU performance advantage within a couple of quarters.

Enhancements in Saltwell

Although the CPU core is mated to a 512KB L2 cache, there's a separate 256KB low power SRAM that runs on its own voltage plane. This ULP SRAM holds CPU state and data from the L2 cache when the CPU is power gated in the deepest sleep state. The reasoning for the separate voltage plane is simple. Intel's architects found that the minimum voltage for the core was limited by Vmin for the ULP SRAM. By putting the two on separate voltage planes it allowed Intel to bring the CPU core down to a lower minimum power state as Vmin for the L2 is higher than it is for the CPU core itself. The downside to multiple power islands is an increase in die area. Since Medfield is built on Intel's 32nm LP process while the company transitions to 22nm, spending a little more on die area to build more power efficient SoCs isn't such a big deal. Furthermore, Intel is used to building much larger chips, making Medfield's size a relative nonissue for the company.

The die size is actually very telling as it's a larger SoC than a Tegra 2 with two Cortex A9s despite only featuring a single core. Granted the rest of the blocks around the core are different, but it goes to show you that the CPU core itself (or number of cores) isn't the only determination of the die size of an SoC.

The performance tweaks come from the usual learnings that take place over the course of any architecture's lifespan. Some instruction scheduling restrictions have been lifted, memory copy performance is up, branch predictor size increased and some microcode flows run faster on Saltwell now.

Clock Speeds & Turbo

Medfield's CPU core supports several different operating frequencies and power modes. At the lowest level is its C6 state. Here the core and L2 cache are both power gated with their state is saved off in a lower power on-die SRAM. Total power consumption in C6 of the processor island is effectively zero. This isn't anything new, Intel has implemented similar technologies in desktops since 2008 (Nehalem) and notebooks since 2010 (Arrandale).

When the CPU is actually awake and doing something however it has a range of available frequencies: 100MHz all the way up to 1.6GHz in 100MHz increments.

The 1.6GHz state is a burst state and shouldn't be sustained for long periods of time, similar to how Turbo Boost works on Sandy Bridge desktop/notebook CPUs. The default maximum clock speed is 1.3GHz, although just as is the case with Turbo enabled desktop chips, you can expect to see frequencies greater than 1.3GHz on a fairly regular basis.

Power consumption along the curve is all very reasonable:

| Medfield CPU Frequency vs. Power | ||||||

| 100MHz | 600MHz | 1.3GHz | 1.6GHz | |||

| SoC Power Consumption | ~50mW | ~175mW | ~500mW | ~750mW | ||

Since most ARM based SoCs draw somewhere below 1W under full load, these numbers seem to put Medfield in line with its ARM competitors - at least on the CPU side.

It's important to pay attention to the fact that we're dealing with similar clock frequencies to what other Cortex A9 vendors are currently shipping. Any performance advantages will either be due to Medfield boosting up to 1.6GHz for short periods of time, inherently higher IPC and/or a superior cache/memory interface.

164 Comments

View All Comments

guilmon19 - Tuesday, January 10, 2012 - link

http://www.brightsideofnews.com/news/2011/5/19/the...brightside actually does a very nice benchmark and analysis on the memory bandwith problem that arm has.

Exophase - Tuesday, January 10, 2012 - link

That was with an old i.MX51. The situation is different with newer Cortex-A9 SoCs, especially where the SoC designer didn't botch the main memory latency.grrrrr - Wednesday, January 11, 2012 - link

intel = FAKEEEEEEBOOOOOOO

Hector2 - Wednesday, January 11, 2012 - link

grow upshaolin95 - Wednesday, January 11, 2012 - link

what an awesome comment...what are you 5?Stuka87 - Thursday, January 12, 2012 - link

Shouldn't that be "FAAAAAAKE" as the 'e' is silent. So extending the 'e' out like that has no change on the sound of the word.If you are going to troll, at least do it properly.

chiddy - Sunday, January 15, 2012 - link

+1Morg. - Wednesday, January 11, 2012 - link

ARM's memory problem ???Year-old 40+nm parts are slightly slower than brand new Intel 32nm ?

yes arm has a memory problem indeed ..

the real market situation for medfield will probably be a LOT different and as usual Intel will still get some market space thanks to murky deals and stuff :p

guilmon14 - Wednesday, January 11, 2012 - link

I wasn't trying to dis ARM what i meant to show, with the link, is that ARM A8 cpu performance would be just as, if not more, then the current atom if it had similar memory performance.blazermaniac - Saturday, January 14, 2012 - link

murky deals...?