Corsair DDR3-2133 - How high and fast will it go?

by Rajinder Gill on August 28, 2008 3:00 AM EST- Posted in

- Memory

Reaching DDR3-2133, the hard way

We can rule out the use of quad-core processors in this task for a start. There are no quad-core processors currently available that can run 533FSB in a 24/7 configuration. Therefore, we are left looking at the dual-core Wolfdales, which represent a light enough load on the system to scale well over 500FSB. Of course, we stress a disclaimer at this point: there are always the offspring of Satan's donkey in the marketplace - some of us just are not born lucky when it comes to getting good retail processors.

Such was our case, so we're now limiting ourselves even further with a decent Wolfdale teamed up with an interesting X48 board to achieve at least stock DDR3-2133 specifications for the modules - and perhaps go a little higher. The constant thorn in my conscience while writing all this is few if any people buy 2GB kits - especially $500+ kits - anymore unless they are serious about benchmarking. However, benchmarkers are just as fussy as everyone else involved in overclocking. They want kits that scale well with voltage while running tight latencies at a very high bandwidth.

This Samsung based part can certainly satisfy the bandwidth requirements and then some, but it's not known for its ability to run tight latencies up high. This pretty much puts these particular 2GB kits into a niche within a niche market. It's rather like deciding between a 39 or 40 carat diamond for a dinner ring when your better half is already wearing a 45 carat wedding ring.

There might just be a redeeming quality for the Samsung part, as it is a very light capacitive load. This means it's less demanding of the MCH output stages compared to the typical Micron D9JNL, which gives it the potential to scale a little higher in raw speed. It may not manage tight latencies, but we must remember that Intel's Core 2 architecture has already shown it usually favors raw processor MHz as long as the all-important tRD (Performance Level) register is kept as low as possible.

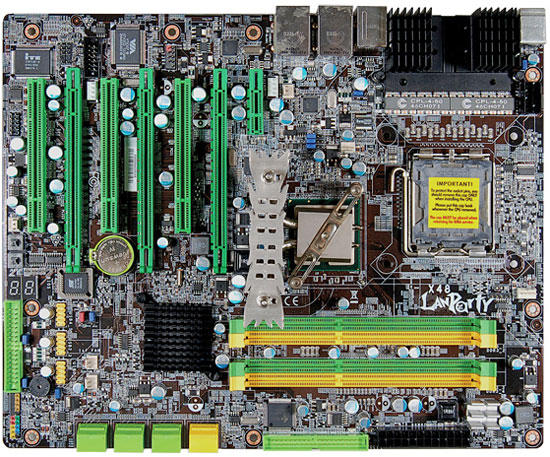

Shortly after the Corsair kit arrived in the labs, DFI shipped us their new LANParty UT X48 T3R motherboard. It uses DDR3 and is armed to the rafters with overclocking options - we thought we'd found the perfect partner. In truth, we could not have been more wrong at the time. The BIOS was still very much alpha level and had more quirks, knots, and idiosyncrasies than we care to list. We found ourselves receiving a new BIOS every few days just to get modules (any modules, much less these) to either boot or get the board to even resemble an overclocking product.

The rest was really down to our own inability to master this BIOS. Sure we've done it all before, but this one really is different and took every ounce of patience to get from A to Z. Finally, we are in a position to start appreciating the qualities of DFI's hell-boy, though it is still not without its disappointments. We provided our BIOS settings in the gallery below.

A full lowdown on this board will be given in an upcoming review. Meanwhile, let's look at what this red carpet pairing of parts can do. Will they self destruct, or will they waltz together like Astaire and Rogers?

7 Comments

View All Comments

hoohoo - Wednesday, September 10, 2008 - link

I want bandwidth numbers!geok1ng - Thursday, August 28, 2008 - link

It would be good to see a table with CAS, Trd, dividers and frequencies for DDR3 users, just as you did for DDR2 users on the Rampage formula review http://www.anandtech.com/mb/showdoc.aspx?i=3208&am...">http://www.anandtech.com/mb/showdoc.aspx?i=3208&am...using the data from these tables i would infer that the best option for an E8600 and a high end DDR3 is:

2:1 divider

tRD of 5

CPU at 10x400

DDR3 1600

These are the highest 12,5ns Trd timings displayed. Are they valid for a X48 DDR3 mobo?

If they are possible at CAS 6, just how far can the FSB be increased while keeping the tRD at 5?

What DDR3 modules are capable of reaching DDR3 1600+ at CAS 6 with the least voltage?

on the Rampage review the authors proposed a DDR2 1000 CAS 4 solution as the best option for running four sticks of RAM, with DDR2 1200 CAS 5 as an alternative for 2 sticks of RAM.

What are Anandtech suggestions for DDR3 builds on the X48 chipset?

Berger - Thursday, August 28, 2008 - link

Aiming for a tRD of 6 at around 450FSB on the 2:1 divider brings the best overall balance for a 24/7 system. tRD 5 is attractive but you will lose out on copy and write bandwidth without sufficient FSB to bolster bandwidth. Plus the VMCH requirement is rather high for outright stability.For quad processors sticking around 400FSB is the best option, tRD 5 is likely to be too tight for some boards when armed with 4GB of memory.

Personally I don't like suing 'down' dividers - ie anything that pits the FSB slower than the memory bus. Too many wasted clock cycles.

regards

Raja

geok1ng - Sunday, August 31, 2008 - link

So the problem is that for 10x450-a typical result for an E8600 at 1,4v- one can either run the memory at 2:1 and relaxed tRD and CAS or try slower memo speeds but tighter CAS and tRD. quoting the article i posted:"Moving on to the analysis at 450Mhz FSB, although we are able to show impressive memory read speeds at this same bus frequency using a 3:2 divider for DDR2-1350 CAS 5 at a tRD of 5, this configuration was far from stable on stock cooling alone - as was the memory speed. Most likely, the need to loosen tRD to 6 will be inevitable at this bus speed"

So from your tests DDR3 based mobos didnt break the 1350Mhz barrier for tRD 5 operation?

Is CAS 5,tRD 5 at the 1250-1350 range really that demanding on the NB?

Is CAS 6,tRD 6 at 1800Mhz so much faster?

What about CAS 5 tRD 6 operation at DDR3 1710 as in http://www.xtremesystems.org/FORUMS/showthread.php...">http://www.xtremesystems.org/FORUMS/showthread.php... Sure the write and copy speeds are lower, but 45ns latency at "just" 1710Mhz is nothing to be ashamed of.

Berger - Thursday, August 28, 2008 - link

*Edit* that should read using down dividers where the memory bus is running slower than the FSB. We don't have up didviders on DDR3 anyway. 2:1 is where the action is at on DDR3.regards

Raja

strikeback03 - Thursday, August 28, 2008 - link

You sign as Raja here, as Berger in the NVIDIA comments, who are you?nevbie - Thursday, August 28, 2008 - link

Putting those BIOS screens into a gallery looks good - it's the first time I see this new gallery function used in an interesting way.