Intel's Silverthorne Unveiled: Detailing Baby Centrino

by Anand Lal Shimpi on February 20, 2008 12:00 AM EST- Posted in

- CPUs

The Memory Subsystem

Silverthorne's in-order architecture also means that it is susceptible to high memory latencies. If a dependent instruction's data isn't available in cache on an out-of-order processor, it can simply re-order instructions around the dependency. With an in-order core however, if an instruction needs data that isn't yet available, it can't continue executing other independent instructions further down the instruction queue until that data becomes available. Making matters worse, Silverthorne has no on-die memory controller - this is something it will get in 2009/2010 with the Moorestown platform.

Silverthorne lacks an integrated memory controller and graphics core simply because Intel's 45nm memory controller and graphics core designs weren't finalized in time for Silverthorne's launch. Moorestown, which will also be built on Intel's 45nm process, will add an on-die memory controller and on-die graphics as well.

Thankfully, Intel has outfitted Silverthorne with fairly large caches. The L1 cache is unusually asymmetric with a 32KB instruction and 24KB data cache, a decision made to optimize for performance, die size, and cost. The L2 cache is an 8-way 512KB design, very similar to what was used in the Core architecture.

While Silverthorne is built entirely on Intel's high-k/metal gate 45nm process, there is one major difference: SRAM cell size. Intel uses a 0.382 um^2 SRAM cell in Silverthorne compared to 0.346 um^2 in Core 2. Each SRAM cell is an 8 transistor design compared to 6 transistors in Core 2. The larger cell size increases the die size of Silverthorne but it draws less power and runs at a lower voltage.

FSB, Performance, Clock Speeds, and Transistors

Silverthorne is connected to the outside world by a quad-pumped FSB similar to what Intel uses in its other processors, with some significant power tweaks. The FSB can operate at either 533MHz or 400MHz depending on power state/performance demands.

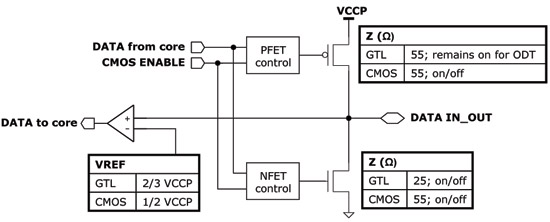

Dual Mode FSB

Ever since the P6 Intel has used a Gunning Transistor-Logic (GTL) based FSB, while Silverthorne's FSB can work in either a GTL or CMOS based mode. In CMOS mode power consumption is reduced significantly by turning off on-die termination and operating at half the voltage of GTL mode. Unfortunately, Intel couldn't give us more details as to what tradeoffs are made in order to achieve lower power operation in CMOS mode.

Silverthorne's pipeline depth is a bit on the long side, especially considering that it is an in-order core (which generally have shorter pipelines than out-of-order designs). Even the Core 2 architecture features a shorter 14-stage design, so we suspect that Intel needed a longer pipe to reach Silverthorne's clock and power targets.

Intel has stated publicly that Silverthorne is going to offer performance competitive with the first Pentium M processors, from both a clock speed and application performance standpoint. We'll touch on the application performance side of that momentarily, but the clock speed claims are reasonable. Thanks to a fairly deep pipeline, a very simple in-order core, and a very clockable 45nm manufacturing process Intel should have no problems hitting clock speeds in the 1 - 2GHz range. Intel's ISSCC paper states that performance is similar to mainstream Ultra-Mobile PCs, meaning that we should expect these things to perform at the level of a low 1GHz Core Solo processor.

The decision to go in-order made a lot of sense to Intel. Intel took its 20W TDP mobile Core 2 processors, scaled them down to 3W, and discovered that the best it could manage was a paltry 1GHz clock speed. The power consumption needed to be lower and clock speeds/performance needed to be higher, and thus a new design using an in-order architecture was necessary. This is especially true once you start looking at average and idle power, both of which need to be in the 10s - 100s of mW; in-order is necessary given the performance targets. While eventually we may see an out-of-order derivative (much as desktop microprocessors were in-order until out-of-order became feasible), Intel stated that for the next 5 years we're looking at in-order.

Silverthorne is built far more modularly than Core 2 or any of Intel's previous mobile microprocessors; it is honestly built more like a GPU than a CPU. Only 9% of the chip uses custom logic, and the rest is built using standard Intel circuit libraries. The L2 cache, PLLs, data I/O, addressing I/O, and a few other elements are standard logic for two reasons: time to market and flexibility.

Intel has been working on Silverthorne for 4 years now, so time to market was clearly not an issue for this first design - but for subsequent incarnations, it is. A standard design that's very modular will allow Intel to quickly integrate custom logic on a demand basis for specific markets. Intel could conceivably have a slightly different version of Silverthorne, with quick turnaround, for CE markets or for embedded applications.

12 Comments

View All Comments

HelpfulVisitor - Wednesday, February 20, 2008 - link

Anand wrote the following:"The at 2.0GHz, running at 1.0V, Silverthorne runs at 90C and dissipates 2W. The CPU temperature alone should be indication that this is too hot for an ultra small iPhone-like form factor"

When the specs state TDP power at a given temperature, they are not claiming that the chip will dissipate that high of a temperature. They are baselining the TDP measurement, because leakage varies over different temperatures, and TDP needs to account for worst case conditions. It is standard practice to use the max Tcase temperature as a baseline, which is the temperature that the chip cannot exceed without permanent damage. Most chips operate WELL BELOW this.

While I cannot argue that Silverthorne would be inappropriate for iPhone, it is not because of the 90c degree specification. The 90c degree measurement only refers to where the thermal contraint specification has been measured.

stockascnc - Thursday, September 30, 2021 - link

NCFM Academy Hyderabad is one of the maximum properly know institutes now not simplest in Ameerpet but also in Hyderabad. <a href="https://www.ascncfmacademy.com/">Stock Market Training Institute in Hyderabad</a> We additionally offer Advanced Technical analysis training both on line and offline. We have designed the courses with years of experience and those publications will assure you success for sure. Just be part of the NCFM Academy Hyderabad if you need to research Advanced Technical Analysis. You can also study this course in Telugu too.Torched - Wednesday, February 20, 2008 - link

Going for the GeodeLX's jugular.puffpio - Wednesday, February 20, 2008 - link

Maybe Microsoft's answer to PSP and DS will use this hcipViRGE - Thursday, February 21, 2008 - link

I don't think so, the chip uses too much power. To give you an idea of the DS's power consumption, it comes with a 3.7v 1000mAh battery (in other words, 3.7watt-hours). Given that the DS lasts over 10 hours, you're looking at an average power consumption of 370mW for the entire device, meanwhile Silverthorne (just the CPU) is around 600mW before any other chips are added. The PSP/DS have the same power/thermal envelope as the iPhone, so you can count Silverthorne out of any similar device.Visual - Wednesday, February 20, 2008 - link

this just doesn't make sense... if it uses (and dissipates) less power than the scaled-down core cpus that are already in UMPCs, why would it's temperature be higher? why would it be harder to cool? why would it not be feasible for UMPCs?less is less, no matter how i look at it. i don't understand...

Visual - Wednesday, February 20, 2008 - link

oops, yeah. you said it wont be feasible for an iphone, not umpc.sorry i got confused... i guess it is just because i cant visualize the difference, not having seen either in person.

michael2k - Wednesday, February 20, 2008 - link

UMPC is about twice as big as an iPhone.UMPC is about half the size of an ultraportable laptop.

Calin - Wednesday, February 20, 2008 - link

"Inevitably the comparison to VIA's recently announced Isaiah CPU will be made, but Silverthorne is really aimed at a different market. Isaiah is a higher performance out-of-order core, while Silverthorne is eventually designed to make its way into highly integrated CE devices. We expect VIA's latest creation to outperform Silverthorne"I've never believed I'd live to see that - VIA outperforming Intel.

True, they might be targeting different power envelopes, but certainly Intel used to run circles around its competition from VIA

marsbound2024 - Wednesday, February 20, 2008 - link

On the "Who is Silverthorne" page, you repeated a paragraph talking about the sensibility of executing two IPC. Just wanted to throw that out there. :)