Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

by Dr. Ian Cutress on July 30, 2019 9:30 AM EST- Posted in

- CPUs

- Intel

- 10nm

- Microarchitecture

- Ice Lake

- Project Athena

- Sunny Cove

- Gen11

Using Power More Efficiently: Dynamic Tuning 2.0

A common thread in modern microprocessor design is being able to use the power budget available. There have been many articles devoted to how to define power budgets, thermal budgets, and what the mysterious ‘TDP’ (thermal design power) actually means in relation to power consumption. Intel broadly uses TDP and power consumption simultaneously, along with a few other values, such as power limits 1 and 2 (PL1 and PL2), which apply to sustained power draw and peak power draw respectively. Most Intel processors up until this point will allow a processor to turbo, up to a peak power draw of PL2 for a fixed time, before enforcing a PL1 sustained power draw. This is all very OEM dependent as well. However, for Ice Lake, this changes a bit.

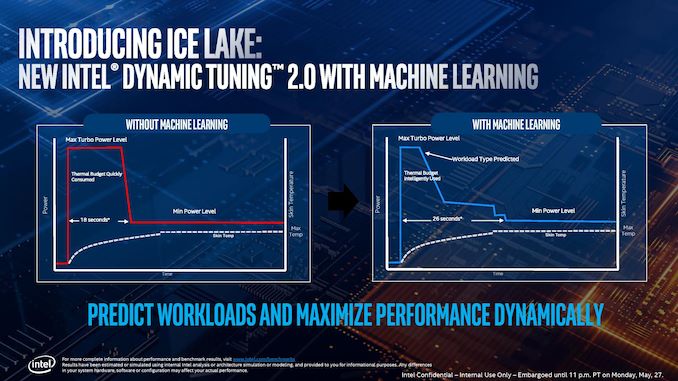

For Ice Lake, Intel has a new feature called Dynamic Tuning 2.0, which implements a layer of machine learning on top of the standard turbo mode. The idea behind DT2.0 is that the processor can predict the type of workload that is incoming, say transcode, and adjust the power budget intelligently to give a longer turbo experience.

Technically the concepts of PL1 and PL2 don’t magically disappear under this new regime – the processor ends up going below max turbo because the algorithm predicts that the user won’t need it, and this saves up ‘power budget’ in order to enable the turbo to work for longer.

This is a topic that Intel will hopefully go into more detail. We do know that it requires collaboration at the OS level, but how these algorithms are trained would be a useful trove of information. It is unclear whether Intel will allow this feature to be enabled/disabled at the user level, for testing purposes, but it should be noted that unless it is by default ‘on’ for OEM systems, we might end up with some systems enabling it while others do not.

107 Comments

View All Comments

eastcoast_pete - Tuesday, July 30, 2019 - link

Thanks Ian! One initial observation: that slide or picture from Dell showing processor options for their 2in1 has the i7 with 4 MB of cache; my guess is Dell needs a proofreader in their marketing department (:Ian Cutress - Tuesday, July 30, 2019 - link

It's likely those cache numbers are the other way round, i.e. quad core i7 with 8MB, dual core i3 with 4MB. That would align with what we would expect.eastcoast_pete - Tuesday, July 30, 2019 - link

Agree. Looks a lot like somebody at Dell didn't check after cut-and-paste. Has Dell announced expected shipping date? As a launch partner, they're likely be among the first who ship finished product.Ian Cutress - Tuesday, July 30, 2019 - link

Not yet, as far as I know.close - Tuesday, July 30, 2019 - link

Now we know the cause of Intel's manufacturing hell. Ian's been biting their wafers... :)tipoo - Tuesday, July 30, 2019 - link

iirc Dell said NDA was lifting August 1st on the ICL XPS 13FloconDeNeige - Tuesday, July 30, 2019 - link

Page 2, the table about In-Flight Stores and Loads: The values are switched around, or else the paragraph after is wrong.Otherwise looks like a great article. Still reading :)

FloconDeNeige - Tuesday, July 30, 2019 - link

Page 3 sorryDanNeely - Tuesday, July 30, 2019 - link

I'm a bit surprised to see pen support on the Athena requirement list. Everything else seems reasonable as an evolution of mainstream designs; but pens have always been very niche something I don't see changing. Even if pen support is baked into Intels <1W LCDs; including a pen's going to drive up system costs. And if loose is just going to end up lost; if a pen holster is required that's a decent amount of internal volume in increasing thin and dense designs.notashill - Tuesday, July 30, 2019 - link

There are already tons of laptops with pen support but no included pen or internal holster.