The IBM POWER8 Review: Challenging the Intel Xeon

by Johan De Gelas on November 6, 2015 8:00 AM EST- Posted in

- IT Computing

- CPUs

- Enterprise

- Enterprise CPUs

- IBM

- POWER

- POWER8

The L4-cache and Memory Subsystem

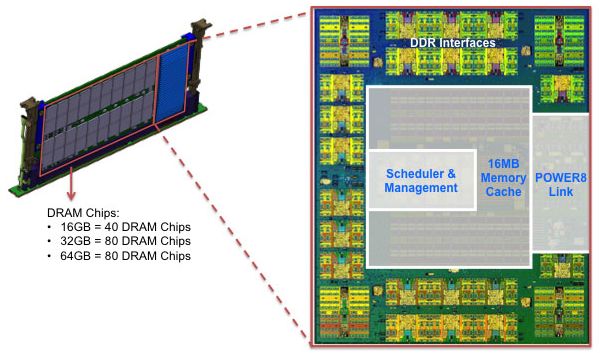

Each POWER8 memory controller has access to four "Custom DIMMs" or CDIMMs. Each CDIMMs is in fact a "Centaur" chip and 40 to 80 DRAM chips. The Centaur chip contains the DDR3 interfaces, the memory management logic and a 16 MB L4-cache.

The 16 MB L4-cache is eDRAM technology like the on-die L3-cache. Let us see how the CDIMMs look in reality.

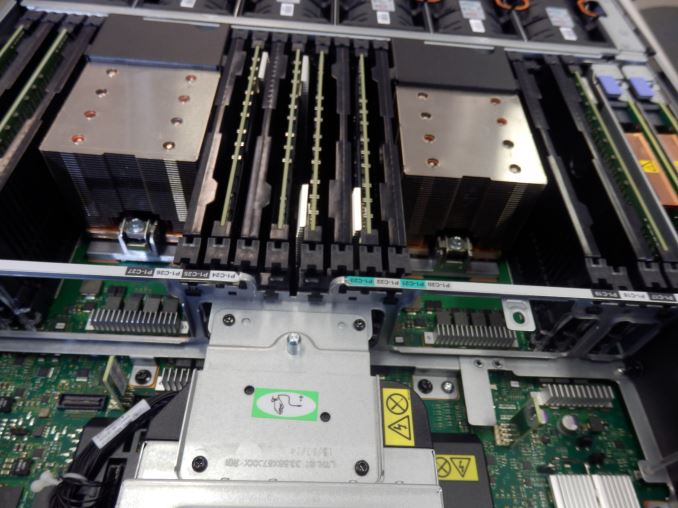

Considering that 4Gb DRAM chips were available in mid 2013, the 1600 MHz 2Gb DRAM chips used here look a bit outdated. Otherwise the (much) more expensive 64GB CDIMMs use the current 4Gb DRAM chips. The S822L has 16 slots and can thus use up to 1TB (64GB x 16) in DIMMs.

Considering that many Xeon E5 servers are limited to 768 GB, 1 TB is more than competitive. Some Xeon E5 servers can reach 1.5 TB with 64 GB LR-DIMMs but not every server supports this rather expensive memory technology. It is very easy to service the CDIMMs: a gentle push on the two sides will allow you to slide them out. The black pieces of plastic between the CDIMMS are just place-holders that protect the underlying memory slots. For our testing we had CDIMMs installed in 8 of our system's 16 slots.

The Centaur chip acts as a 16MB L4-cache to save memory accesses and thus energy, but it needs quite a bit of power (10-20 W) itself and as a result is covered by heatsink. CDIMMs have ECC enabled (8+1 for ECC) and have also an extra spare DRAM chip. As result, a CDIMM has 10 DRAM chips while offering capacity of 8 chips.

That makes the DRAM subsystem of the S822L much more similar to the E7 memory subsystem with the "Scalable memory interconnect" and "Jordan Creek" memory buffer technology than to the typical Xeon E5 servers.

146 Comments

View All Comments

Michael Bay - Saturday, November 7, 2015 - link

You are probably still hurry.Or just not civilized enough.

JohanAnandtech - Saturday, November 7, 2015 - link

I have to disagree with "only old legacy". One of things I really want to tackle is running Apache Spark on POWER. Spark is one of the most exciting Big Data tools, it is a very modern piece of software. IBM claims that the POWER8 is very good at it, and I want to check that.Jake Hamby - Friday, November 6, 2015 - link

Very interesting review! I've been a PowerPC fan for many years. I even bought a used PowerMac Quad G5 a few years ago to hack on FreeBSD for PowerPC with (much cheaper than the latest gear).My only suggestion is that I would love to see you run the same benchmarks with big-endian Linux, since the entire stack is so much more mature for PPC than LE Linux, which as you mention wasn't even supported for many years.

Anyone running Java workloads in particular has no business using LE Linux when Java itself uses big-endian data formats, and IBM has 15+ years of tuning the JDK for big-endian Linux & AIX.

TL;DR is the biggest advantage of LE Linux is that it's easier to port large custom apps that were written for x86 and have too many byte ordering issues to fix. The original motivation to make the PowerPC architecture bi-endian instead of big-endian was the hope of a Windows NT port. When Apple went their own way with hardware, and IBM focused on servers, little-endian mode disappeared. It's good that POWER8 supports LE mode again, for customers who really need it, but it's far from the normal mode.

PS. I've been working on fixing bugs in Clang/LLVM for PowerPC arch (32/64-bit). FreeBSD recently switched from GCC 4.2.1 (final GPLv2 version) to Clang as the default system compiler on x86, but LLVM has some code gen bugs for PowerPC that I'm hoping to squash. For now, it doesn't work well enough for me to recommend trying to use Clang as an alternative to GCC for POWER8 benchmarking. Certainly not for little-endian mode.

Jake Hamby - Friday, November 6, 2015 - link

BTW, the name of the instruction set architecture is still PowerPC, even though IBM's chips are the POWER series. The predecessor architecture was named POWER, so I always write PowerPC to avoid confusion when referring to the instruction set. The PowerPC 970MP chips in my Quad G5 (2 x dual-core) are a derivative of POWER4.ZeDestructor - Saturday, November 7, 2015 - link

That would be incorrect actually (since they changed since in 2006).The ISA is (currently) named the Power ISA (previously "PowerPC ISA", the "ISA" bit is quite important to denote hardware architecture vs ISA) (with the current being Power ISA 2.07 B)

Underneath each ISA, there are a variety of designs that all have nice, different names, from POWER1-8, PowerPC (including the various variants used by Apple, like the G5/970), Power-PC-AS, Cell, most LSI controllers (mostly PowerPC 440 (Power ISA 2.03) based, afaik) etc.

Source: https://en.wikipedia.org/wiki/Power_Architecture

tipoo - Friday, November 6, 2015 - link

I wish I had a what-if machine to see what IBM would be making had they stayed in the consumer space (well, discounting some consoles they're in - currently only the Wii U on an ancient PowerPC 750 modified for tri-core). And how chunky that PowerBook G5 would have been :Phttp://forums.macrumors.com/attachments/powerbook_...

DanNeely - Friday, November 6, 2015 - link

Probably they'd've ended up making architectural tradeoffs that made their cores a lot more like Intel. As it is, they can optimize their designs for very high power isn't a problem because the power cost is a small fraction of the TCO on one of their monster servers; and a relatively minor concern for consoles (ie just dropping the core count gets them desktop CPU level thermals which are good enough). If they were still selling to Apple, they'd need to be well optimized for performance at only a few watts/core for laptops. Huge L1 caches and massive SMT would be gone because they'd devour battery power to little benefit on systems that generally functioned at very low average CPU loads vs on a mega server or mainframe where if you're not pushing enough work onto it to keep it at a high load level you're doing it wrong.Jake Hamby - Friday, November 6, 2015 - link

Yep. It feels a lot like Apple's own 64-bit ARM cores have approached the old G5 (PPC 970) from the other end of the power envelope.Kevin G - Saturday, November 7, 2015 - link

While Apple's engineers were given the task of a PowerBook G5, they new it could never happen due to thermals and a very arcane chipset. Case in point, the PowerPC 970 could not boot itself: it needed a service processor to calibrate and initialize the frontside bus for the processor before it could take control. Justifiable for servers but unnecessary for a consumer laptop.The expected Powerbook G5's were supposed to be using PA-Semi chips. Due to IBM not meeting Apple's goals, they switched to Intel and the PA-Semi deal fell through with it. However, their dealings with Apple did lead to Apply buying them out a few years later to help design custom ARM SoCs and eventually the custom ARM cores used in the iPhone/iPad of today.

JohanAnandtech - Saturday, November 7, 2015 - link

Would love to hear some thoughts on what the possible problems could arise if we rerun our tests on BE linux. Because our best benchmarks are all all based upon some data stored on our x86 fileservers - so they are probably stored in LE.