The Intel 6th Gen Skylake Review: Core i7-6700K and i5-6600K Tested

by Ian Cutress on August 5, 2015 8:00 AM ESTSkylake's iGPU: Intel Gen9

Both the Skylake processors here use Intel’s HD 530 graphics solution. When I first heard the name, alarm bells went off in my head with questions: why is the name different, has the architecture changed, and what does this mean fundamentally?

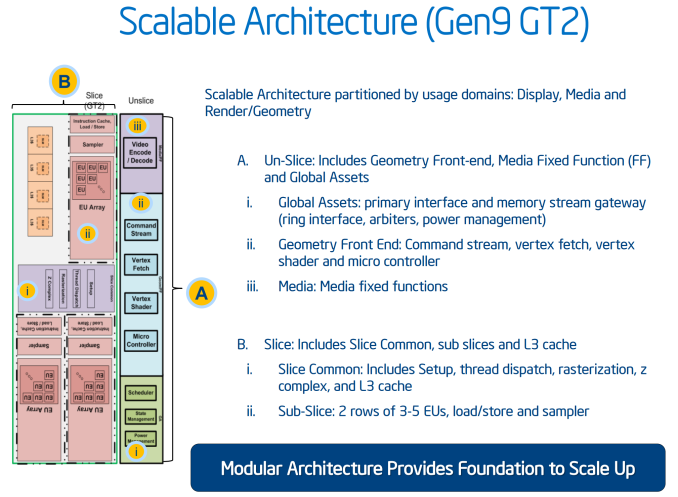

Not coming up with many details, we did the obvious thing – check what information comes directly out of the processor. Querying HD 530 via Intel's OpenCL driver reports a 24 EU design running at 1150 MHz. This is different than what GPU-Z indicates, which points to a 48 EU design instead, although GPU-Z is not often correct on newer graphics modules before launch day. We can confirm that this is a 24 EU design, and this most likely follows on from Intel’s 8th Generation graphics in the sense that we have a base GT2 design featuring three sub-slices of 8 EUs each.

As far as we can tell, Intel calls the HD 530 graphics part of its 9th Generation (i.e. Gen9). We have been told directly by Intel that they have changed their graphics naming scheme from a four digit (e.g. HD4600) to a three digit (HD 530) arrangement in order "to minimize confusion" (direct quote). Personally we find that it adds more confusion, because the HD 4600 naming is not directly linked to the HD 530 naming. While you could argue that 5 is more than 4, but we already have HD 5200, HD 5500, Iris 6100 and others. So which is better, HD 530 or HD 5200? At this point it will already create a miasma of uncertainty, probably exaggerated until we get a definite explanation of the stack nomenclature.

Naming aside, Generation 9 graphics comes with some interesting enhancements. The slice and un-slice now have individual power and clock domains, allowing for a more efficient use of resources depending on the load (e.g. some un-slice not needed for some compute tasks). This lets the iGPU better balance power usage between fixed-function operation and programmable shaders.

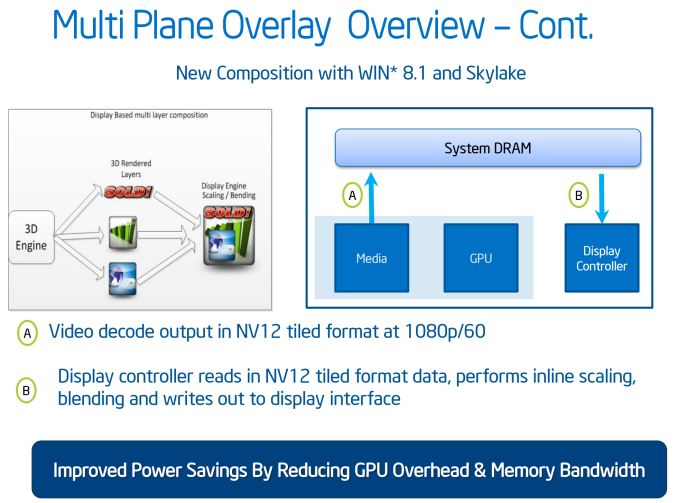

Generation 9 will support a feature called Multi Plane Overlay, which is a similar feature to AMD’s video playback path adjustments in Carrizo. The principle here is that when a 3D engine has to perform certain operations to an image (blend, resize, scale), the data has to travel from the processor into DRAM then to the GPU to be worked on, then back out to DRAM before it hits the display controller, a small but potentially inefficient operation in mobile environments. What Multi Plane Overlay does is add fixed function hardware to the display controller to perform this without ever hitting the GPU, minimizing power consumption from the GPU and taking out a good portion of DRAM data transfers. This comes at a slight hit for die area overall due to the added fixed function units.

As shown above, this feature will be supported on Win 8.1 with Skylake’s integrated graphics. That being said, not all imaging can be moved in this way, but where possible the data will take the shorter path.

To go along with the reduced memory transfer, Gen9 has support for memory color stream compression. We have seen this technology come into play for other GPUs, where by virtue of fixed function hardware and lossless algorithms this means that smaller quantities of image and texture data is transferred around the system, again saving power and reducing bandwidth constraints. The memory compression is also used with a scalar and format conversion pipe to reduce the encoding pressure on the execution units, reducing power further.

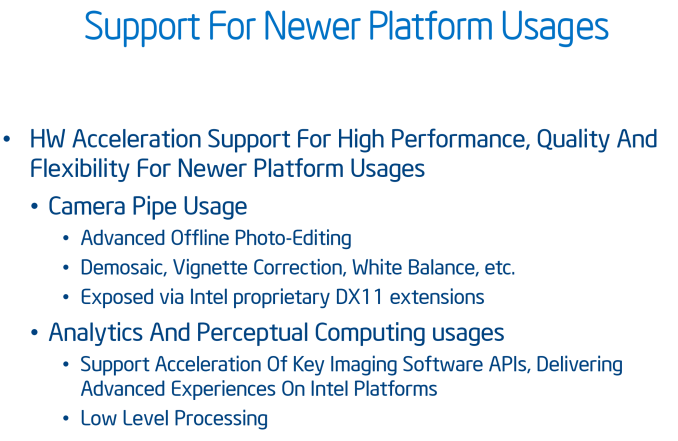

Adding into the mix, we have learned that Gen9 includes a feature called the ‘Camera Pipe’ for quick standard adjustments to images via hardware acceleration. This adjusts the programmable shaders to work in tandem for specific DX11 extensions on common image manipulation processes beyond resize/scale. The Camera Pipe is teamed with SDKs to help developers connect into optimized imaging APIs.

Media Encoding & Decoding

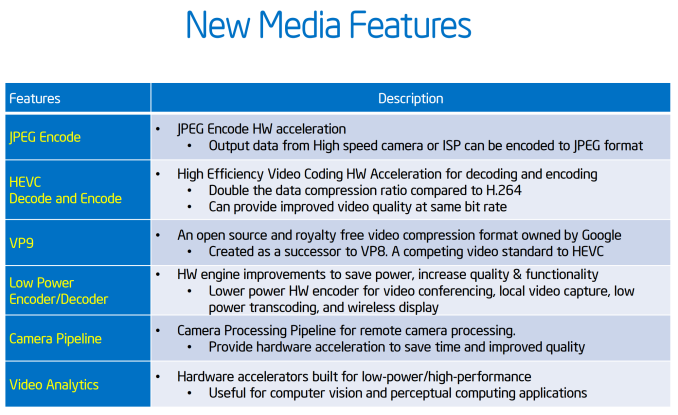

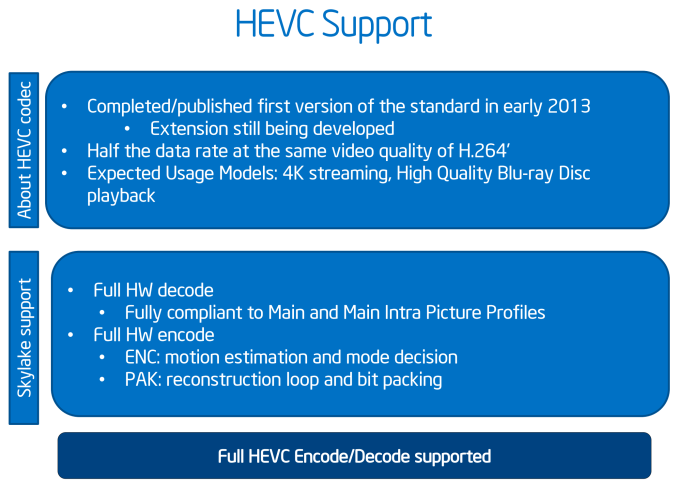

In the world of encode/decode, we get the following:

Whereas Broadwell implemented HEVC decoding in a "hybrid" fashion using a combination of CPU resources, GPU shaders, and existing GPU video decode blocks, Skylake gets a full, low power fixed function HEVC decoder. For desktop users this shouldn't impact things by too much - maybe improve compatibility a tad - but for mobile platforms this should significantly cut down on the amount of power consumed by HEVC decoding and increase the size and bitrate that the CPU can decode. Going hand-in-hand with HEVC decoding, HEVC encoding is now also an option with Intel's QuickSync encoder, allowing for quicker HEVC transcoding, or more likely real-time HEVC uses such as video conferencing.

Intel is also hedging their bets on HEVC by also implementing a degree of VP9 support on Skylake. VP9 is Google's HEVC alternative codec, with the company pushing it as a royalty-free option. Intel calls VP9 support on Skylake "partial" for both encoding and decoding, indicating that VP9 is likely being handled in a hybrid manner similar to how HEVC was handled on Broadwell.

Finally, JPEG encoding is new for Skylake and set to support images up to 16K*16K.

Video Support

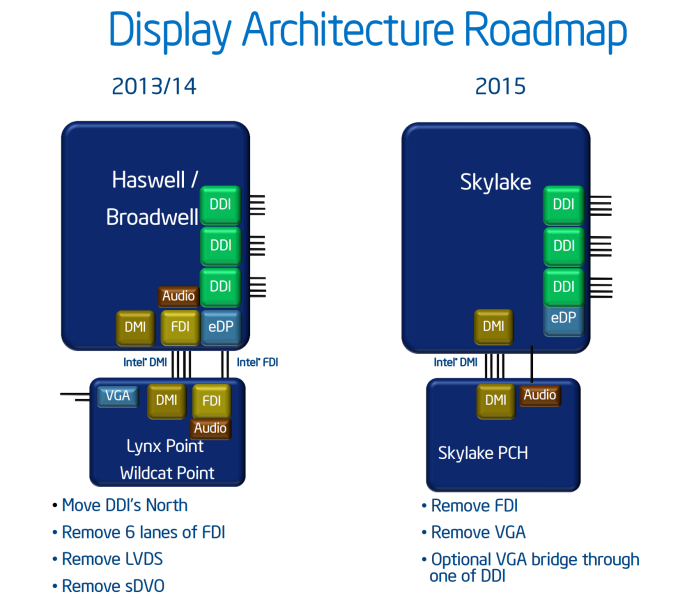

The analog (VGA) video connector has now been completely removed from the CPU/chipset combination, meaning that any VGA/D-Sub video connection has to be provided via an active digital/analog converter chip. This has been a long time coming, and is part of a previous committment made by Intel several years ago to remove VGA by 2015. Removing analog display functionality will mean added cost for legacy support in order to drive analog displays. Arguably this doesn’t mean much for Z170 as the high end platform is typically used with a discrete graphics card that has HDMI or DisplayPort, but we will see motherboards with VGA equipped in order to satisfy some regional markets with specific requirements.

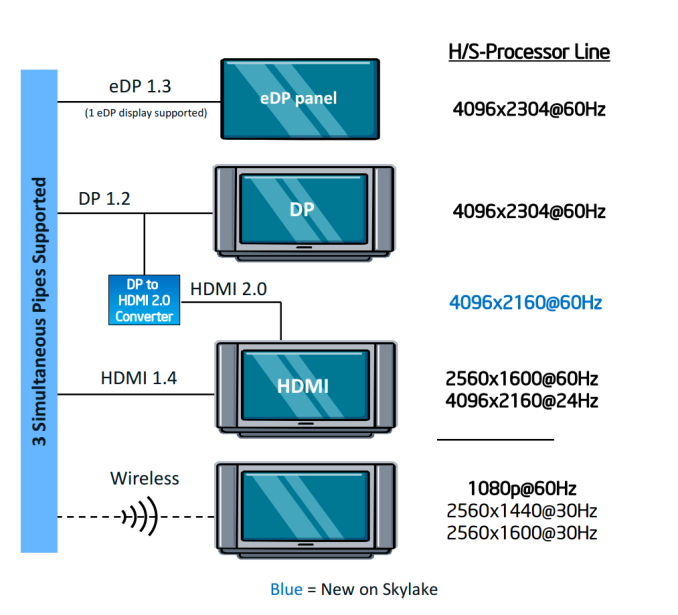

HDMI 2.0 is not supported by default, and only the following resolutions are possible on the three digital display controllers:

A DP to HDMI 2.0 converter, specifically an LS-Pcon, is required to do the adjustments, be it on the motherboard itself or as an external adapter. We suspect that there will not be many takers buying a controller to do this, given the capabilities and added benefits listed by the Alpine Ridge controller.

477 Comments

View All Comments

medi03 - Thursday, August 6, 2015 - link

Yeah. Blaming Intel that HP didn't want to use FASTER AMD CPUs FOR FREE, fearing Intel's illegal revenge is just nuts.AMD Athlon 64's beat Intel in all regards, they were faster, cheaper and less power hungry. Yet Intel was selling several times more Prescotts,

Not being able to profit even in a situation when you have superior product (despite much modest R&D budget), yeah, why blame intel.

MrBungle123 - Sunday, August 9, 2015 - link

In the Athlon 64 days, yes, AMD had a better product but the cold hard truth behind the curtain was that AMD didn't have the manufacturing capacity to supply everyone that Intel was feeding chips to.silverblue - Thursday, August 6, 2015 - link

A "tweaked 8-core Ph2"? Putting aside the fact that significant changes would've been required to the fetch and retire hardware (the integer units themselves were very capable but were underutilised), a better IMC and all the modern instruction sets that K10 didn't support, AMD had already developed its replacement. It probably would've buried them to have to shelve Bulldozer (twice, it turns out) and redevelop what was essentially a 12-year old micro-architecture.AMD were under pressure to deliver Bulldozer hence the cutting of corners and the decision to go with GF's poor 32nm process as they simply didn't have any alternative (plus I imagine they were promised far more than GF could deliver). Phenom II was not enough against Nehalem, let alone Sandy Bridge.

Blaming Intel doesn't help either as AMD couldn't exactly saturate the market with their products even when they were fabbing them themselves, however I think the huge drop in mainstream CPU prices when Core 2 was released along with the huge price paid for ATi did more damage than any bribing of retailers and systems manufacturers.

nikaldro - Wednesday, August 5, 2015 - link

40% over excavator, with 8 cores, good clockspeeds and good pricing doesn't sound that bad. I'll wait till Zen comes out, then decide.Spoelie - Thursday, August 6, 2015 - link

IPC difference between piledriver and skylake amounts to 80%... Lets hope excavator's IPC is better than anticipated and 40% is sandbagging it a bit.Given AMD's track record of overpromising and underdelivering, I'm afraid Zen will massively disappoint.

Asomething - Thursday, August 6, 2015 - link

Well it will only be behind by something like 15-25% if the difference between piledriver and skylake is 80% since piledriver to excavator is supposed to be a good 20% jump. If amd can manage to catchup in any meaningful way and make chips that can touch 5ghz then things might turn out ok.mapesdhs - Thursday, August 6, 2015 - link

Catchup will not be good enough. They need to be usefully competitive to pull people away from Intel into a platform switch, especially business, who have to think about this sort of thing for the long haul, and AMD's track record has been pretty woeful in this regard. I hope they can bring it to the table with Zen, but I'll believe it when I see it. Highly unlikely Intel isn't planning to either splat its prices or shove up performance, etc., if they need to when Zen comes out, especially for consumer CPUs. We know what's really possible based on how many cores, TDP, clock rates, etc. are used for the XEONs, but that potential just hasn't been put into a consumer chip yet.Remember, Intel could have released an 8-core for X79, but they didn't because there was no need; indeed the 3930K *is* an 8-core, just with 2 cores disabled (read the reviews). Ever since then, again and again, Intel has held back what it's perfectly capable of producing if it wanted to. The low clock of the 5960X is yet another example, it could easily be much higher.

MapRef41N93W - Friday, August 7, 2015 - link

You're assuming it's going to be a flat 40% over Excavator and not a best case scenario 40% (like every single AMD future performance projection always is...). It's more than likely a flat 20% IPC increase which puts it even behind Nehalem IPC wise.Top off the fact that it's AMD's first FinFET part (look at the penalty Intel paid in clockspeed with the transition to FinFET with IB/HW) and a transition to a new scalable uARCH (again look at the clockspeed hit Intel took when going from Netburst to scalable core arch, very similar to what AMD is doing now actually) and I can see Zen parts clocking horribly on top of that. Being on a Samsung node that is designed with low power in mind won't help their case either.

You may get an 8 core Zen part for $300-$400 but it probably won't clock worth a damn and end up at 3.5-4GHz on average. So it would be a much worse choice than a 5820k for most people.

mapesdhs - Wednesday, August 12, 2015 - link

Btw, I wasn't assuming anything about Zen, I really haven't a clue how it'll compare to Intel's offerings of the day. I hope it's good, but with all that's happened before, I hope for the best but expect the worst, though I'd like to be wrong.Azix - Friday, August 21, 2015 - link

You guys are being pretty negative on AMD. AMD tried to do an 8core chip on 32nm, maybe that was their mistake. The market wasn't even ready considering how long that way and where we are now. I do think intel got them pretty badly with their cheatingThe next processors are on a much better process. Based on the process alone we would expect a significant bit more performance than some seem willing to allow. Not to mention the original architecture was designed on a 32nm process. It's no surprise it would fall that far behind intel who is currently on 14nm. As time progresses though, those process jumps will take intel longer and longer. AMD will be much closer. Next year will be the first these two are on the same process (similar anyway). in a long while and it will last till at least 2017. AMD should be able to pick up some CPU sales next year and hopefully return to profitability. Intel also enjoys ddr4 support.

Stop pushing old 32nm architectures and crappy motherboards.