Intel-Micron Share Additional Details of Their 3D NAND

by Kristian Vättö on March 26, 2015 2:20 PM EST

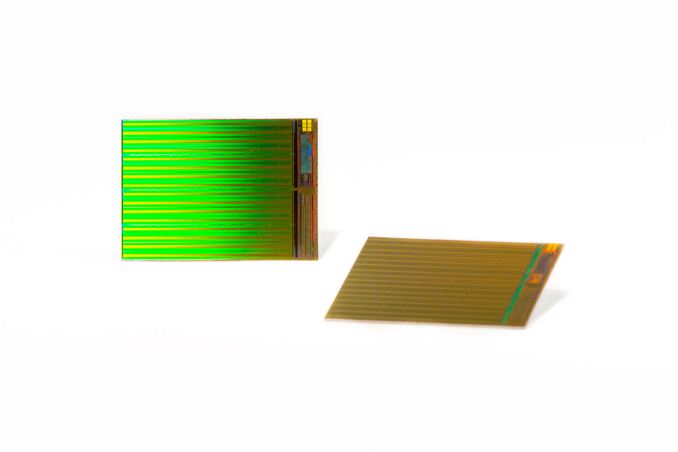

Today must be the busiest day in the world of NAND. Earlier today, Toshiba announced that it has begun sampling of its 48-layer 128Gbit 3D NAND part and now a few hours later Intel and Micron held a joint webinar that revealed a few new details about the companies' 3D NAND process. Intel-Micron originally unveiled their 3D NAND in November last year and disclosed that the first generation product will be a 32-layer 256Gbit (32GB) MLC part, which can also operate in TLC mode to bring the capacity per die to 384Gbit (48GB).

The initial part will be a 4-plane design, which is necessary for retaining high performance at such a high die capacity. For understanding why the number of planes is important, I suggest you read this page from our Crucial M550 review, but in short the number of planes translates to the number of pages that can be programmed in tandem within a single die (i.e. one page can be programmed in one plane at a time, so that's four simultaneous page programs in a 4-plane die). There's some additional latency from multi-plane programming, but with a 4-plane design you can get roughly two times the write (and read/erase too) throughput compared to a 2-plane design. That's a vital element because as the die capacity increases, less die is required to build a drive with fixed capacity (e.g. with 256Gbit die, a 256GB SSD only consists of eight dies, whereas with a 128Gbit die there would be 16 dies operating in parallel).

As I thoroughly explained in our Samsung 850 Pro review, one of the key issues with planar NAND is the shrinking number of electrons. Because 3D NAND can utilize a much larger cell structure due to the fact that scaling is done vertically rather than horizontally, the number of electrons is considerably higher, which improves both endurance and performance. The slide Intel and Micron shared shows that their 3D NAND will have roughly the same number of electrons as their 50nm process did (or actually slightly more), which is over a tenfold improvement compared to the latest 16nm node. The companies weren't willing to share the exact lithography that's used for manufacturing, but I was told that the process relies on single patterning and thus I would estimate the lithography to be somewhere between 35nm and 50nm given the limits of argon fluoride patterning. Ultimately the lithography on its own is rather useless anyway because it only measures the smallest pitch in the die and there's more than a couple of pitches that need to be known for any accurate analysis.

In terms of endurance, Micron told me that the parts will initially be rated at 3,000 P/E cycles. That may sound low, but Micron explained that the reason behind this is that all Micron's client-grade MLC has been rated at 3,000 for several years now and frankly that's more than enough for client applications. Both companies are confident that their 3D NAND technology is capable of delivering far more than that, but as validation takes time and money the first batch won't be rated at more than 3,000 cycles. It will be interesting to see what the enterprise-focused 3D NAND is rated at once it arrives to the market, but given the increased number of electrons and other endurance improvements it's safe to assume that Intel-Micron's 3D NAND will be capable of +10,000 P/E cycles as the process matures.

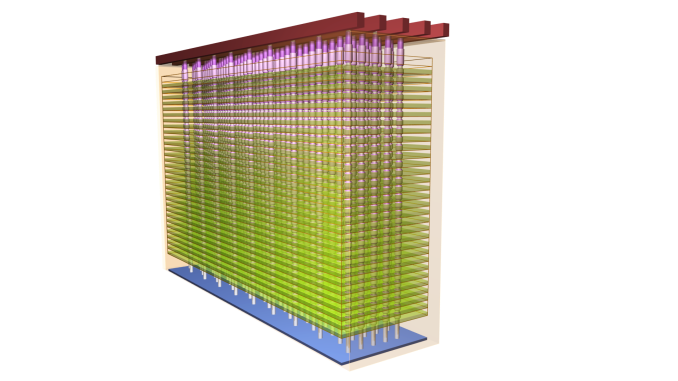

The companies also shared some high-level details of their 3D NAND structure, which has remained a secret until now. To be honest, the above illustration I was given is far from easy to understand (even the Intel/Micron engineers I talked had trouble understanding it), but what I was able to understand is that the purple tubes are the channels and the individual cells are between the channels and the green wordline (i.e. the actual cells are not really shown in the picture). Obviously, the graphs leave many questions unanswered (like how a single cell is accessed and where and how the wordlines are connected), so we'll have to wait for further details before we can fully understand how the structure differs from Samsung's and Toshiba-SanDisk's.

That said, Intel-Micron did disclose that their design utilizes a traditional floating gate, whereas the other 3D NAND designs we have seen use a newer charge trap technology. There's inherently several benefits to charge trap (e.g. less electron leakage), but Intel and Micron told me that they decided to use floating gate because it's a decades old design and the physics are well known, while charge trap is much newer and more unproven. It's impossible to outright say that one cell structure is better than the other because in the end it all boils down to cost where floating gate design is probably more cost efficient for Intel-Micron given their deep knowledge of its functionality.

All in all, we now know a few more bits about Intel-Micron's 3D NAND, but there's still lots of details to be unveiled and investigated to fully understand the differences to other 3D NAND technologies. 256Gbit MLC samples are now shipping to select customers and mass production will begin in the second half of this year, so the first products with Intel-Micron 3D NAND will likely hit the shelves in the first half of 2016.

34 Comments

View All Comments

jjj - Thursday, March 26, 2015 - link

"Toshiba announced that it has begun shipments "Tosh said they are sampling not shipping and Sandisk said "Pilot production will commence as planned in the second half of 2015 in the Yokkaichi joint venture facility, with meaningful commercial production targeted for 2016."

"It's impossible to outright say that one cell structure is better than the other because in the end it all boils down to cost where floating gate design is probably more cost efficient for Intel-Micron given their deep knowledge of its functionality."

Charge trap is supposed to be more cost effective and reliable so your statement seems a bit misleading. Maybe they couldn't figure out charge trap or maybe they decided to not risk failing at it but it seems unlikely that they went this way for better costs.

menting - Thursday, March 26, 2015 - link

more cost effective and more reliable might be true for the long term, but it's possible Micron/Intel wasn't willing to take that risk on a their gen 3D NAND.jjj - Thursday, March 26, 2015 - link

Yeah and i actually mention that but the statement suggests that floating gate was likely cheaper and that seems baseless.Kristian Vättö - Thursday, March 26, 2015 - link

I haven't read anything that would indicate charge trap being more cost effective in general. From a manufacturing standpoint it might be, but once you take all the years of R&D into account the equation is no longer that simple. I didn't say floating gate is generally cheaper, but that it was likely more cost effective for Intel and Micron, which I would say is quite obvious because they did consider other structures too and I'm sure they also did the financial estimations that lead to floating gate being the chosen one.jjj - Thursday, March 26, 2015 - link

Unless they did it to mitigate risks (Intel is not the one to take risks) or this was plan B.You assume cost was the primary factor but we all know that's not always the case.Kristian Vättö - Friday, March 27, 2015 - link

From a finance perspective, risk has a monetary value as well. It may result in higher profit, but it may also result in loss. It sounds reasonable that Intel-Micron decided to play safe and use a well known cell structure because going with an alternative structure was likely too risky and hence possibly higher cost as well (when considering the development cost, that is).MRFS - Thursday, March 26, 2015 - link

Whereupon we repeat once again our ill-fated proposal of a new storage metric:HOW LONG DOES IT TAKE TO READ THE ENTIRE DEVICE JUST ONCE? e.g.

4TB / 200MBps (HDD) = ~5.6 hours, 10TB / 600MBps (SSD) = ~4.6 hours

"There is no oligopoly here," declared the church mouse.

"Just the very same 3D announcements on the very same day," replied the Choir Master. :)

Hulk - Thursday, March 26, 2015 - link

3000 P/E cycles for MLC or TLC?sharath.naik - Thursday, March 26, 2015 - link

After the experience I had with Intel 320 SSD, I am not sure about Intel's reliability. They kept saying they fixed the bricking for their SSD and it still does.toyotabedzrock - Thursday, March 26, 2015 - link

I think you have a minor case of color blindness given your description of the diagram.