Intel’s Core M Strategy: CPU Specifications for 9mm Fanless Tablets and 2-in-1 Devices

by Ian Cutress on September 5, 2014 11:30 AM EST

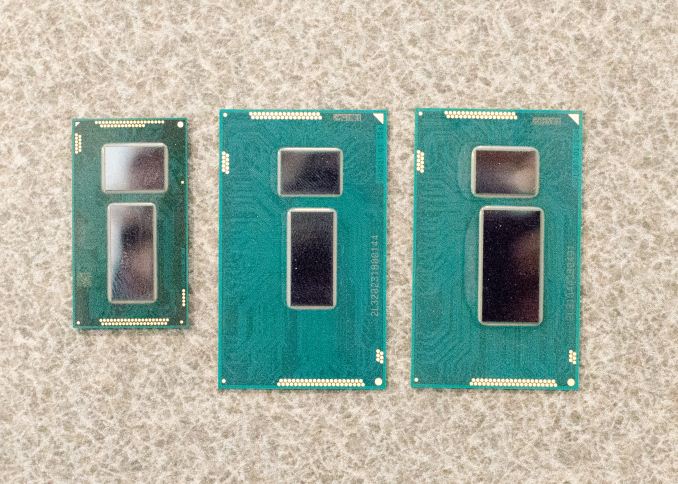

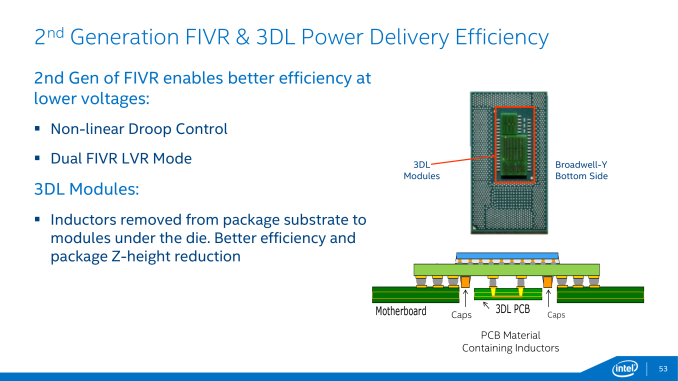

Continuing our coverage of Intel’s 14nm Technology, another series of press events held by Intel filled out some of the missing details behind the strategy of their Core M platform. Core M is the moniker for what will be the Broadwell-Y series of processors, following on from Haswell-Y, and it will be the first release of Intel’s 14nm technology. The drive to smaller, low powered fanless devices that still deliver a full x86 platform as well as the performance beyond that of a smartphone or tablet is starting to become a reality. Even reducing the size of the CPU package in all dimensions to allow for smaller devices, including reducing the z-height from 1.5mm to 1.05 mm is part of Intel’s solution, giving a total die area 37% smaller than Haswell-Y.

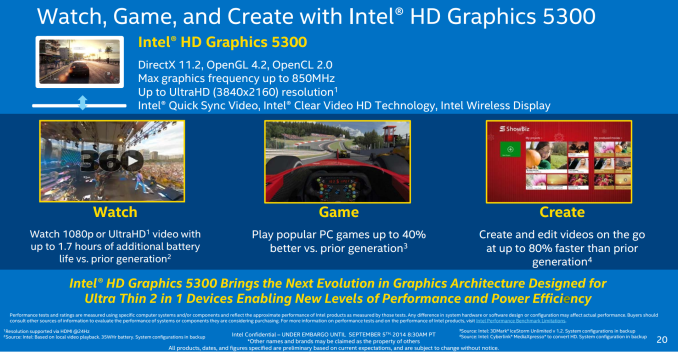

The first wave of three Core M parts will all be dual core flavors, with HD 5300 graphics and all within a 4.5W TDP. For Core M Intel is no longer quoting the SDP terminology due to the new design.

| Intel Core M Specifications | |||

| Core M-5Y70 | Core M-5Y10a | Core M-5Y10 | |

| Cores / Threads | 2 / 4 | 2 / 4 | 2 / 4 |

| Base Frequency / MHz | 1100 | 800 | 800 |

| Turbo Frequency / MHz | 2600 | 2000 | 2000 |

| Processor Graphics | HD 5300 | HD 5300 | HD 5300 |

| IGP Base Frequency / MHz | 100 | 100 | 100 |

| IGP Turbo Frequency / MHz | 850 | 800 | 800 |

| L3 Cache | 4 MB | 4 MB | 4 MB |

| TDP | 4.5 W | 4.5 W | 4.5 W |

| LPDDR3/DDR3L Support | 1600 MHz | 1600 MHz | 1600 MHz |

| Intel vPro | Yes | No | No |

| Intel TXT | Yes | No | No |

| Intel VT-d/VT-x | Yes | Yes | Yes |

| Intel AES-NI | Yes | Yes | Yes |

The top of the line processor will be called the Core M-5Y70, which is a bit of a mouthful but the name breaks down similarly to Intel’s main Core series. ‘5’ is similar to i5, giving us a dual-core processor with Hyper-Threading; ‘Y’ is for Broadwell-Y; and ‘70’ gives its position in the hardware stack.

The CPU will leverage both processor graphics and CPU Turbo Boost, allowing each of them to turbo at different times and different rates depending on the workload and overall power usage. Of particulary interest is that the 5Y70 features a base clock of 1.1 GHz, with turbo for both single-core and dual-core use listed as up to 2.6 GHz. The new HD 5300 GPU similarly has a 100 MHz base frequency with an 850 MHz turbo. The 5Y70 is different from the other two models in both clock speeds and features, as it will be part of Intel’s vPro program and also supports Intel TXT.

The other two processors in the stack are the 5Y10a and 5Y10, with dual-core + HT configurations and 800 MHz base frequency with turbo up to 2.0 GHz. There doesn't appear to be any major difference between the two parts, though Intel's presentation notes that the 5Y10 supports "4W Config Down TDP" (cTDP Down). The graphics is clocked slightly lower on the turbo, giving 800 MHz.

It's interesting to note that Intel informed us that the 1k unit pricing will be the same for all three processors: $281. Obviously these chips are going to end up in hybrids, tablets, and laptops that come pre-built, so the actual pricing will vary by OEM and whatever deals they have with Intel. But in general, Intel seems to be saying that OEMs can choose any of the three chips based on their power/thermal targets.

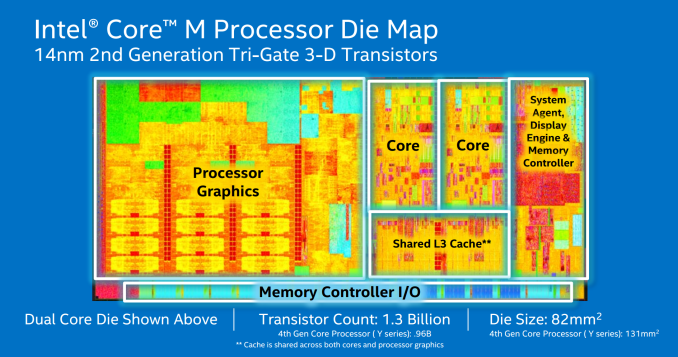

The HD Graphics 5300 is the new processor graphics and as part of the brief behind Core-M, a die shot was supplied with the important areas marked:

In the processor graphics section in the shot above, there clearly looks like 12 repeated units, with each representing two EUs (Execution Units). In our dive into the architecture in early August, it was stated that the minimum configuration here would be as a result of Broadwell taking 8 EUs per sub-slice, with the minimum configuration being three sub-slices, making 24 in total. This comes in combination with an increase in the L1 cache and samplers relative to the number of EUs, allowing for 25% more sampling throughput per EU.

| Intel's Tick-Tock Cadence | |||||

| Microarchitecture | Process Node | Tick or Tock | Release Year | ||

| Conroe/Merom | 65nm | Tock | 2006 | ||

| Penryn | 45nm | Tick | 2007 | ||

| Nehalem | 45nm | Tock | 2008 | ||

| Westmere | 32nm | Tick | 2010 | ||

| Sandy Bridge | 32nm | Tock | 2011 | ||

| Ivy Bridge | 22nm | Tick | 2012 | ||

| Haswell | 22nm | Tock | 2013 | ||

| Broadwell | 14nm | Tick | 2014 | ||

| Skylake | 14nm | Tock | 2015 | ||

The fundamental architecture of the GPU does not change from Haswell, albeit on a smaller process node. The GPU is confirmed as supporting DirectX 11.2, OpenGL 4.2 and OpenCL 2.0, with UltraHD (3840x2160) supported at 24 Hz through HDMI. This opens up possibilities of fanless tablets with UHD panels.

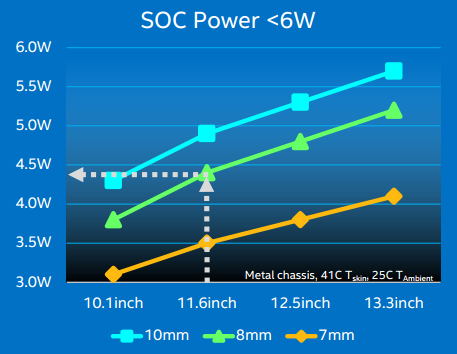

One of the main graphs Intel was pushing in their briefing was this one, indicating what power is required for a fanless tablet:

For a chassis of 7, 8 or 10mm, to have a maximum skin temperature of 41C at load, the above TDPs are required depending on the chassis size in order to go fanless. The first batch of 4.5W Core M processors aim at either the 11.6-inch, 8mm thick fanless tablet design as indicated in the graph above, or similarly a 10.1-inch 10mm thick tablet will also be suitable. Intel wants Core M to have a range of possible TDPs based on increasing or decreasing the frequency as required for a thin fanless tablet.

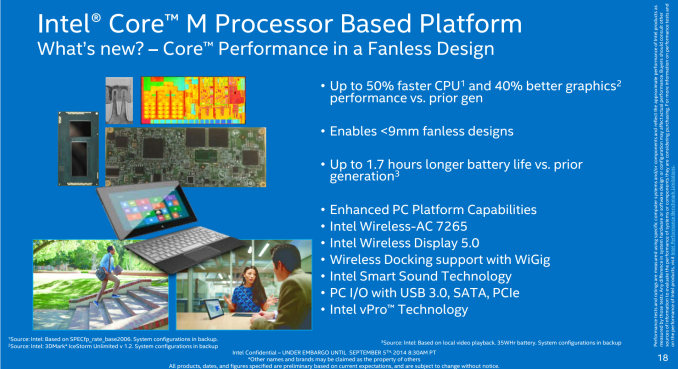

Intel is going to support extended docking functionality, especially with its business partners to allow features such as WiGig and additional I/O. Intel is also bringing a new 802.11ac design in the form of AC 7265, a lower powered version of the 2T2R 7260 for tablets. This will also support WiDi 5.0, and overall the platform aims to offer 1.7 hours longer battery life. Intel got to this ‘+1.7’ hour number with a reference design compared to a clocked-down Haswell-Y. I would like to point out that despite these numbers, a clocked-down part usually represents moving outside the optimal efficiency window, especially when dealing with low powered tablets.

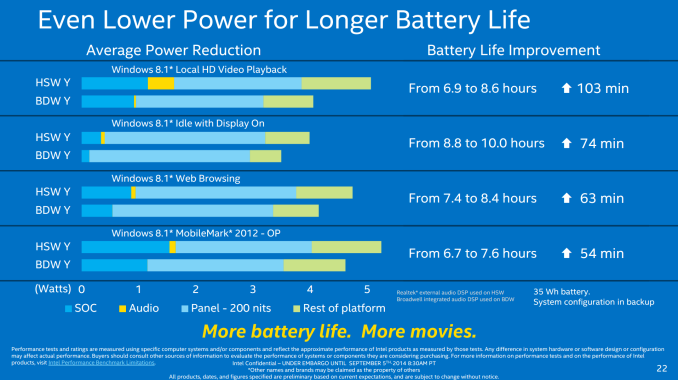

Intel used the above slide in their presentations and drew particular attention to the power consumption of the audio during HD video playback (the orange bar on the top comparison). As part of Core M, Intel is reducing power consumption of the audio segment of the system from 100s of milliwatts down to single-digit milliwatts by integrating an audio digital signaling processor (DSP) onto the die. This is what Intel refers to as its Smart Sound Technology, and is designed to shift the majority of the audio processing onto a configured part of the die which can process at lower power.

If you think you’ve heard of something like this before, you have: AMD’s TrueAudio sounds remarkably similar in its implementation and its promotion. We asked Intel if this new DSP for Broadwell would have a configurable API similar to TrueAudio, however we are still waiting on an official response to this.

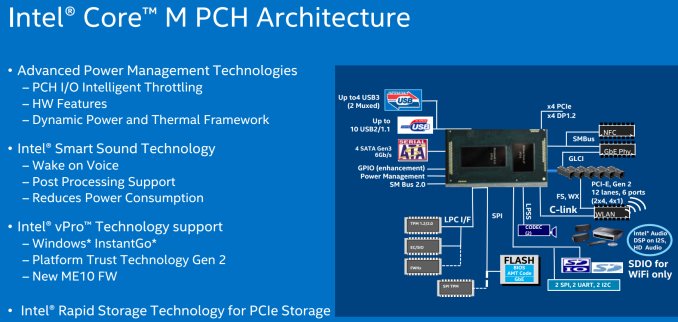

The platform controller hub layout was also provided, showing USB 3.0 support along with SATA 6 Gbps and four lanes of PCIe:

The PCH is also designed to be dynamic with power, meaning that disabling features on a design could yield a better-than-expected increase in battery life. The design will support NFC, and it is worth noting that the two USB 3.0 ports are in a mux configuration which may limit bandwidth. With a number of PCIe lanes in tow however, there are a number of controllers that could be used to expand functionality in a design.

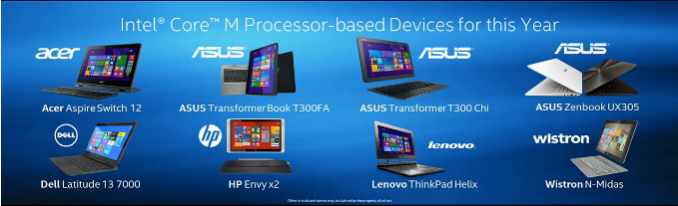

Intel will be showing off the Core M at IFA in Berlin this week, with over 20 designs based on Core M from OEMs in the known pipeline – including designs like ASUS’ Transformer Book T300 Chi announced back at Computex. The T300 Chi was specified as a 12.5-inch fanless tablet in a 7.3mm thickness design, with LTE support and a 2560x1600 display. With the 12.5-inch size and 7.3mm width, it sounds like the T300 Chi will be modifying the Core M CPU to be around 4W in order to keep the 41C skin temperature as a maximum. Intel also listed the following Core M devices at IFA:

The CPUs will be in volume production before the end of the year (we seem to have differing reports whether volume production has started already or is just about to), with systems from ~5 OEMs available in Q4, starting in late October. Intel lists both consumer and business designs for this timeframe, however volume production is expected in Q1 2015.

115 Comments

View All Comments

Wolfpup - Monday, September 8, 2014 - link

I'm baffled by all these comments that don't seem impressed by this and seem to think 28nm phone chips are in some way comparable to 14nm chips based on Intel's latest and greatest :-OAlexey291 - Thursday, September 11, 2014 - link

Considering how badly intel has been doing in the mobile space I'm not baffled by these comments at all.And given the price of these chips I'm not seeing them sell any significant quantity.

fteoath64 - Tuesday, September 9, 2014 - link

"interesting to see these tested against Intel Atoms." These parts are clocked at 800Mhz at 4.5w with 2 cores : the BayTrial clocked at 2Ghz with 4 cores at 10w. Granted the gpu of BT is just poor compared to GT3e in these chips. ie 40EUs with eDram. SO on cpu, the BT would be 40% as fast approx.ArthurG - Friday, September 5, 2014 - link

Dear Yan,it's a nice article but reality is a bitch. These "wonderful" (irony) products are already end of life !!!

see here: http://qdms.intel.com/dm/d.aspx/824A06BE-D3AD-47AC...

this Product Change Notification document states that you can't order these models after September 26 !!! The official reason is that the market moved to other products ; politically correct way to say that nobody wants it !!!

harpocrates - Friday, September 5, 2014 - link

Intel is releasing a new Core M stepping to fix the TSX bug:http://www.kitguru.net/components/cpu/anton-shilov...

MartinT - Friday, September 5, 2014 - link

Are you sure the F stepping is supposed to fix that bug? Seems awfully early for a fix to be in production so soon after the public acknowledgement of the bug.harpocrates - Friday, September 5, 2014 - link

I'm not 100% sure but it's what been reported at the moment.From Techreport: "Intel has a fix in the works for Broadwell's next stepping. We don't yet know when Broadwell production will transition to the new stepping or how prevalent the TSX erratum will be among the first wave of Broadwell-based systems."

http://techreport.com/news/26911/errata-prompts-in...

extide - Friday, September 5, 2014 - link

No, it's because the 14nm process delays caused this launch to get delayed so far back that it's almost time for skylake to come out.Krysto - Saturday, September 6, 2014 - link

For real.Shadowmaster625 - Friday, September 5, 2014 - link

4.5W in a 7" device? OK Intel, now take a rockchip ARM SoC and one of your tiny modems and stick them in there and make me a dual boot device. Better yet, just add the modem and the ARM cores to the broadwell SoC. Get rid of some of those EUs because lets face it, you just cant use that many at that TDP. Imagine Android + windows all from one SoC. Intel already has everything they need to do it, except for the desire to make money, apparently.