MIPS Strikes Back: 64-bit Warrior I6400 Arrives

by Stephen Barrett on September 2, 2014 10:00 AM ESTMIPS Instruction Set: 64-bit Release 6

Computer processors accomplish tasks by following instructions. The processor, however, only understands instructions in a specific "language". The language of a processor is called its Instruction Set Architecture (ISA). The code sent to a processor must be in that ISA to be understood. It's similar to what would happen if someone proceeded to give me instructions in Portuguese: I unfortunately would have no idea how to execute them. When a program or operating system is authored and compiled, the compiler is parameterized to generate the 1s and 0s of binary code using a specific ISA.

In general, there are two types of ISAs. Complex Instruction Set Computing (CISC) and Reduced Instruction Set Computing (RISC). The difference between them being of course their relative complexity. In general, a RISC ISA contains significantly fewer instructions that are far simpler than a CISC ISA.

Despite its increased complexity, CISC actually predates RISC and was only named retroactively. CISC ISAs were a necessity when low level code (assembly) was often authored by hand, and compilation was crippled by dramatically less powerful compilers than those available today. Having higher level instructions in the ISA, such as looping, allowed simple compilers to extract sufficient performance and human assembly authors to write programs. The most popular CISC ISA ever written is the x86 ISA used in Intel, AMD, and VIA processors. Interestingly, these processors now use dedicated decoding hardware to actually translate CISC instructions into RISC instructions that are executed internally.

RISC ISAs push much of the instruction complexity into the code compiler. Instead of using instruction decode circuits inside the CPU core to translate complex instructions into simple ones, RISC processors operate directly on the simple instructions provided by the compiler. This benefit is somewhat offset as often code compiled for RISC ISAs is larger; it may take multiple RISC instructions for the equivalent CISC instruction. This holds true in computer science theory, as one of the first things taught is there is often a tradeoff between storage and efficiency. If there is a desire for increased efficiency, precompute items ahead of time and then store them. If you need to save storage (or reduce the memory footprint), compute items on-the-fly.

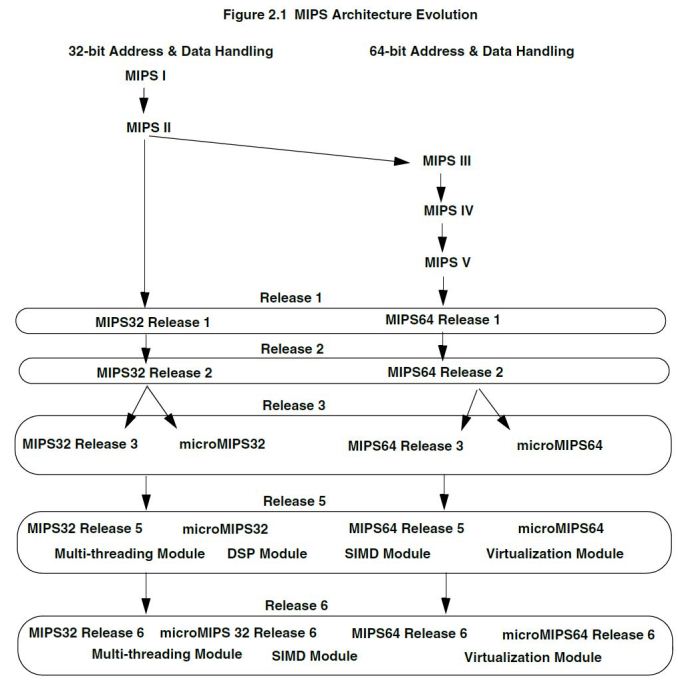

The most popular RISC ISA ever written is the ARM ISA. The MIPS ISA, like ARM, is RISC. It has been revised several times since its inception in 1985. The first five releases are named according to roman numerals I through V, and each was a super set of the last. In 1999, MIPS announced a large revision of the ISA which deprecated the old hierarchical I through V scheme and instead focused on two ISAs: MIPS32 and MIPS64.

Release 6 occurred in 2014 and the I6400 is the first CPU utilizing the new ISA. I won’t go through all the changes in the ISA, but the most significant is a culling of the instructions. Significant work was done to simplify the ISA by removing infrequently used instructions, in particular those that overlapped with Imagination’s PowerVR GPUs. Additional instructions were also added specifically targeting today’s applications like web browsers. The fruit of these instructions has recently been seen as Google Chrome’s V8 rendering engine added experimental support for MIPS64 release 6 in July.

In the MIPS programmer’s guide the release 6 ISA is actually referred to as MIPS3264 release 6. This naming is not by accident, as MIPS64 ISA is actually a direct superset of the MIPS32 ISA. In contrast to AMD64 (x86-64), there are no "operating modes" that dictate the bitness of instructions executed on the CPU but rather an entirely new set of instructions specifically for 64-bit. Registers inside the CPU are all 64bit, and when a 32-bit instruction executes, results saved in registers are sign-extended to the entire 64-bits of space. This means there is no mode switching, and 32-bit and 64-bit applications can coexist and even be executed using the same hardware resources like registers (more on this later).

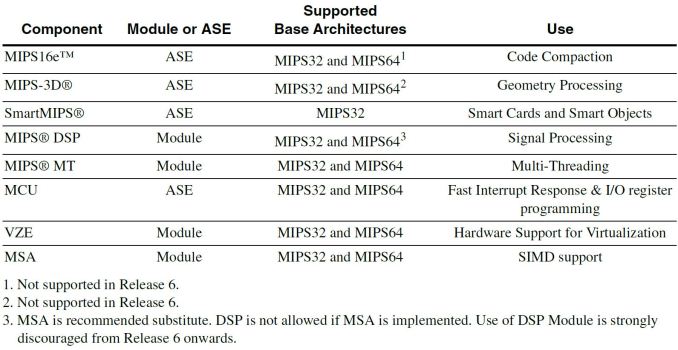

The MIPS ISA contains several optional instructions called Application Specific Extensions. These rely on optional portions of the CPU core that a licensee may or may not implement. Additionally, a MIPS CPU has optional modules that can enhance performance when paired with certain instructions.

Release 6 drops the legacy MIPS16e ASE as well as the redundant 3D ASE now that Imagination offers GPUs alongside MIPS CPUs.

MIPS CPUs in Mobile Devices

While MIPS CPUs are quite popular in networking equipment and many other embedded industries, consumers will likely only experience one firsthand when it's integrated into an Android handset. Since Android 4.0, Google has supported three ISAs: x86, ARM, and MIPS. Several devices have shipped running MIPS processors, most notably the low-cost Novo 7 tablet. MIPS devices will continue to be low cost alternative devices for now, but low cost devices have the largest volume. The volume should eventually help MIPS push app developers to address their #1 problem: compatibility.

Android applications are either written in Java, then compiled on the device to the specific required ISA before running (a processes called JIT compilation), or written in the Android Native Development Kit (NDK) to target a specific ISA. Apps written in Java can therefore run on any ISA that Android itself supports, including MIPS. Apps written with the NDK (many of which exist, especially games) cannot run on anything but the specific ISA they were written for. The Android NDK does allows packaging multiple ISA specific binaries into a single app, but with the vast majority of Android devices using ARM processors and therefore the ARM ISA, a multiple NDK Android app is simply uncommon.

What does this mean for an end user? There are many Android apps that simply won’t run if you have a MIPS processor in your device. Intel has the same NDK compatibility problem, but with their considerably larger engineering resources, Intel implemented a layer that translates ARM ISA applications to the Intel x86 ISA (albeit at a performance penalty). Until MIPS implements the same or ships enough volume to convince Android app developers to put in some extra work, a MIPS Android device will unfortunately be a second class experience.

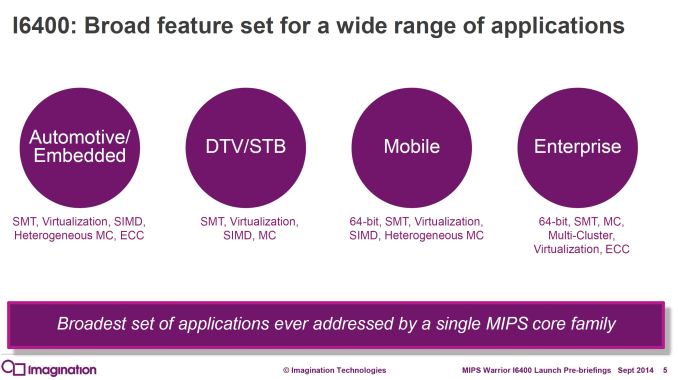

Despite some existing Android app compatibility woes, the MIPS I6400 CPU contains some interesting technology designed to address many more markets than handsets. In fact, Android usage of MIPS processors is really a minor part of the MIPS business. A few slides from the MIPS announcement indicate just how many other markets they are targeting.

84 Comments

View All Comments

Wilco1 - Tuesday, September 2, 2014 - link

I think name99 is a bit harsh but he has valid points. For example the MIPS CoreMark results use a special plugin that adds a CoreMark specific optimization. So it is misleading to claim a great CoreMark result.Now if this optimization was added to mainline and also enabled when benchmarking the "competitor" then it would be a fair comparion.

mthrondson - Sunday, September 7, 2014 - link

I'm not familiar with this special plug in. Can you elaborate?Samus - Wednesday, September 3, 2014 - link

MIPS has always been superior to ARM in regards to "performance per watt" even dating back to the PocketPC day's (1997) but its success has always suffered because of architecture complexity. You might as well port machine code before you recompile an app from ARM to MIPS.The success of MIPS lies with the quality of the development kits, compilers, and price (which they will apparently be aggressively targeting)

jjj - Tuesday, September 2, 2014 - link

Interesting but will be hard for them to get big wins in mobile (the main SoC anyway). Even if they try to be cheaper , how much cheaper do they need to be to justify the compatibility issues.A note here, you look at the competition between ISAs but don't forget that we got a bunch of custom ARM cores too so for consumers it's even more fun.

Also the Meizu MX4 launched today ,first device with the quad A17 Mediatek so a notable event.Haven't really seen any proper benchmarks for A17 yet ,hopefully soon.

alexvoica - Tuesday, September 2, 2014 - link

The compatibility issue is going away fast. MIPS64 is a proven architecture that has a full ecosystem built around it, while others are still catching up. Additionally, 64-bit is an inflection point where a lot of software will need to be recompiled so a lot of people are actually starting from scratch.evolucion8 - Tuesday, September 2, 2014 - link

While I am in love with ARM, I look forward for MIPS too!Notmyusualid - Tuesday, September 2, 2014 - link

The more competition, the better...Wilco1 - Tuesday, September 2, 2014 - link

There is no requirement to recompile anything but the OS - existing apps continue to run in 32-bit without a penalty.alexvoica - Wednesday, September 3, 2014 - link

There is a requirement if you want your software to take advantage of the latest architectural improvements. If you don't, it will still run, yes - but not as fast/efficiently as it could.bleh0 - Tuesday, September 2, 2014 - link

I have to say from a feature standpoint this seems far more interesting then A53. I just doubt that by this time next year we will actually see it in devices.