The 2013 MacBook Air Review (13-inch)

by Anand Lal Shimpi on June 24, 2013 12:01 AM ESTA Custom Form Factor PCIe SSD

In the old days, increasing maximum bandwidth supported by your PATA/SATA interface was always ceremonial at first. Hard drives were rarely quick enough to need more than they were given to begin with, and only after generations of platter density increases would you see transfer rate barriers broken. Then came SSDs.

Not only do solid state drives offer amazingly low access latency, but you can hit amazingly high bandwidth figures by striping accesses across multiple NAND Flash die. A 256GB SSD can be made up of 32 independent NAND die, clustered into 8 discrete packages. A good controller will be able to have reads/writes in flight to over half of those die in parallel. The result is a setup that can quickly exceed the maximum bandwidth that SATA can offer. Today that number is roughly 500MB/s for 6Gbps SATA, which even value consumer SSDs are able to hit without trying too hard. Rather than wait for another rev of the SATA spec, SSD controller makers started eyeing native PCIe based controllers as an alternative.

You can view a traditional SSD controller as having two sides: one that talks to the array of NAND flash, and one that talks to the host system’s SATA controller. The SATA side has been limiting max sequential transfers for a while now at roughly 550MB/s. The SATA interface will talk to the host’s SATA interface, which inevitably sits on a PCIe bus. You can remove the middle man by sticking a native PCIe controller on the SSD controller. With SATA out of the way, you can now easily scale bandwidth by simply adding PCIe lanes. The first generation of consumer PCIe SSDs will use PCIe 2.0, since that’s what’s abundant/inexpensive and power efficient on modern platforms. Each PCIe lane is good for 500MB/s, bidirectional (1GB/s total). Apple’s implementation uses two PCIe 2.0 lanes, for a total of 1GB/s of bandwidth in each direction (2GB/s aggregate).

The move to a PCIe 2.0 x2 interface completely eliminates the host side bottleneck. As I pointed out in my initial look at the new MacBook Air, my review sample’s 256GB SSD had no problems delivering almost 800MB/s in peak sequential reads/writes. Do keep in mind that you’ll likely see slower results on the 128GB drive.

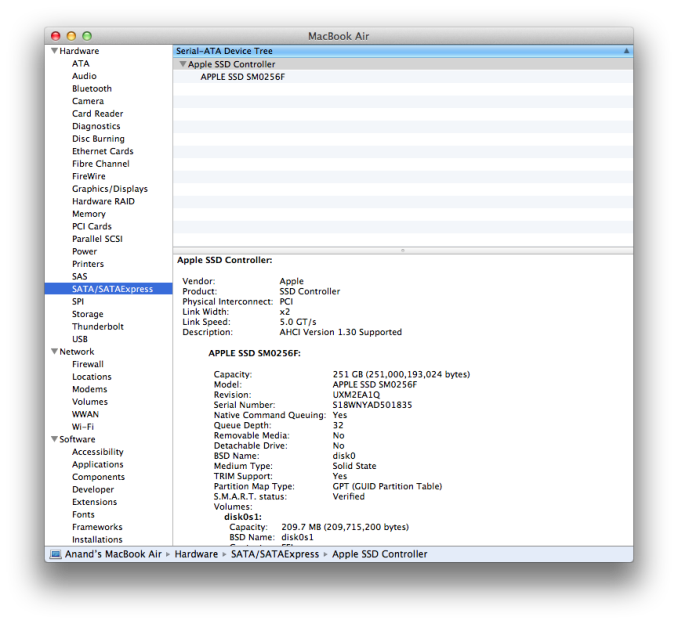

Users have spotted both Samsung and SanDisk based PCIe SSDs in the 2013 MacBook Airs. Thankfully Apple doesn’t occlude the controller maker too much in its drive names. An SM prefix denotes Samsung:

My review sample featured a Samsung controller. There’s very little I know about the new Samsung controller, other than it is a native PCIe solution that still leverages AHCI (this isn't NVMe). Within days of Apple launching the new MBAs, Samsung announced its first consumer PCIe SSD controller: the XP941. I can only assume the XP941 is at least somewhat related to what’s in the new MBA.

The Samsung controller is paired with a 512MB DDR3 DRAM and 8 Samsung 10nm-class (10nm - 20nm process node) MLC NAND devices.

New PCIe SSD (top) vs. 2012 MBA SATA SSD (bottom) - Courtesy iFixit

Despite moving to PCIe, Apple continues to use its own proprietary form factor and interface for the SSD. This isn’t an M.2 drive. The M.2 spec wasn’t far enough along in time for Apple to use it this generation unfortunately. The overall drive is smaller than the previous design, partially enabled by Samsung’s smaller NAND packages.

233 Comments

View All Comments

spronkey - Monday, June 24, 2013 - link

Hmm. Very interested to see the CPU and battery life numbers for the i7 upgrade. If it manages to increase performance by 10% or so, and decrease battery life 10% or so, it could be a nice sweet spot.Bkord123 - Tuesday, June 25, 2013 - link

I can't wait for the i7 review. I think it's the once I'm leaning toward getting.timmyj9 - Monday, June 24, 2013 - link

i would be curious to know if the same 802.11ac file sharing bottlenecks occur when using NFS as the file sharing protocol?Kevin G - Monday, June 24, 2013 - link

It would as the tweak to resolve it was made to TCP and modern NFS are built on top of that.Khato - Monday, June 24, 2013 - link

Can't agree more that Haswell battery life is already blurring the lines with current tablets. I'm curious how the 2013 Tablet Bench Web Browsing suite compares specifically to the one used on notebooks? In the details provided in this review the specific frequency of web page loading is specified while it's not in the Tablet version.The iPad 4 with it's 42.5Wh battery and 9.48 hours of run-time in the test draws an average of 4.48W. If that test is comparable to the Light version shown here then you have the Haswell Macbook Air drawing an average of 4.9W, while if it's comparable to the Medium version then the average is 6.05W. Either way, when you consider that the Macbook Air's 13.3" diagonal screen has 1.88x more surface area than the iPad 4 (nit is another term for cd/m^2, so total luminous intensity of a 13.3" screen at 200 nits is 1.88x that of a 9.7" screen at 200 nits) it's pretty much a given that display power for the Macbook Air is higher than for the iPad 4 despite the lower resolution. Pretty cool.

Shivansps - Monday, June 24, 2013 - link

The HD5000 is running on single channel right? there is a 2do slot for another memory?Kevin G - Monday, June 24, 2013 - link

The entire SoC has dual channel memory. The MacBook Air has no memory expansion slots. If you want to get one of these, be sure to order with the amount of memory you think you'd need in the future.Shivansps - Monday, June 24, 2013 - link

Im saying that because of the IGP performance, i cant find any confirmation on the review that the MBA is running on dual channel memory, 4GB LPDDR3 sounds like 64 bit single channel to me, and that will impact IGP performance, even HD3000 has reduced 3D performance if not running on dual channel.Glindon - Monday, June 24, 2013 - link

Every Macbook Air that I've owned ran in dual channel mode. Why would this year's be any different.Kevin G - Monday, June 24, 2013 - link

Note the part in this article referring to the LPDDR3. It indicates that it has four 32 bit LPDDR3 packages which indicate a 128 bit wide bus (dual channel).