Intel's Haswell Architecture Analyzed: Building a New PC and a New Intel

by Anand Lal Shimpi on October 5, 2012 2:45 AM ESTTSX

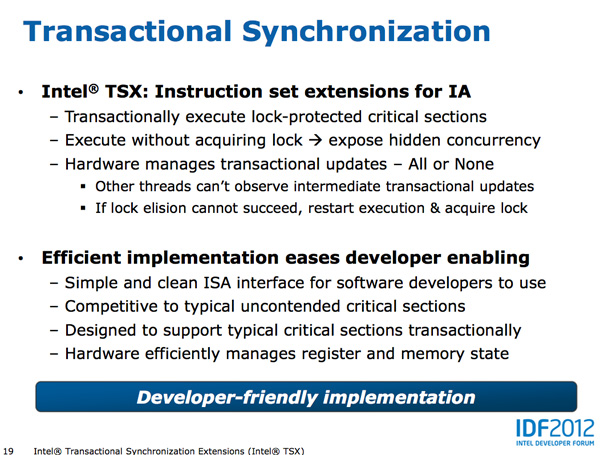

Johan did a great job explaining Haswell's Transactional Synchronization eXtensions (TSX), so I won't go into as much depth here. The basic premise is simple, although the implementation is quite complex.

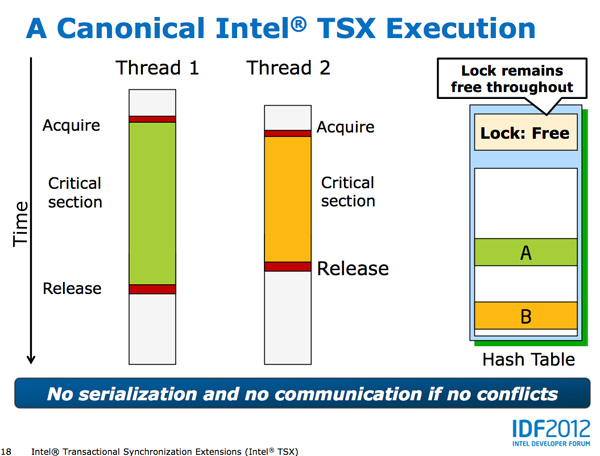

It's easy to demand well threaded applications from software vendors, but actually implementing code that scales well across unlimited threads isn't easy. Parallelizing truly independent tasks is the low hanging fruit, but it's the tasks that all access the same data structure that can create problems. With multiple cores accessing the same data structure, running independent of one another, there's the risk of two different cores writing to the same part of the same structure. Only one set of data can be right, but dealing with this concurrent access problem can get hairy.

The simplest way to deal with it is simply to lock the entire data structure as soon as one core starts accessing it and only allow that one core write access until it's done. Other cores are given access to the data structure, but serially, not in parallel to avoid any data integrity issues.

This is by far the easiest way to deal with the problem of multiple threads accessing the same data structure, however it also prevents any performance scaling across multiple threads/cores. As focused as Intel is on increasing single threaded performance, a lot of die area goes wasted if applications don't scale well with more cores.

Software developers can instead choose to implement more fine grained locking of data structures, however doing so obviously increases the complexity of their code.

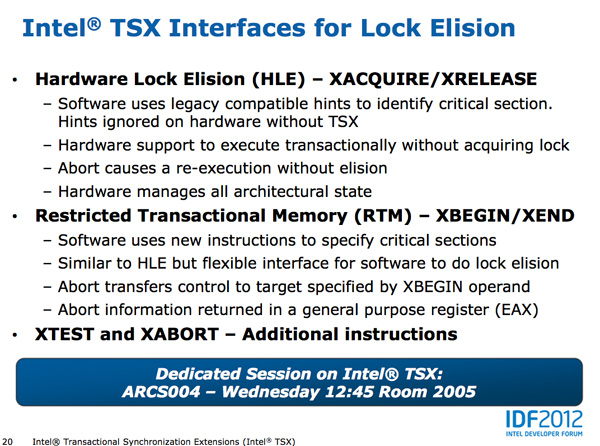

Haswell's TSX instructions allow the developer to shift much of the complexity of managing locks to the CPU. Using the new Hardware Lock Elision and its XAQUIRE/XRELEASE instructions, Haswell developers can mark a section of code for transactional execution. Haswell will then execute the code as if no hardware locks were in place and if it completes without issues the CPU will commit all writes to memory and enjoy the performance benefits. If two or more threads attempt to write to the same area in memory, the process is aborted and code re-executed traditionally with locks. The XAQUIRE/XRELEASE instructions decode to no-ops on earlier architectures so backwards compatibility isn't a problem.

Like most new instructions, it's going to take a while for Haswell's TSX to take off as we'll need to see significant adoption of Haswell platforms as well as developers embracing the new instructions. TSX does stand to show improvements in performance anywhere from client to server performance if implemented however, this is definitely one to watch for and be excited about.

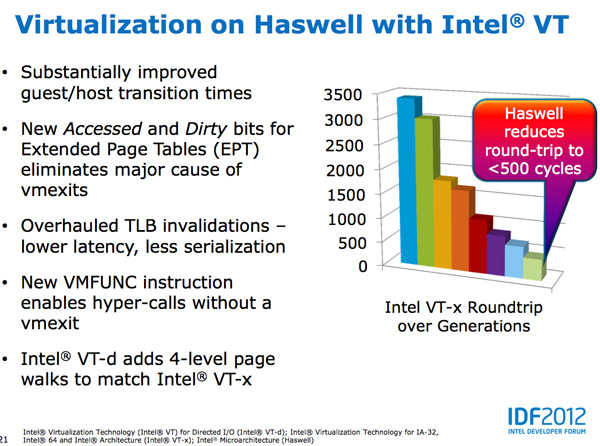

Haswell also continues improvements in virtualization performance, including big decreases to guest/host transition times.

245 Comments

View All Comments

rundll - Friday, October 5, 2012 - link

Four cores and 95 W tdp.What is this?

meloz - Friday, October 5, 2012 - link

Yes this caught my eye and I would like an answer, too.Maybe it is one SKU with GT3 for desktop? Or maybe it is a 6 core part?

Or maybe.....it is the mother of all overclocking processors. Muhahahahah!

Kevin G - Friday, October 5, 2012 - link

I suspect that 95W is the rated socket limit. This is similar to how Intel advertises Ivy Bridge at 77 W on the desktop but tells motherboard manufacturers to build around the higher 95 W figure.What is odd is that Haswell will move some of the VRM circuitry on the package which should restrict just how far off that 95W figure motherboards can deviate.

meloz - Friday, October 5, 2012 - link

What a great article, Anand!Felt so good to read a 'proper' Anandtech article after so long, instead of the usual Apple worship and cheap fillers.

Haswell is looking very good. Would make an ideal upgrade for Sandy Bridge users. AMD is done, but thankfully Intel sees some threat from ARM so that will keep them innovating.

I hope Intel make a sensible choice with Haswell SKUs and get away from their artifical crippling and segmentation tendencies. That's about the only thing that can ruin Haswell.

Wolfpup - Friday, October 5, 2012 - link

Once again they bump up the number of transistors being used on their worthless video-and this time they even lower CPU performance (L3 cache) to appease their worthless video.Interesting article, but I guess I misunderstood previous articles...I thought Conroe through Ivy Bridge had 4 integer execution units per core? (As does Piledriver?)

haukionkannel - Friday, October 5, 2012 - link

Good article and information that you need win 8 to fully utilize Haswell was new information to me. It will be interesting to see how much better Haswell will be with win 8 compared to win 7. Seems to be same kind of dilemma as with AMD Bulldoser/piledriver where there seems to be some kind of better performance with new OS, but how much will reamain to be seen.Belard - Friday, October 5, 2012 - link

Apple owns various CPU tech and design companies such as P.A. Semi. They can build their own CPUs (not x86 of course)...Apple will do what they can to take out the middleman.

jwcalla - Friday, October 5, 2012 - link

Apple doesn't have any fabs though and if Samsung isn't willing to re-sign another contract, they're going to be in a bit of a bind. In other words, it won't be cheap. And even if Samsung does re-up, you can be sure that it'll come with an additional $1.05b price tag to offset any "losses" in their mobile division.I felt the first page overestimated Apple's influence quite a bit. They have ~5% desktop marketshare and 0% in the server space. Not to trivialize any loss in CPU sales, but Intel's primary headwinds don't involve a possible Apple switch to ARM.

Kevin G - Friday, October 5, 2012 - link

Apple's influence comes from the mobile market which is beginning to dwarf the PC market (and is larger than the server market in terms of volume). Apple is the largest tablet maker and a major smart phone manufacturer. There hardware is backed by one of the largest digital media markets. To do this Apple is the worlds largest consumer of flash memory whom orders are large enough to directly affect NAND pricing.With the rest of the industry going ultra mobile, they'll have to compete with Apple who is already entrenched. Sure the PC will survive but mainly for legacy work and applications. Their isn't enough of a PC market in the future to be viable long term with so many players.

jwcalla - Friday, October 5, 2012 - link

While all this is true, the first page seems to indicate that Intel is really pushing the low power envelop partly because of rumors that Apple will move away from Intel chips in their laptop / ultrabook products.While I'm sure Intel is happy to be in MBAs, etc., losing that business isn't going to be as big a deal as the other pressures facing the PC market (as you mention).

Now if WinRT on ultrabooks / laptops began to take off... that would be a huge problem for Intel.