Intel Core i7 3960X (Sandy Bridge E) Review: Keeping the High End Alive

by Anand Lal Shimpi on November 14, 2011 3:01 AM EST- Posted in

- CPUs

- Intel

- Core i7

- Sandy Bridge

- Sandy Bridge E

No Integrated Graphics, No Quick Sync

All of this growth in die area comes at the expense of one of Sandy Bridge's greatest assets: its integrated graphics core. SNB-E features no on-die GPU, and as a result it does not feature Quick Sync either. Remember that Quick Sync leverages the GPU's shader array to accelerate some of the transcode pipe, without its presence on SNB-E there's no Quick Sync.

Given the target market for SNB-E's die donor (Xeon servers), further increasing the die area by including an on-die GPU doesn't seem to make sense. Unfortunately desktop users suffer as you lose a very efficient way to transcode videos. Intel argues that you do have more cores to chew through frames with, but the fact remains that Quick Sync frees up your cores to do other things while SNB-E requires that they're all tied up in (quickly) transcoding video. If you don't run any Quick Sync enabled transcoding applications, you won't miss the feature on SNB-E. If you do however, this will be a tradeoff you'll have to come to terms with.

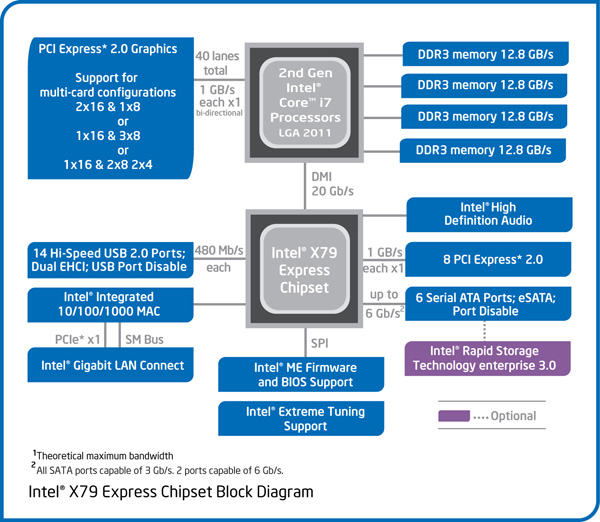

Tons of PCIe and Memory Bandwidth

Occupying the die area where the GPU would normally be is SNB-E's new memory controller. While its predecessor featured a fairly standard dual-channel DDR3 memory controller, SNB-E features four 64-bit DDR3 memory channels. With a single DDR3 DIMM per channel Intel officially supports speeds of up to DDR3-1600, with two DIMMs per channel the max official speed drops to 1333MHz.

With a quad-channel memory controller you'll have to install DIMMs four at a time to take full advantage of the bandwidth. In response, memory vendors are selling 4 and 8 DIMM kits specifically for SNB-E systems. Most high-end X79 motherboards feature 8 DIMM slots (2 per channel). Just as with previous architectures, installing fewer DIMMs is possible, it simply reduces the peak available memory bandwidth.

Intel increased bandwidth on the other side of the chip as well. A single SNB-E CPU features 40 PCIe lanes that are compliant with rev 3.0 of the PCI Express Base Specification (aka PCIe 3.0). With no PCIe 3.0 GPUs available (yet) to test and validate the interface, Intel lists PCIe 3.0 support in the chip's datasheet but is publicly guaranteeing PCIe 2.0 speeds. Intel does add that some PCIe devices may be able to operate at Gen 3 speeds, but we'll have to wait and see once those devices hit the market.

The PCIe lanes off the CPU are quite configurable as you can see from the diagram above. Users running dual-GPU setups can enjoy the fact that both GPUs will have a full x16 interface to SNB-E (vs x8 in SNB). If you're looking for this to deliver a tangible performance increase, you'll be disappointed:

| Multi GPU Scaling - Radeon HD 5870 CF | |||||

| Max Quality, 4X AA/16X AF | Metro 2033 (19x12) | Crysis: Warhead (19x12) | Crysis: Warhead (25x16) | ||

| Intel Core i7 3960X (2 x16) | 1.87x | 1.80x | 1.90x | ||

| Intel Core i7 2600K (2 x8) | 1.94x | 1.80x | 1.88x | ||

Modern GPUs don't lose much performance in games, even at high quality settings, when going from a x16 to a x8 slot.

I tested PCIe performance with an OCZ Z-Drive R4 PCIe SSD to ensure nothing was lost in the move to the new architecture. Compared to X58, I saw no real deltas in transfers to/from the Z-Drive R4:

| PCI Express Performance - OCZ Z-Drive R4, Large Block Sequential Speed - ATTO | ||||

| Intel X58 | Intel X79 | |||

| Read | 2.62 GB/s | 2.66 GB/s | ||

| Write | 2.49 GB/s | 2.50 GB/s | ||

The Letdown: No SAS, No Native USB 3.0

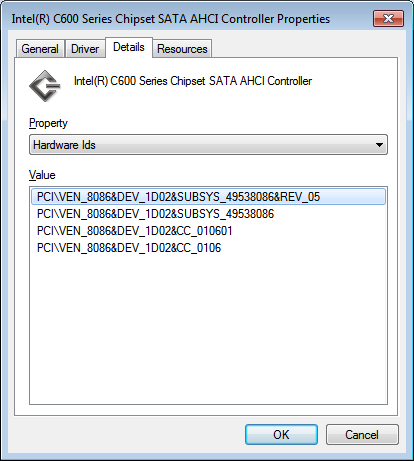

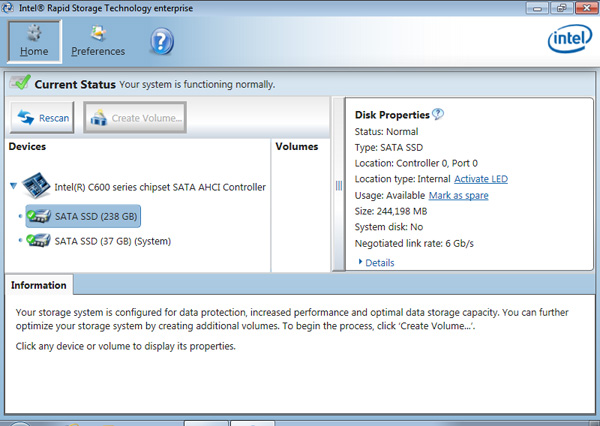

Intel's current RST (Rapid Story Technology) drivers don't support X79, however Intel's RSTe (for enterprise) 3.0 will support the platform once available. We got our hands on an engineering build of the software, which identifies the X79's SATA controller as an Intel C600:

Intel's enterprise chipsets use the Cxxx nomenclature, so this label makes sense. A quick look at Intel's RSTe readme tells us a little more about Intel's C600 controller:

SCU Controllers:

- Intel(R) C600 series chipset SAS RAID (SATA mode)

Controller

- Intel C600 series chipset SAS RAID ControllerSATA RAID Controllers:

- Intel(R) C600 series chipset SATA RAID ControllerSATA AHCI Controllers:

- Intel(R) C600 series chipset SATA AHCI Controller

As was originally rumored, X79 was supposed to support both SATA and SAS. Issues with the implementation of the latter forced Intel to kill SAS support and go with the same 4+2 3Gbps/6Gbps SATA implementation 6-series chipset users get. I would've at least liked to have had more 6Gbps SATA ports. It's quite disappointing to see Intel's flagship chipset lacking feature parity with AMD's year-old 8-series chipsets.

I ran a sanity test on Intel's X79 against some of our H67 data for SATA performance with a Crucial m4 SSD. It looks like 6Gbps SATA performance is identical to the mainstream Sandy Bridge platform:

| 6Gbps SATA Performance - Crucial m4 256GB (FW0009) | ||||||

| 4KB Random Write (8GB LBA, QD32) | 4KB Random Read (100% LBA, QD3) | 128KB Sequential Write | 128KB Sequential Read | |||

| Intel X79 | 231.4 MB/s | 57.6 MB/s | 273.3 MB/s | 381.7 MB/s | ||

| Intel Z68 | 234.0 MB/s | 59.0 MB/s | 269.7 MB/s | 372.1 MB/s | ||

Intel still hasn't delivered an integrated USB 3.0 controller in X79. Motherboard manufacturers will continue to use 3rd party solutions to enable USB 3.0 support.

163 Comments

View All Comments

Hauk - Monday, November 14, 2011 - link

Was hoping to get 40 PCI-E lanes & 2600K performance for $300.. craptastic that they delay the 3820 till next year. Can't wait any longer, 2600K it is..medi01 - Monday, November 14, 2011 - link

Hi,why don't we see AMD cpu pricing along Intel CPU pricing?

g00ey - Monday, November 14, 2011 - link

I think it is false advertising to call the Bulldozer 8C an eight core CPU. It doesn't really have eight cores, it's actually only four cores where they have added an extra ALU inside each core. It's like doubling the core count of the i7s because of the hyperthreading (SMT) feature. The addition of ALUs is nothing but an enhanced version of hyperthreading so a Bulldozer 8C is only 4 cores, 6C is only 3 cores and 4C is only 2 cores.But AMD say; No No No, there are two computation CORES inside each MODULE.

What a BIG WAD of *BULLSHIT*!!!!!!!!!!!!!!!!!!!!!!!!!!!!

They should be thrown into jail for such fraudulent statements!!!

raddude9 - Monday, November 14, 2011 - link

Nope Mr. Troll.Bulldozer 8C can run 8 threads simultaneously. Sandy Bridge E with it's 6 multi-threaded cores can only run 6 threads at the same time, the other 6 threads have to wait.

BSMonitor - Monday, November 14, 2011 - link

Actually you are completely wrong.Hyperthreading actually allows 12 threads to fully utilize the resources of a 6 core processor.

Whereby, Bulldozer simply has double the Integer hardware. Allowing it to run 8 integer threads simulateously. So long as there are that many consecutive integer computations in a row on each thread. Beware when floating point threads start to appear. And then it crawls back to 4 cores.

raddude9 - Monday, November 14, 2011 - link

What did I say that is wrong?Hyperthreading means that each core holds the state of 2 threads. Only one thread can run at a time, usually when one thread stalls, the other thread can kick in. So, at best it can run 6 threads at once, the 6 hyperthreaded threads are waiting in the backround for their chance. But it still just runs 6 threads at once.

You are trying to mislead people with your mis-information on the Bulldozer Floating Point unit. It's FPU can run as either two independent 128bit FPUs or a single 256bit FPU. So it can run two independent Floating Point instructions at once. So, Regardless of whether Bulldozer is running Floating Point or Integer instructions, it can still run 8 threads at once.

LittleMic - Tuesday, November 15, 2011 - link

You are wrong because you are describing T1000 and T2000 CPU and not Intel with HT. Sun processor are indeed hiding memory access latency this way.Intel processors are actually scheduling micro instruction from both threads according to execution resources availabitity. It is quite old technology now so the white papers have disappeared from Intel web site, but if you have a look at

http://en.wikipedia.org/wiki/Hyper-threading

the picture on the right clearly shows that a pipeline stage can contain µ instructions coming from 2 threads

LittleMic - Tuesday, November 15, 2011 - link

No edit...Finally found "official" paper directly from Intel :

http://download.intel.com/technology/itj/2002/volu...

Have a look at page 10 that shows that all the pipeline contains instructions from both threads simultanously.

Lord 666 - Monday, November 14, 2011 - link

Anand,Have read mixed information on the release date for the 26xx series Xeons with respect to release date and architecture. Actually holding off a much needed server because have read either December or Jan.

With the socket the same, is the reviewed SB-E the same design as the new Xeons? Will there be 3D design like Ivy Bridge?

Thanks - Loyal reader for over 7 years

mwarner1 - Monday, November 14, 2011 - link

I am impressed by how much memory you had in your 386SX! My first (IBM compatible) PC was a 486DX2-50 I bought for my Software Engineering degree and it only had 4MB. This was pretty much standard for the time.