ARM's Cortex A7: Bringing Cheaper Dual-Core & More Power Efficient High-End Devices

by Anand Lal Shimpi on October 19, 2011 12:31 PM EST- Posted in

- SoCs

- CPUs

- Arm

- Cortex A15

- Smartphones

- Mobile

- Cortex A7

- Tablets

big.LITTLE: Heterogeneous ARM MP

The Cortex A15 is going to be a significant step forward in performance for ARM architectures. ARM hopes it will be enough to actually begin to threaten the low end of the x86 space, which gives you an idea of just how powerful these cores are going to be. The A15 will also find its way into smartphones and tablets, ultimately replacing the Cortex A9s used by high-end devices today.

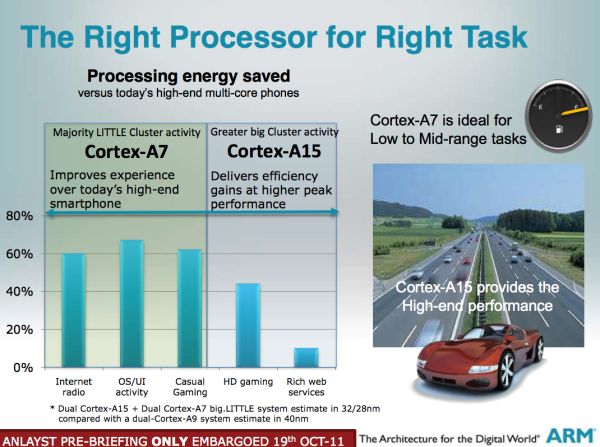

For heavy workloads, the Cortex A15 is expected to be more power efficient than the A9. The core may draw more instantaneous power, but it will do so for a shorter period of time thus allowing the CPU(s) to get to sleep quicker and reducing average power.

As ARM has often argued (particularly against Intel) however, these big out-of-order microprocessor architectures are inefficient at dealing with lightweight mobile workloads. In particular, things like background tasks running on your phone while it’s locked in your pocket simply don’t demand the performance of a Cortex A15. ARM further argues that the power consumed by an A15 running these tasks, even though only for a short period of time, is greater than it would be on a much simpler in-order architecture. This is where the A7 comes into play.

Although the Cortex A7 is fully capable of being used on its own (and it most definitely will be), ARM’s partners are free to integrate Cortex A7 cores alongside Cortex A15 cores in a big.LITTLE (or little.BIG?) configuration.

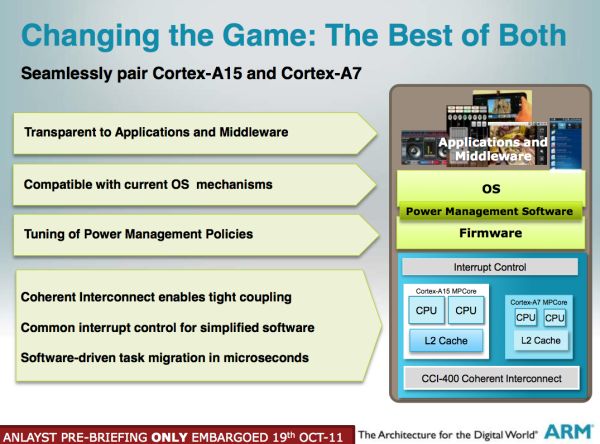

Since the A7 and A15 are equally capable of executing the same ARM instruction set, any applications running on one core can just as easily be migrated to run on the other. In the example above there are a pair of A15s and a pair of A7s on a single SoC. In this particular configuration, the OS only believes there are two cores in the machine. ARM’s own power management firmware determines which core cluster to activate depending on performance states requested by the OS. If the OS wants a high performance state, ARM returns the A15 cores at a high p-state. If it wants a low performance state, the chip will put the A15s to sleep and schedule everything on the A7s. Cache coherency is guaranteed via the CCI-400 interconnect, so any data invalidated by one core cluster will be reflected in the other cluster’s cache. ARM claims it can switch between core clusters in this configuration in as quick as 20 microseconds.

If everything works the way ARM has described it, a big.LITTLE configuration should be perfectly transparent to the OS (similar to what NVIDIA is promising with Kal-el). ARM did add that SoC vendors are free to expose all cores to the OS if they would like, although doing so would obviously require OS awareness of the different core types.

Core Configurations, Process Technology & Final Words

ARM’s Cortex A7 will be available in 1 - 4 core configurations, both as the primary CPU in an SoC as well as in a big.LITTLE configuration alongside some A15s. ARM expects that we will see some 40nm A7 designs as early as the end of next year for use in low end smartphones (~$100). Most smartphone configurations, even at these price points will likely use dual-core A7 implementations. It’s only in emerging markets that ARM is expecting to see single core Cortex A7 smartphone devices. This is pretty big news as it means that even value smartphones will be dual-core by 2013.

Costs will keep the A7 on 40nm for a while although the cores will be offered at 28nm for integration into A15 designs as well as for even higher performance/lower power implementations.

I have to say that I’m pretty excited about the Cortex A7 announcement across the board. It looks like this core will not only enable much better performance at the value end of the device spectrum but it should bring battery life improvements at the high end as well. Chip architects have argued for years that we were going to see heterogeneous computing as the next phase in the evolution of microprocessors, it’s fascinating to see that we may get the first consumer application of it in ultra mobile devices.

75 Comments

View All Comments

introiboad - Thursday, October 20, 2011 - link

I believe it's too early in the development stage and no public data is available for the T-604 nor Rogue (VR6 series). This should change in the coming months I assume, since they announced both quite a while backfrench toast - Thursday, October 20, 2011 - link

cheers, hopefully they will spill the beans soon!ltcommanderdata - Wednesday, October 19, 2011 - link

So they are envisioning a SoC with dual A15 and dual A7 cores, the A15 pair used for high performance and the A7 pair used for low power. Is there a way to use both the A15 and A7 together if there is thermal room since they are the same ISA?fic2 - Wednesday, October 19, 2011 - link

From the aritcle:ARM did add that SoC vendors are free to expose all cores to the OS if they would like, although would obviously require OS awareness of the different core types.

geniekid - Wednesday, October 19, 2011 - link

You could also focus on advancing battery technology.I understand battery tech is much more mature than SoC tech, so revolutionary advancements in this field may be wishful thinking, but it would be cool to see what things are being done in the R&D labs of our smartphone battery producers :)

bjacobson - Wednesday, October 19, 2011 - link

meh that's a dead end.Lithium batteries only store 30% or so of what they are capable of storing. Why don't they? Because at full energy density that energy is just asking to get out-- a pin prick into the cell would set it on fahr.

Etsp - Thursday, October 20, 2011 - link

There are technologies that are much safer than Li-ion currently in development. While Pros/Cons differ between different battery technologies, developing a better battery is never a dead end.That said, I'm certain that there are advancements in battery technology all the time, we just read articles about them.

Etsp - Thursday, October 20, 2011 - link

We just *don't* read articles about them.Steel77 - Thursday, October 20, 2011 - link

Battery technology is by no means "more mature". The techniques developed that are in use today are actually pretty recent advances when you consider that high-output LiFePO4 batteries are a pretty recent invention, and aren't even really on the market yet.Current batteries are dangerous because they use LiCoO4, which decomposes at high temperature to release lithium metal and oxygen. I think it's obvious why that's a bad setup, but we already have a number of potential solutions fairly far along through the research stage.

Other potential advances have come from some recent potentially game-changing success in 3D batteries, which use materials such as aerogels, foams, etc. to give exceptionally high surface areas, which gives them the potential to have much higher power and energy densities. This system is just more difficult because it requires even coatings of subsequent layers, which requires somewhat complicated, though potentially very efficient, chemical methods.

So battery research is extremely important, and there's a lot of progress being made, though it's suffering right now due to research budget shortfalls, at least in the USA.

secretmanofagent - Wednesday, October 19, 2011 - link

This is not my area of expertise, but it really seems like Krait would have an advantage over this design. Am I reading into this incorrectly?