Apple iPhone 4S: Thoroughly Reviewed

by Anand Lal Shimpi & Brian Klug on October 31, 2011 7:45 PM EST- Posted in

- Smartphones

- Apple

- Mobile

- iPhone

- iPhone 4S

The Memory Interface

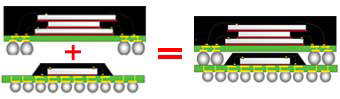

Most SoCs deployed in smartphone designs implement a package-on-package (PoP) stack of DRAM on top of the SoC package. As its name implies, PoP refers to the physical stacking of multiple packages and not layering of raw die. The SoC is typically the lowest level with its memory bus routed to pads on the top of the package. A DRAM package is then stacked on top of the SoC. Avoiding having to route high-speed DRAM lines on the PCB itself not only saves space but it further reduces memory latency.

An example of a PoP stack

The iPhone has always used a PoP configuration for its SoCs and Apple has always been kind enough to silkscreen the part number of the DRAM on the outer package of the SoC. In the past we've seen part numbers from both Samsung and Elpida on Apple SoCs. As both companies can provide similarly spec'd DRAM it makes sense for Apple to source from two suppliers in the event that one is unable to meet demand for a given period.

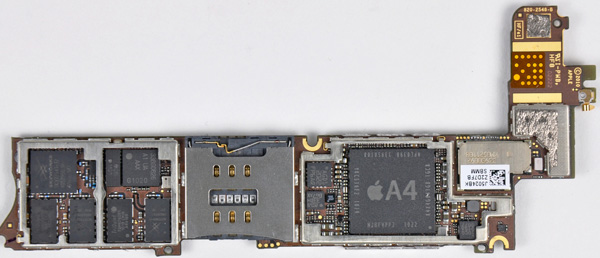

iPhone 4 mainboard, courtesy iFixit

If we look at iFixit's teardown of the iPhone 4 we see the following DRAM part number: K4X4G643G8-1GC8. Most DRAM vendors do a pretty bad job of providing public data about their part numbers used in chip stacks, so we have to do a little bit of inferring to figure out exactly what Apple used last generation.

The first three characters tell us a bit about the type of DRAM. The K means it's memory, the 4 tells us that it's DRAM and the X tells us that it's mobile DDR (aka LPDDR). The next two characters tell us the density of the DRAM, in this case 4G is translated literally to 4Gbit or 512MB. Characters 6 and 7 are also of importance - they tell us the DRAM organization. Samsung's public documentation only tells us that 16 refers to a 16-bit interface and 32 here would mean a 32-bit interface. Based on that we can safely assume that the 4Gbit DRAM on the A4 is 64-bits wide. In the mobile world a 32-bit interface typically refers to a single channel, which confirms the A4's DRAM interface is two 32-bit channels wide.

The last two characters in the part number, C8, tell us the source clock frequency of the DRAM. Samsung's datasheets tell us that C8 corresponds to a 5ns cycle time with a CAS latency of 3 clocks. Taking the inverse of that gives us 200MHz (frequency = 1 / clock period). Remember, we're talking about double data rate (DDR) SDRAM so data is transferred at both the rising and falling edges of the clock, making the effective data rate 400MHz.

All of this tells us that the iPhone 4's A4 SoC has a 64-bit wide LPDDR1 memory interface with a 400MHz data rate. Multiply all of that out and you get peak theoretical bandwidth of 3.2GB/s. DDR memory interfaces are generally 80% efficient at best so you're looking at a limit of around 2.5GB/s. To put this in perspective, the A4 has as much memory bandwidth as the original AMD Athlon 64 released in 2003.

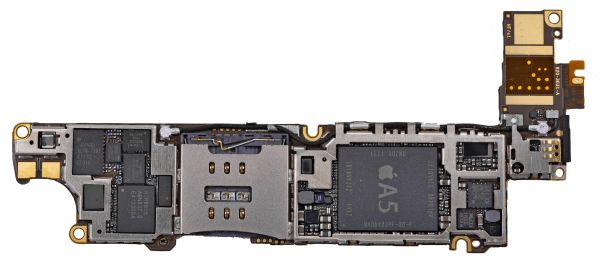

iPhone 4S mainboard, courtesy iFixit

With the A5 Apple definitely stepped up the memory interface. Once again we turn to iFixit's teardown of the iPhone 4S to lift that oh-so-precious part number: K3PE4E400B-XGC1.

The K once again tells us we're dealing with Samsung memory, while the 3P reveals there are two mobile DDR2 with 4n prefetch (aka LPDDR2-S4) DRAM die on the package. Why not a 4 this time? Technically the 4 refers to a discrete DRAM while the 3 implies a DRAM stack, obviously both are stacked DRAM so I'm not entirely sure why there's a difference here. Each of the next two E4s tell us the density of the two DRAM die. Samsung's public documentation only goes up to E3 which corresponds to a 1Gbit x32 device. Given that we know the A5 has 512MB on-package, E4 likely means 2Gbit x32 (256MB 32-bit). There are two E4 die on package which makes up the 512MB 64-bit DRAM stack.

Once again the final two characters reveal the cycle time of the DRAM: 2.5ns. The inverse of 2.5ns gives us a 400MHz clock frequency, or an 800MHz data rate (source clock frequency is actually 200MHz, but with a 4n prefetch we can transfer at effectively 800MHz). Peak bandwidth to the A5 is roughly double that of the A4: 6.4GB/s. This is as much memory bandwidth as AMD's Athlon 64 platform offered in late 2004, just 7 years later and in a much smaller form factor.

The doubling of memory bandwidth requires a sufficiently large workload to really show it. We see this in Geekbench's memory bandwidth results where the A5 doesn't appear to offer any more bandwidth than the A4 in all but one of the tests:

| Memory Bandwidth Comparison - Geekbench 2 | ||||

| Apple iPhone 4 | Apple iPhone 4S | |||

| Overall Memory Score | 593 | 700 | ||

| Read Sequential | 318.7 MB/s | 302.3 MB/s | ||

| Write Sequential | 704.9 MB/s | 809.2 MB/s | ||

| Stdlib Allocate | 1.55 Mallocs/sec | 1.55 Mallocs/sec | ||

| Stdlib Write | 1.25 GB/s | 2.54 GB/s | ||

| Stdlib Copy | 724.5 MB/s | 490.1 MB/s | ||

| Overall Stream Score | 280 | 281 | ||

| Stream Copy | 413.5 MB/s | 396.4 MB/s | ||

| Stream Scale | 313.3 MB/s | 317.4 MB/s | ||

| Stream Add | 518.0 MB/s | 527.1 MB/s | ||

| Stream Triad | 363.6 MB/s | 373.9 MB/s | ||

Memory bandwidth tests are extremely sensitive to architecture optimizations, particularly for single threaded tests like these so I wouldn't read too much into the cases where you see no gains or a drop.

The increase in raw memory bandwidth makes a lot of sense. Apple doubled the number of CPU cores on the A5, with each one even more bandwidth hungry than the single A4 core. The 4x increase in GPU compute combined with an increase in clock speeds give the A5 another big consumer of bandwidth. Add things like 1080p video capture and the memory bandwidth increase seems justified.

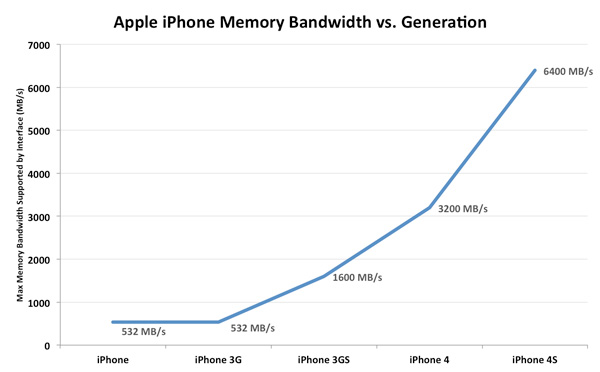

Looking back at the evolution of the iPhone's memory interface gives us an idea of just how quickly this industry has been evolving. Back in 2007 the original iPhone debuted with a 16-bit wide LPDDR-266 memory interface connected to a meager 128MB of DRAM. The 3GS delivered a huge increase in memory bandwidth by doubling the interface width and increasing the data rate to 400MHz. Scaling since then has been even more dramatic:

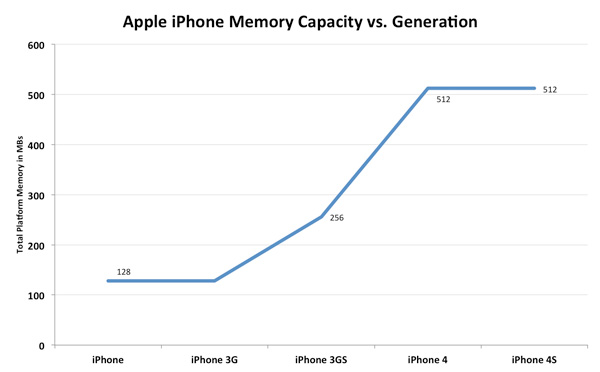

Memory capacity on the other hand has seen more of a step-function growth:

By using a mobile optimized OS Apple has been able to get around large memory requirements. The growth pattern in memory size partially illustrates the lag between introducing faster hardware and developers building truly demanding applications that require that sort of performance. Apple was able to leave the iPhone 4S at 512MB of RAM because the target for many iOS apps is still the iPhone 3GS generation. Don't be surprised to see a move to 1GB in the next iPhone release (we won't see 768MB due to the dual-channel memory requirement) as the app developer target moves to 512MB.

199 Comments

View All Comments

tipoo - Monday, October 31, 2011 - link

Anyone know if there is a reason this hasn't made it into any Andriod phone yet? Does Google specify compatible GPU's, or is it cost, or development time, etc? Looks like it slaughters even the Mali 400 which is probably the next fastest.zorxd - Monday, October 31, 2011 - link

The only reason is that no one used it yet. The TI OMAP 4470 will use the 544 which is probably a little faster.The SGS2 is using the slower Mali 400, however it was released 6 months ago. Yet it's not that bad, even beating the 4S in Glbenchmark pro.

zorxd - Monday, October 31, 2011 - link

I meant no SoC vendor is using it.djboxbaba - Monday, October 31, 2011 - link

The numbers were incorrect and have been updated, the 4S is ~2x faster than the GS2 on the GLBenchmark Pro.freezer - Thursday, November 3, 2011 - link

But not when running at phone's native resolution. Thats what people will use while running games on their phone.iPhone 4S has much more pixels for GPU to draw while having much smaller screen. Not very optimal for gaming right?

http://glbenchmark.com/result.jsp?benchmark=glpro2...

djboxbaba - Thursday, November 3, 2011 - link

Correct, but we're comparing the GPU's by standardizing the resolution. Of course in the native resolution this will change.thunng8 - Monday, October 31, 2011 - link

I don't see any GL benchmark that the Mail 400 beats the 4S???freezer - Thursday, November 3, 2011 - link

That's because Anandtech review shows only the 720p offscreen results.This gives very different numbers compared to running GL Benchmark Pro in phone's native resolution.

iPhone 4S has about 60% more pixels than Galaxy S2, and so its GPU has to draw much more pixels in every frame.

Go to glbenchmark.com and dig database yourself.

Ryan Smith - Monday, October 31, 2011 - link

The 544 should be identical to the 543 at the same clock and core configuration. It's effectively a 543 variant with full D3D feature level 9_3 support. The primary purpose of the 544 will be to build Windows devices, whereas for non-Windows devices the 543 would suffice. We don't have access to PowerVR's pricing, but it likely costs more due to the need to license additional technologies (e.g. DXTC) to achieve full 9_3 support.Penti - Tuesday, November 1, 2011 - link

Who will use it to support Windows Phone though? Qualcomm uses their own AMD/ATi based Adreno GPU. I guess it will be TI's attempt off getting Microsoft to support Windows Phone on their SoC in order to supply say partners of theirs like Nokia. Or might just be a later purchase/contract date for the other SoC vendors. Getting the IP-blocks later, but many did opt for the Mali-400 so why wouldn't they opt for the successor too? It seems to have worked out good. Samsung is just one of the vendors that usually did use PowerVR. I guess ST-E will use it in order to support Windows Phone on Nova A9540 SoC too. While Android vendors might opt for the older A9500 still.Interesting to see how Nvidia do lag in this field though.