Intel's Ivy Bridge Architecture Exposed

by Anand Lal Shimpi on September 17, 2011 2:00 AM EST- Posted in

- CPUs

- Intel

- Ivy Bridge

- IDF 2011

- Trade Shows

Cache, Memory Controller & Overclocking Changes

Despite the title of this section, to my knowledge there haven't been any changes to Ivy Bridge's cache. The last level cache (L3) is still shared via a ring bus between all cores, the GPU and the system agent. Quad-core Ivy Bridge CPUs will support up to 8MB of L3 cache, and the private L1/L2s haven't increased from their sizes in Sandy Bridge (32+32K/256K).

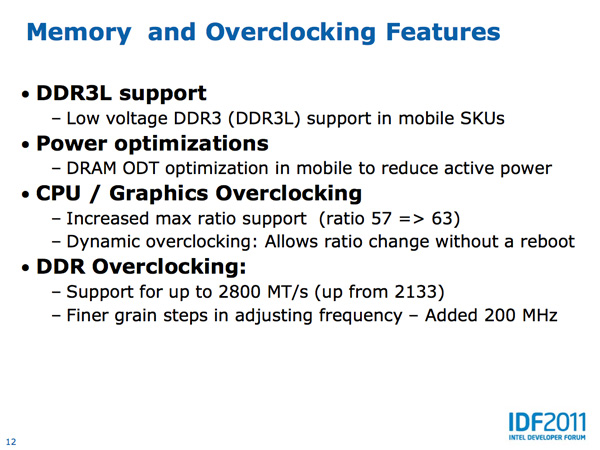

The memory controller also remains relatively unchanged, aside from some additional flexibility. Mobile IVB supports DDR3L in addition to DDR3, enabling 1.35V memory instead of the standard 1.5V DDR3. This is particularly useful in notebooks that have on-board DDR3 on the underside of the notebook; OEMs can use DDR3L and keep your lap a bit cooler.

From Nehalem to Sandy Bridge, Intel introduced fairly healthy amounts of power gating throughout the processor. With little more to address in Ivy Bridge, Intel power gated one of the last available portions of the die: the DDR3 interface. If there's no external memory activity, the DDR3 interface can now be turned off completely. External IOs leak current like any other transistor so this change makes sense. Power gating simply increases die size but at 22nm Intel should have some extra area to spend on things like this.

Memory overclocking also gets a bump in Ivy Bridge. The max supported DDR3 frequency in SNB was 2133MHz, Ivy Bridge moves this up to 2800MHz. You can now also increase memory frequency in 200MHz increments.

97 Comments

View All Comments

Hrel - Thursday, September 22, 2011 - link

1: I said comparable, not competitive.2: I don't care about price. I make enough it doesn't matter. I just care about performance. At the same time, I don't waste money, so I don't buy Extreme Editions either. I buy whatever CPU has the best performance around 200 bucks.

Point: At this point if AMD is even close (within 15%) I'm switching.

mino - Monday, September 26, 2011 - link

If price does not matter, the you shall not bother about desktop stuff and go directly fro 2P workstations with ECC.Just a thought.

JKflipflop98 - Monday, October 24, 2011 - link

Hind sight is 20/20 now.Zoomer - Saturday, September 17, 2011 - link

That stuff can, and imo should, be implemented in the filesystem.Cr0nJ0b - Saturday, September 17, 2011 - link

I'm wondering they wounldn't just got with all USB 3.0 ports since they are backward compatible with other UBS forms. Maybe a licensing cost issue?Zoomer - Saturday, September 17, 2011 - link

Intel's platform is really a mess and a hodgepodge nowadays. Pity.ggathagan - Saturday, September 17, 2011 - link

There aren't enough PCIe lanes to allow for that kind of bandwidth.DanNeely - Sunday, September 18, 2011 - link

Along with the fact that USB3 controllers are larger and need more pins on the chip to connect. They're the same reasons that AMD only has a 4 USB3 ports on its most recent southbridges.marcusj0015 - Saturday, September 17, 2011 - link

Intel Invented USB...so no there are no licensing costs that i can think of.

Aone - Sunday, September 18, 2011 - link

Is Ivy's Quick Sync in the same power gated domain together with IGP as it happens in SB or Quick Sync and IGP can be switched on/off independently?