Intel's Ivy Bridge Architecture Exposed

by Anand Lal Shimpi on September 17, 2011 2:00 AM EST- Posted in

- CPUs

- Intel

- Ivy Bridge

- IDF 2011

- Trade Shows

Core Architecture Changes

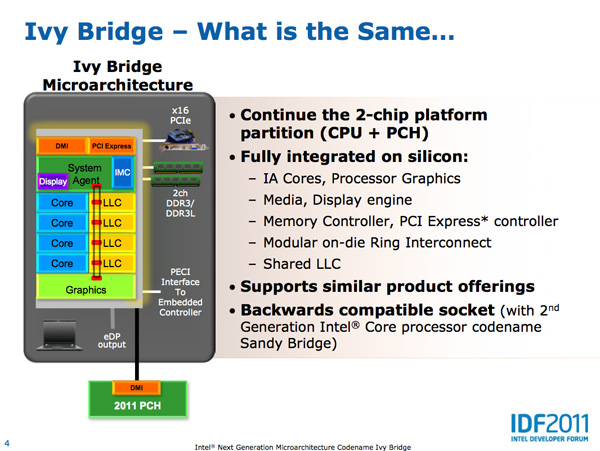

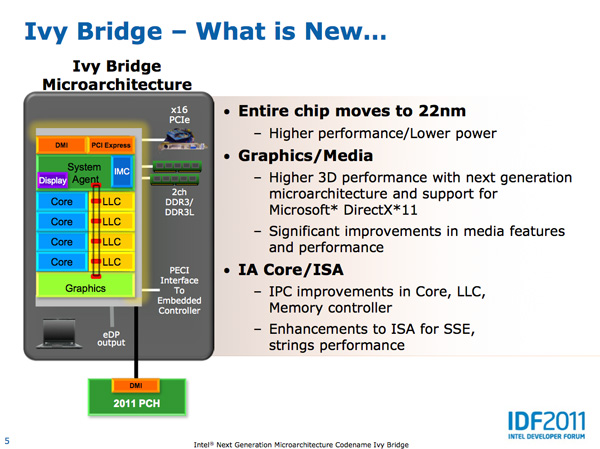

Ivy Bridge is considered a tick from the CPU perspective but a tock from the GPU perspective. On the CPU core side that means you can expect clock-for-clock performance improvements in the 4 - 6% range. Despite the limited improvement in core-level performance there's a lot of cleanup that went into the design. In order to maintain a strict design schedule it's not uncommon for a number of features not to make it into a design, only to be added later in the subsequent product. Ticks are great for this.

Five years ago Intel introduced Conroe which defined the high level architecture for every generation since. Sandy Bridge was the first significant overhaul since Conroe and even it didn't look very different from the original Core 2. Ivy Bridge continues the trend.

The front end in Ivy Bridge is still 4-wide with support for fusion of both x86 instructions and decoded uOps. The uOp cache introduced in Sandy Bridge remains in Ivy with no major changes.

Some structures within the chip are now better optimized for single threaded execution. Hyper Threading requires a bunch of partitioning of internal structures (e.g. buffers/queues) to allow instructions from multiple threads to use those structures simultaneously. In Sandy Bridge, many of those structures are statically partitioned. If you have a buffer that can hold 20 entries, each thread gets up to 10 entries in the buffer. In the event of a single threaded workload, half of the buffer goes unused. Ivy Bridge reworks a number of these data structures to dynamically allocate resources to threads. Now if there's only a single thread active, these structures will dedicate all resources to servicing that thread. One such example is the DSB queue that serves the uOp cache mentioned above. There's a lookup mechanism for putting uOps into the cache. Those requests are placed into the DSB queue, which used to be split evenly between threads. In Ivy Bridge the DSB queue is allocated dynamically to one or both threads.

In Sandy Bridge Intel did a ground up redesign of its branch predictor. Once again it doesn't make sense to redo it for Ivy Bridge so branch prediction remains the same. In the past prefetchers have stopped at page boundaries since they are physically based. Ivy Bridge lifts this restriction.

The number of execution units hasn't changed in Ivy Bridge, but there are some changes here. The FP/integer divider sees another performance gain this round. Ivy Bridge's divider has twice the throughput of the unit in Sandy Bridge. The advantage here shows up mostly in FP workloads as they tend to be more computationally heavy.

MOV operations can now take place in the register renaming stage instead of making it occupy an execution port. The x86 MOV instruction simply copies the contents of a register into another register. In Ivy Bridge MOVs are executed by simply pointing one register at the location of the destination register. This is enabled by the physical register file first introduced in Sandy Bridge, in addition to a whole lot of clever logic within IVB. Although MOVs still occupy decode bandwidth, the instruction doesn't take up an execution port allowing other instructions to execute in place of it.

ISA Changes

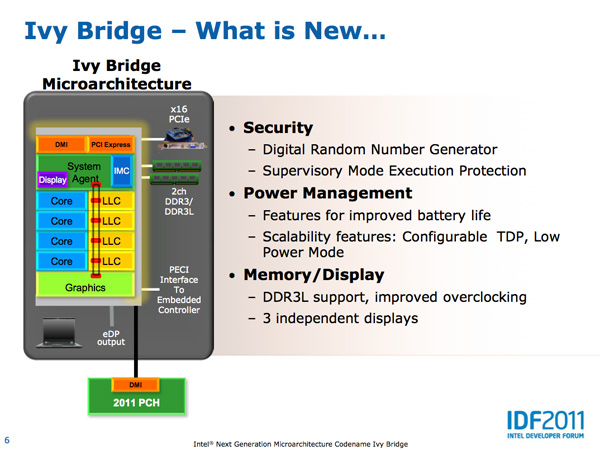

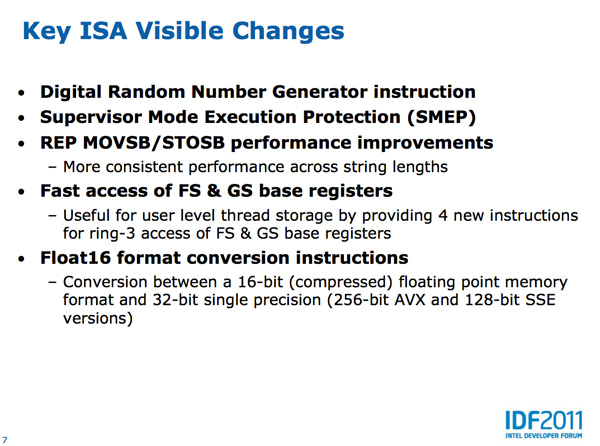

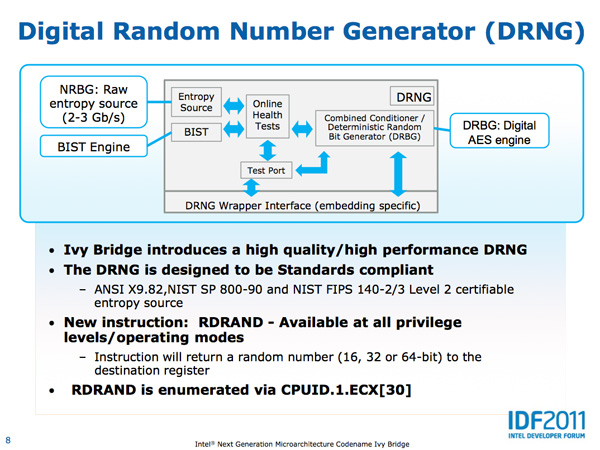

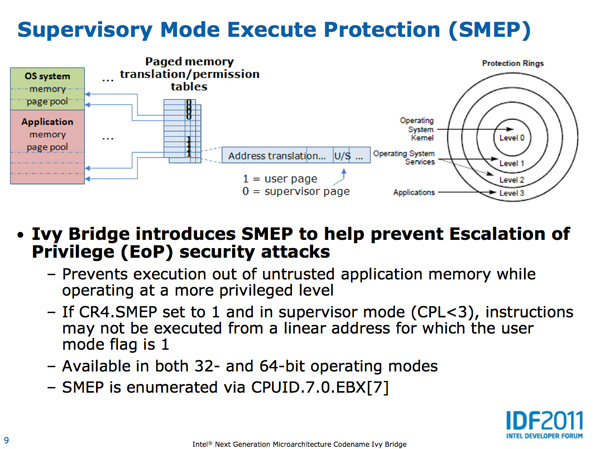

Intel also introduced a number of ISA changes in Ivy Bridge. The ones that stand out the most to me are the inclusion of a very high speed digital random number generator (DRNG) and supervisory mode execution protection (SMEP).

Ivy Bridge's DRNG can generate high quality random numbers (standards compliant) at 2 - 3Gbps. The DRNG is available to both user and OS level code. This will be very important for security and algorithms going forward.

SMEP in Ivy Bridge provides hardware protection against user mode code being executed in more privileged levels.

97 Comments

View All Comments

piroroadkill - Saturday, September 17, 2011 - link

I'd have liked a little more on this.. What's the source?I searched anyway, and found it is using thermal sampling. Presumably it's also seeded. Anyway, I thought it was of interest.

Jamahl - Saturday, September 17, 2011 - link

Don't you get tired of saying "intel is finally taking gpu performance seriously" every year? I do.JonnyDough - Monday, September 19, 2011 - link

I'd just like to say...=) Yes sir, I do.

imaheadcase - Saturday, September 17, 2011 - link

I heard when sandy bridge came out they was considering a GPUless version for enthusiasts who don't need it..is that something they will do eventually?I suspect its tied to the core, so not going to happen because of high costs. But wouldn't that save even more power/heat problems with that removed?

It just seems like its a mobile orientated cpu vs consumer. :D

DanNeely - Saturday, September 17, 2011 - link

With power gating if you're not using the IGP it doesn't consume any power; so the only thing they'd save on is die area by removing it.imaheadcase - Saturday, September 17, 2011 - link

Ah did not know that part. thanks.fic2 - Monday, September 19, 2011 - link

"I heard when sandy bridge came out they was considering a GPUless version for enthusiasts who don't need it..."Interesting since Intel did the exact opposite - put the only GPU with half decent performance into the enthusiast 'K' series.

JonnyDough - Monday, September 19, 2011 - link

The only people who would actually consider that are businesses and home users who don't play "real" games. :Pjjj - Saturday, September 17, 2011 - link

"I believe that x86 CPU performance is what sells CPUs today"That's not all that true anymore,there was a time when apps used by everybody required a fast CPU but that's not the case anymore nowdays..Just a few years ago playing HD content was a chalange on older systems but now ,if you look at usage paterns and what kind of perf is needed, the picture has changed. This is one of the reasons PC sales are not doing so great,there is no need to upgrade your system every 1-2 years.Even Windows is not driving system requirements up anymore.

In the consumer space GPU and battery life matter more now. Intel is trying to fight all this with lower power consumption, ultrabooks but that far from enough.If they want to survive the ARM "tsunami" (think about the financial part too here not just perf) , they got to push the software to be more demanding too and maybe the easiest is to do it on the GPU side -not in games.

MadMan007 - Saturday, September 17, 2011 - link

Intel's quarterly results say there is less to worry about than hyperbolic ARM domination headlines would lead one to think. One IDF slide showed large growth in emerging markets where the analysts aren't as able to get reliable data. Yes, PC upgrade cycles are longer, but that doesn't mean there is not net worldwide growth.There is room for growth in both areas, it's not a zero-sum game, and some things like mobile video consumption actually go hand-in-hand with faster beefy CPUs.