Everything You Always Wanted to Know About SDRAM (Memory): But Were Afraid to Ask

by Rajinder Gill on August 15, 2010 10:59 PM ESTSynchronous dynamic random access memory (SDRAM) is made up of multiple arrays of single-bit storage sites arranged in a two-dimensional lattice structure formed by the intersection of individual rows (Word Lines) and columns (Bit Lines). These grid-like structures, called banks, provide an expandable memory space allowing the host control process and other system components with direct access to main system memory to temporarily write and read data to and from a centralized storage location.

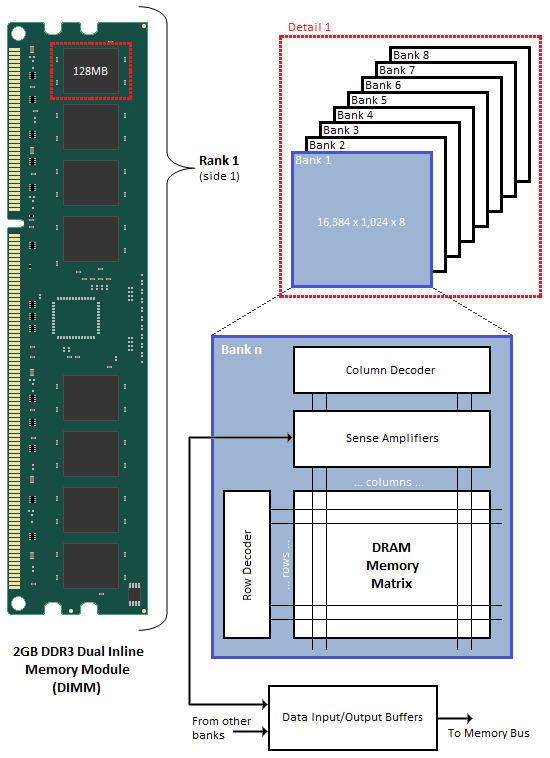

When associated in groups of two (DDR), four (DDR2) or eight (DDR3), these banks form the next higher logical unit, known as a rank. 2GB DDR3 Dual Inline Memory Modules (DIMM) are undoubtedly the most popular density choice among today's enthusiast users. Most new parts of this type are configured as two identical ranks of eight banks each; one side of the DIMM housing those ICs that make up Rank 1, with Rank 2 populating the opposite face of the module. For this reason, single-sided DIMMs typically comprise only a single rank of addressable memory space.

Figure 1 shows the typical functional arrangement of SDRAM memory space. In the case of our example dual-sided dual-rank unbuffered 2GB SDRAM DIMM, the fully populated module contains a total of 16 ICs, eight per side. Each IC contains eight banks of addressable memory space comprising 16K pages and 1K column address starting points with each column storing a single 8-bit word. This brings the total memory space to 128MB (16,384 rows/bank x 1,024 columns addresses/row x 1 byte/column address x 8 stacked banks) per IC. And since there are eight ICs per rank, Rank 1 is 1GB (128MB x 8 contiguous banks) in size, with the same for Rank 2, for a grand total of 2GB per module.

If each row contains 1K (1,024) column address staring points and each column stores 8 bits (1 byte), this would mean each row (page) is 8,192 bits (1,024 x 8 bits) or 1K bytes per bank. It's important to understand that each page of memory is segmented evenly across Bank n of each IC for the associated rank. For this reason, each page is in actuality 8KB (1KB x 8 contiguous banks) in size. So when we talk about IC density we are referring to eight distinct stacked banks and the total memory space therein, whereas when we talk about page space, we are really working with Bank n spread across the total number of ICs per rank. In the end the math comes out the same (8 ICs versus 8 banks), but conceptually it's a critical distinction worth acknowledging if we are to really grasp the ins and outs of memory addressing.

We can now see why the DDR3 core has a 8n-prefetch (where n refers to the number of banks per rank) as every read access to the memory requires a minimum of 64 bits (8 bytes) of data to be transferred. This is because each bank, of which there are eight for DDR3, fetches no less than 8 bits (1 byte) of data per read request - the equivalent of one column's worth of data. Whether or not the system actually makes use of all 8 bytes of transferred data is irrelevant. Any delivered data not actually requested can be safely disregarded as it's just a copy of what is still retained in memory.

46 Comments

View All Comments

Dwebtron - Monday, August 16, 2010 - link

How did you know I was afraid to ask!!0ldman79 - Tuesday, May 28, 2019 - link

It's because we're all from the future.neslog - Monday, August 16, 2010 - link

Thank you for a great article on memory and you are right, I was afraid to ask.landerf - Monday, August 16, 2010 - link

I've found for the i7 platform the perfect ram setup is 1200 Mhz + cas5 or 6 timings, a 3:1 uncore ratio, and a B2B of 4. Not only does this perform well even in synthetics, it provides the "smoothest" intel experience. Something people who use amd and intel have been complaining about intel lacking. Check this chart and see how well that setup performs compared to all the conventional 2:1 setups. https://spreadsheets.google.com/ccc?key=0AsaXlcTga...Servando Silva - Monday, August 16, 2010 - link

Thanks for a great article. It will take me a while to read it carefully and fully understand it.Kris + Raju = Killer combo.

neslog - Monday, August 16, 2010 - link

On page 8 you may want to change the wording in the last paragraph " Once you've had...to cordially invite[d] (you) to do some..."

Thanks again for the article. I appreciate all the work that went into putting it together

elforeign - Monday, August 16, 2010 - link

It's a site willing to go the extra mile like this to report and educate the masses that are truly worth the time to peruse and read the posted articles. I check this site daily because there is always something interesting to read. Thank you to all the staff who do a great job here!chizow - Monday, August 16, 2010 - link

Just kidding....Or am I? :D

JarredWalton - Monday, August 16, 2010 - link

There's obviously benefits to either direction. Reducing latency is definitely a priority, but something not mentioned in the text that bears repeating is that latency is a factor of clock speed as well as the various timings. While CAS 6 will always be better than CAS 7 at the same base clock (and likewise for the other timings), if you have a faster memory speed CAS 7 could end up being better.So here's the scoop:

DDR3-1066 = 266MHz base clock, or 3.75ns per cycle.

DDR3-1333 = 333MHz base clock, or 3.00ns per cycle.

DDR3-1600 = 400MHz base clock, or 2.50ns per cycle.

DDR3-2000 = 500MHz base clock, or 2.00ns per cycle.

That gives this table in order of increasing latency, with rough pricing for 2x2GB. Based on pricing and latency, I've starred the best buys on Newegg:

CAS 6 DDR3-2000 = 12.0ns. ($180)

CAS 7 DDR3-2000 = 14.0ns. ($140)

CAS 6 DDR3-1600 = 15.0ns. ($115) ***

CAS 8 DDR3-2000 = 16.0ns. ($150)

CAS 7 DDR3-1600 = 17.5ns. ($101) ***

CAS 9 DDR3-2000 = 18.0ns. ($100) ***

CAS 6 DDR3-1333 = 18.0ns. ($100) ***

CAS 10 DDR3-2000 = 20.0ns. ($118)

CAS 8 DDR3-1600 = 20.0ns. ($85) ***

CAS 7 DDR3-1333 = 21.0ns. ($90)

CAS 9 DDR3-1600 = 22.5ns. ($92)

CAS 8 DDR3-1333 = 24.0ns. ($92)

CAS 7 DDR3-1066 = 26.3ns. ($80)

CAS 9 DDR3-1333 = 27.0ns. ($85)

CAS 8 DDR3-1066 = 30.0ns. ($93)

Notice how the total latency often comes in groups. The DDR3-1333 CL6, DDR3-1600 CL7, and DDR3-2000 CL9 are all priced around $100. If you buy any of these modules, there's a good chance (though YMMV) that you can tweak timings to run at whichever value makes you happiest. I'd probably err on the side of buying the higher speed rated modules, though, or at least grab the 1600MHz set.

Rick83 - Monday, August 16, 2010 - link

Your pricing comparison is sadly missing one important factor:Operating voltage.

I was at first surprised by the high cost of 1333/9, but I expect the voltage of that kit to be around 1.5, where most 1333/7 kits already clock in at 1.65.

The 2000/9 kit probably also runs higher V's than the identically priced 1333/6?

Lower voltages are usually preferred, as they give you a) more headroom and b) less heat at stock - with on-die controllers even less cpu heat.