Intel Unveils Moorestown and the Atom Z600, The Fastest Smartphone Platform?

by Anand Lal Shimpi on May 4, 2010 11:54 PM EST- Posted in

- Smartphones

- Intel

- Atom

- Mobile

- SoCs

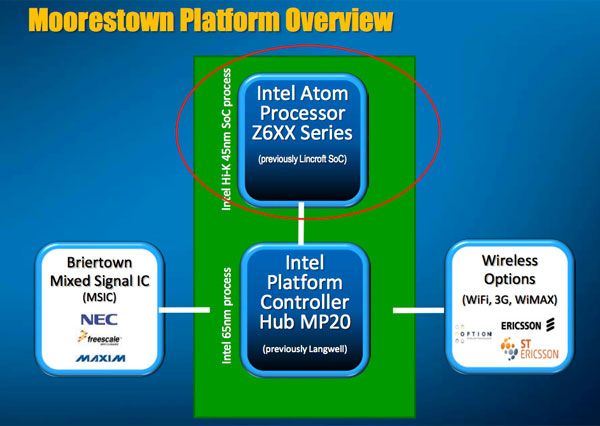

Moorestown: The Two Chip Solution That Uses Five Chips

Intel calls Moorestown a two-chip solution. That’s the Lincroft SoC and the Langwell IO Hub. Intel says there’s no architecture limitation for splitting these two up, it was just a way of minimizing risk. You put the bulk of the 3rd party technologies in the Langwell IO Hub and keep the important, mostly Intel controlled components in Lincroft. This is still the first SoC that Intel is going to market with, so splitting the design into two chips makes sense. The followon to Moorestown, codenamed Medfield, will integrate these two once Intel is comfortable.

The 45nm, 140M transistor Lincroft die

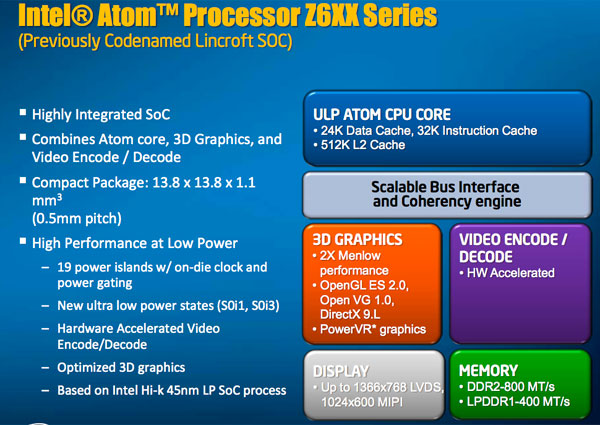

Lincroft houses the CPU, GPU and memory controller and is built on Intel’s 45nm process. This isn’t the same 45nm process used in other Intel CPUs, instead it’s a special low power version that trades 6 - 8% performance for a 60% reduction in leakage. The tradeoff makes sense since the bulk of these chips will run at or below 1.5GHz. And by the way, it’s now called the Atom Z600 series.

| Transistor Comparison | |||||

| Intel Atom Z5xx Series | Intel Atom Z6xx Series | NVIDIA Tegra 2 | |||

| Manufacturing Process | 45nm | 45nm | 40nm | ||

| Transistor Count | 47M | 140M | 260M* | ||

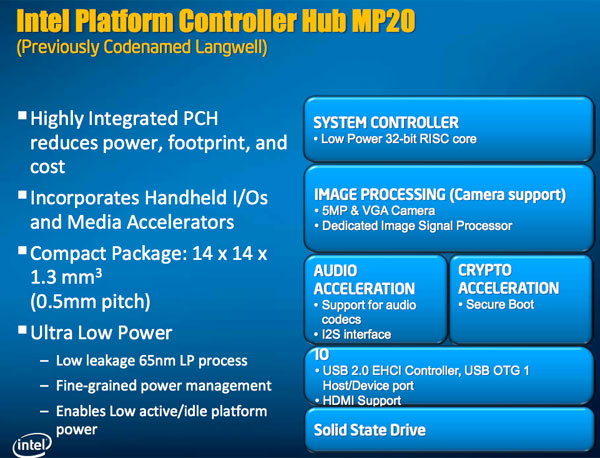

Langwell, now known as the Intel Platform Controller Hub (PCH) MP20, holds virtually everything else. It’s got an image processing core that supports two cameras (1 x 5MP and 1 x VGA), USB 2.0 controller, HDMI output (1080p) and a NAND controller that can support speeds of up to 80MB/s. The whole chip is managed by a 32-bit RISC core.

Langwell is a 65nm chip built at TSMC. TSMC has existing relationships with all of the IP providers for the blocks inside Langwell, so making it at TSMC is a sensible move (a temporary one though, with Medfield Intel will integrate all of this).

and_PlatformControllerHub_package2_sm.jpg)

Langwell (left) and Lincroft (right)

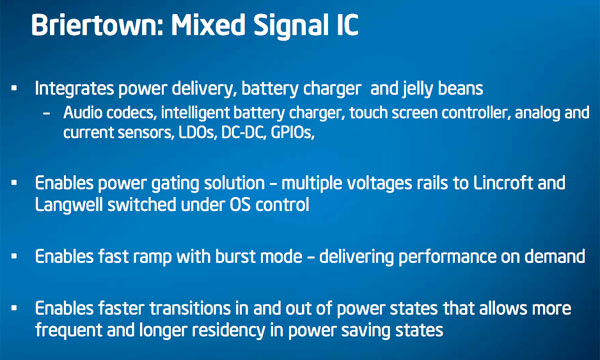

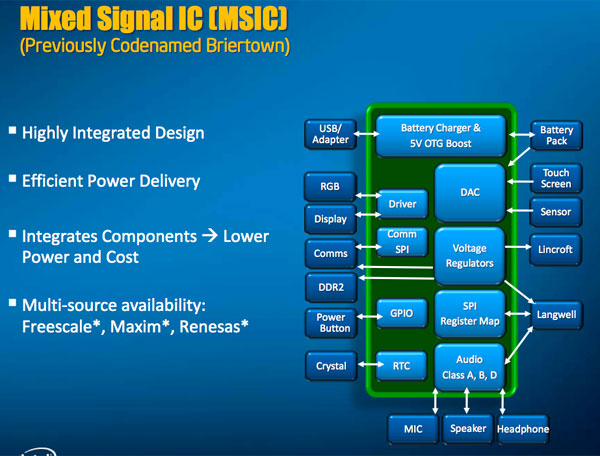

While Lincr, err, Atom Z600 and the Intel PCH MP20 are enough for a traditional system, they are not enough for a smartphone. You need wireless radios, that’s one chip for WiFi and one for 3G support. You need something to handle things like power management, charging the battery and controlling the touch screen. That’s an additional chip, called Briertown.

We’re up to four chips at this point, but you need at least one more. While modern day smartphone SoCs ship with on-package memory, Intel doesn’t yet support that. Obviously it’s not impossible to do, Marvell, TI, Qualcomm and Samsung do it with all of their SoCs. Look inside Apple’s iPad and you won’t see any DRAM chips, just a Samsung part number on the application processor package. Intel doesn’t have the same experience in building SoCs and definitely not in integrating memory so it’s not a surprise we don’t have that with Moorestown. Unfortunately this means a smartphone manufacturer will need as many as five discrete chips to support Moorestown.

| Platform Size | |||||

| Moorestown | |||||

| CPU + Chipset | 387 mm2 | ||||

| Total Platform Area | 4200 mm^2 | ||||

| SoC Package Size | 13.8 mm x 13.8 mm x 1.0 mm | ||||

| PCH Package Size | 14 mm x 14 mm x 1.33 mm | ||||

And now we know why Intel has been showing off its extremely long form factor prototype all this time:

67 Comments

View All Comments

strikeback03 - Thursday, May 6, 2010 - link

Actually, at least on Verizon, there are not many phones that last more than 2-3 days with relatively light use (5-10 min talk, 20-30 txt per day). This is actually something that has gone down in the past few years, as even basic phones get flashier UIs and use more power to run them. And while I support having some phones with weeklong standby time, I am fine with charging my phone or switching batteries every night so long as the phone can last a day in moderate use, which the Snapdragon phones typically can. I like to be able to access more than talk and text on the go.v12v12 - Monday, May 10, 2010 - link

WOW... standing ovation... All of my Droid friends are laughable! Constantly tethered to a power outlet! Always doing something useless and for sure entertainment Vs thinking quietly with their minds... pretty soon "dude I gotta go, my phone is about to die," yeah umm just how many hours have your spent actually TALKING on the dang thing vs playing around with it constantly like some personalized TOY?Battery life should be much more focused upon... The cattle-minded consumers are at it again; now tell me, had to only have 1 car, would you also buy a car that gets the WORST miles per gallon, but has a bunch of silly go-fast features that have you constantly at the fuel pump Vs getting to where you need/should be? Course that's why people usually own 2 cars to separate those needs Vs desires.... Today's "Ferrari" phones have the everyday idiot rambling along, bumping into shit, with their heads constantly fixated on the "screen," like drones. Talking...(?) haha you rarely see people talking with these things, it's just constant "entertainment," even in the most hindering places and social situations. So everyone's got a "Ferrari" phone, but end up trying to use it like a honda; sorry it just doesn't work like that. Faster = more fuel, LESS actual usefulness.

__I'd rather have a phone with a decent amount of enjoyable features, that I can actually take with me on a trip to places that may or may not have power ON-DEMAND lol..

juampavalverde - Wednesday, May 5, 2010 - link

The article and the new product is really interesting, but intel aint ready yet for smartphones, actually this moorestown platform looks much more interesting for pads and handhelds, having more space for such amount of chips, also being x86 with a custom linux. something like an ipad powered by this kind of atom starts to make sense, both from the performance and the battery lifeWorldMage - Thursday, May 6, 2010 - link

The interesting thing about all of the power draw figures given is that they were for workloads wherethe ATOM would be doing almost nothing. Video decode is done by the video decode HW where the

atom might wake up every few seconds to load the next batch of data, similarly for audio playback and

talk time (as you point out cellular modem is the only thing doing work). The thing that gets closest is web browsing, but assuming they are browsing 'static' pages (i.e. no Flash) the atom does a bit of work and probably sits essentially idle for easily 90% of the time.

So it's not surprising they are in the same ballpark as other SOC's for those workloads since they seem to essentially be using the same HW blocks as the competing SOC's. I think it's very telling that all of the power consumption figures from Intel were for essentially non-Atom work loads.

To which you might say "so what?" if those are the work flows that you care about, but that would ignore the fact that the whole point of the atom is to enable "fancy" UI's (and perhaps games) with lots of animation and stuff happening in the background and actually making use of the power of an ATOM.

If you can't actually power the ATOM for an hour of actual use (browsing contacts, checking flights, web pages with Flash ads etc) won't the smart phone be almost worthless?

Th3Loonatic - Thursday, May 6, 2010 - link

On page 3 of the article you misnamed the chips. The one on the left is Lincroft and the one on the right is Langwell.Electrofreak - Friday, May 7, 2010 - link

Anand, Cortex A8 on the 65 nm feature size is reported to use about 0.59 mW per MHz under load, and Cortex A8 on the 45 nm feature size is reported to use 20-30% less than that. For a little bit of added beliveability, Qualcomm's Snapdragon sips in the vicinity of 0.5 mW per MHz on the 65 nm scale, though that may be under optimal circumstances / marketing spin.Ultimately it's roughly half the power consumption Moorestown is reporting. And we notice that nowhere does Intel actually compare their power consumption figures to ARM's.

Additionally, I was under the impression that the A4 had a dual-channel memory controller. I would guess LPDDR2 memory as well, but your guess is as good as mine.

I suspect the S5L8930 in the A4 is a PA Semi (remember Apple bought them) reworked Samsung S5PV210, the dual-channel controller tablet / MID-oriented sister chip to the Samsung Hummingbird S5PC110 (which uses a single-channel controller with LPDDR2 support, if my resources are to be trusted.)

pradeepcvk - Tuesday, November 1, 2011 - link

Anand liked your brief of S0Ix wrt Meego. I wonder how would it work with windows ACPI.could you please have an article for the same.