NVIDIA's Fermi: Architected for Tesla, 3 Billion Transistors in 2010

by Anand Lal Shimpi on September 30, 2009 12:00 AM EST- Posted in

- GPUs

Architecting Fermi: More Than 2x GT200

NVIDIA keeps referring to Fermi as a brand new architecture, while calling GT200 (and RV870) bigger versions of their predecessors with a few added features. Marginalizing the efforts required to build any multi-billion transistor chip is just silly, to an extent all of these GPUs have been significantly redesigned.

At a high level, Fermi doesn't look much different than a bigger GT200. NVIDIA is committed to its scalar architecture for the foreseeable future. In fact, its one op per clock per core philosophy comes from a basic desire to execute single threaded programs as quickly as possible. Remember, these are compute and graphics chips. NVIDIA sees no benefit in building a 16-wide or 5-wide core as the basis of its architectures, although we may see a bit more flexibility at the core level in the future.

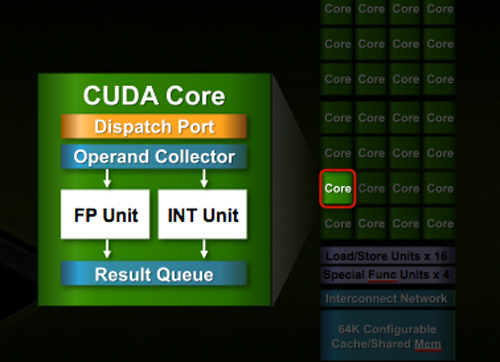

Despite the similarities, large parts of the architecture have evolved. The redesign happened at low as the core level. NVIDIA used to call these SPs (Streaming Processors), now they call them CUDA Cores, I’m going to call them cores.

All of the processing done at the core level is now to IEEE spec. That’s IEEE-754 2008 for floating point math (same as RV870/5870) and full 32-bit for integers. In the past 32-bit integer multiplies had to be emulated, the hardware could only do 24-bit integer muls. That silliness is now gone. Fused Multiply Add is also included. The goal was to avoid doing any cheesy tricks to implement math. Everything should be industry standards compliant and give you the results that you’d expect.

Double precision floating point (FP64) performance is improved tremendously. Peak 64-bit FP execution rate is now 1/2 of 32-bit FP, it used to be 1/8 (AMD's is 1/5). Wow.

NVIDIA isn’t disclosing clock speeds yet, so we don’t know exactly what that rate is yet.

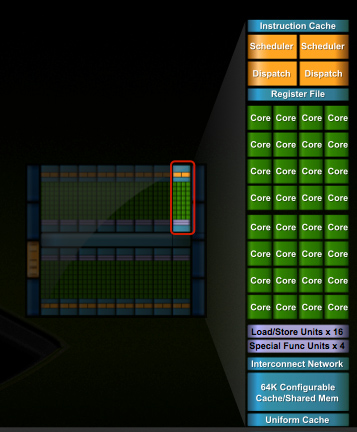

In G80 and GT200 NVIDIA grouped eight cores into what it called an SM. With Fermi, you get 32 cores per SM.

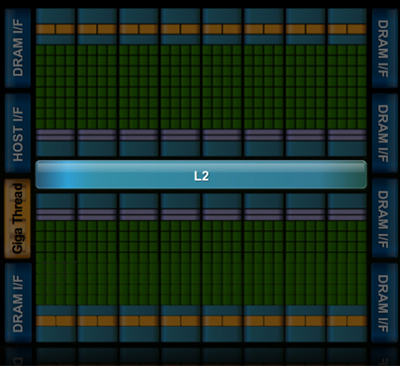

The high end single-GPU Fermi configuration will have 16 SMs. That’s fewer SMs than GT200, but more cores. 512 to be exact. Fermi has more than twice the core count of the GeForce GTX 285.

| Fermi | GT200 | G80 | |

| Cores | 512 | 240 | 128 |

| Memory Interface | 384-bit GDDR5 | 512-bit GDDR3 | 384-bit GDDR3 |

In addition to the cores, each SM has a Special Function Unit (SFU) used for transcendental math and interpolation. In GT200 this SFU had two pipelines, in Fermi it has four. While NVIDIA increased general math horsepower by 4x per SM, SFU resources only doubled.

The infamous missing MUL has been pulled out of the SFU, we shouldn’t have to quote peak single and dual-issue arithmetic rates any longer for NVIDIA GPUs.

NVIDIA organizes these SMs into TPCs, but the exact hierarchy isn’t being disclosed today. With the launch's Tesla focus we also don't know specific on ROPs, texture filtering or anything else related to 3D graphics. Boo.

A Real Cache Hierarchy

Each SM in GT200 had 16KB of shared memory that could be used by all of the cores. This wasn’t a cache, but rather software managed memory. The application would have to knowingly move data in and out of it. The benefit here is predictability, you always know if something is in shared memory because you put it there. The downside is it doesn’t work so well if the application isn’t very predictable.

Branch heavy applications and many of the general purpose compute applications that NVIDIA is going after need a real cache. So with Fermi at 40nm, NVIDIA gave them a real cache.

Attached to each SM is 64KB of configurable memory. It can be partitioned as 16KB/48KB or 48KB/16KB; one partition is shared memory, the other partition is an L1 cache. The 16KB minimum partition means that applications written for GT200 that require 16KB of shared memory will still work just fine on Fermi. If your app prefers shared memory, it gets 3x the space in Fermi. If your application could really benefit from a cache, Fermi now delivers that as well. GT200 did have an L1 texture cache (one per TPC), but the cache was mostly useless when the GPU ran in compute mode.

The entire chip shares a 768KB L2 cache. The result is a reduced penalty for doing an atomic memory op, Fermi is 5 - 20x faster here than GT200.

415 Comments

View All Comments

samspqr - Thursday, October 1, 2009 - link

ATI's availability will be sorted out soon, NVIDIA's weird design choices that are targeted at anything but graphics won'tin fact, I have just realized: NVIDIA IS DOING A MATROX!

(forget about graphics, concentrate in a proffessional niche, subsequently get run over by competitors in its former main market... eventually dissappear from the graphics market or become irrelevant? with some luck, RayTracing will be here sooner rather than later, ATI will switch to GPUcomputing at the right time -as opposed to very much too soon-, and we will have a 3 players market; until then, ATI domination all over)

andrihb - Thursday, October 1, 2009 - link

What a huge leap of the imagination :Psamspqr - Friday, October 2, 2009 - link

sorry, I was just trying to imagine how many weird things would have to happen so that we don't have a single GPU maker in the marketin any case, if you want some imaginative thinking, try here:

http://www.semiaccurate.com/2009/10/01/nvidia-fake...">http://www.semiaccurate.com/2009/10/01/nvidia-fake...

(I'm not sure yet who is the one making stuff up -charlie or nvidia-, but so far my bet would be on nvidia)

mindless1 - Saturday, October 3, 2009 - link

What they may have done is take an existing PCB design for something else, and tacked down the parts and air-wired them. It is a faster way to debug a prototype, as well as just drilling a few holes and putting makeshift screws in to test a cooling design before going to the effort of the rest of the support parts before you know if the cooling subsystem is adequate.IF that is the situation, I feel nVidia should have held off until they were further along with the prototypes, but when all is said and done if they can produce performance in line with the expectations, that would prove they had a working card.

IGoodwin - Friday, October 2, 2009 - link

First off, I don't know the truth about a fake or real Tesla being in existence; however, when an article shows a strong emotional bias, I do find it hard to accept the conclusions.Here is a link to the current Tesla product for sale online:

http://www.tigerdirect.com/applications/SearchTool...">http://www.tigerdirect.com/applications...tails.as...

This clearly shows the existing Tesla card with screws on the end plate. Also, if memory serves, having partial venting on a single slot for the new Tesla card would equal the cooling available on the ATI card. Also, six-pin connector is in roughly the same place.

As for the PCB, it is hidden on the older Tesla screen shots, so nothing can be derived.

The card may be fake, or not, but Charlie is not exactly unbiased either.

jonGhast - Saturday, October 3, 2009 - link

"but Charlie is not exactly unbiased either."What's the deal with that, I keep trying to read Semi's articles, though his 'tude towards MS and Intel is pretty juvenile, but I've got to ask; did somebody at Nvidia gang rape his mom?

mindless1 - Saturday, October 3, 2009 - link

I simply assume he is either directly or indirectly on ATI's payroll.Fudzilla wrote "The real engineering sample card is full of dangling wires." To display such a card to others they could simply epoxy down some connectors and solder the wires to them.

monomer - Friday, October 2, 2009 - link

Here's an article from Fudo saying that the card was a mock-up. Nvidia claimed it was real at the conference, and are now saying its a fake, but that they really, truly, had a real one running the demos. Really! I completely believe them.http://www.fudzilla.com/content/view/15798/1/">http://www.fudzilla.com/content/view/15798/1/

Yojimbo - Thursday, October 1, 2009 - link

What makes you think it isn't the right time? You can only really tell in hindsight, but you give in your post any reason that you think now is not the right time and later, when amd is gonna do it, is the right time. I think the right time is whenever the architecture is available and the interest is there. Nvidia has, over the past 5 years, been steadily building the architecture for it. Whether the tools are all in place yet and whether the interest is really there remains to be seen.It has nothing to do with matrox or any shift to a "professional niche." Nvidia believes that it has the ability to evolve and leverage its products from the niche sector of 3d graphics into a broader and more ubiquitous computing engine.

wumpus - Thursday, October 1, 2009 - link

Do you see any sign of commercial software support? Anybody Nvidia can point to and say "they are porting $important_app to openCL"? I haven't heard a mention. That pretty much puts Nvidia's GPU computing schemes solely in the realm of academia (where you can use grad students a cheap highly-skilled labor). If they could sell something like a FEA package for pro-engineer or solidworks, the things would fly off the shelves (at least I know companies who would buy them, but it might be more a location bias). If you have to code it yourself, that leaves either academia (which mostly just needs to look at hardware costs) and existing supercomputer users. The existing commercial users have both hardware and software (otherwise they would be "potential users"), and are unlikely to want to rewrite the software unless it is really, really, cheaper. Try to imagine all the salaries involved in running the big, big, jobs Nvidia is going after and tell me that the hardware is a good place to save money (at the cost of changing *everything*).I'd say Nvidia is not only killing the graphics (with all sorts of extra transistors that are in the way and are only for double point), but they aren't giving anyone (outside academia) any reason to use openCL. Maybe they have enough customers who want systems much bigger than $400k, but they will need enough of them to justify designing a >400mm chip (plus the academics, who are buying these because they don't have a lot of money).