The Dark Knight: Intel's Core i7

by Anand Lal Shimpi & Gary Key on November 3, 2008 12:00 AM EST- Posted in

- CPUs

Understanding Nehalem's Memory Architecture

Nehalem does spice things up a bit in the memory department, not only does it have an integrated memory controller (a first for an x86 Intel CPU) but the memory controller in question has an unusual three-channel configuration. All other AMD and Intel systems use dual channel DDR2 or DDR3 memory controllers; with each channel being 64-bits wide, you have to install memory in pairs for peak performance.

With a three-channel DDR3 memory controller, Nehalem requires the use of three DDR3 modules to achieve peak bandwidth - which also means that the memory manufacturers are going to be selling special 3-channel DDR3 kits made specifically for Nehalem. Motherboard makers will be doing one of two things to implement Nehalem's three-channel memory interface on boards; you'll either see boards with four DIMM slots or boards with six:

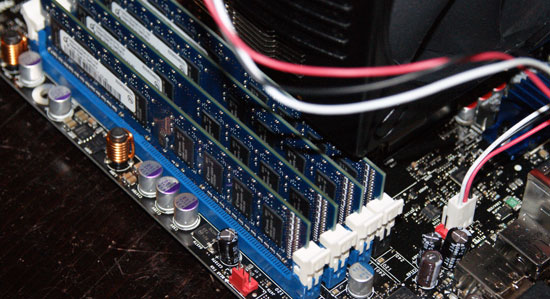

Four DDR3 slots, three DDR3 channels

In the four-slot configuration the first three slots correspond to the first three channels, the fourth slot is simply sharing one of the memory channels. The downside to this approach is that your memory bandwidth drops to single-channel performance as you start filling up your memory. For example, if you have 4 x 1GB sticks, the first 3GB of memory will be interleaved between the three memory channels and you'll get 25.6GB/s of bandwidth to data stored in the first 3GB. The final 1GB however won't be interleaved and you'll only get 8.5GB/s of bandwidth to it. Despite the unbalanced nature of memory bandwidth in this case, your aggregate bandwidth is still greater in this configuration than a dual-channel setup.

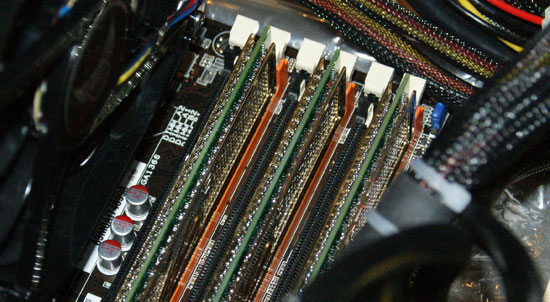

Six DDR3 slots, two slots per DDR3 channel

The more common arrangement will be six DIMM slots where each DDR3 channel is connected to a pair of DIMM slots. In this configuration as long as you install DIMMs in triplicate you'll always get the full 25.6GB/s of memory bandwidth.

That discussion is entirely theoretical however, the real question is: does Nehalem's triple-channel memory controller actually matter or would two channels suffice? I suspect that Hyper Threading simply improved Nehalem's efficiency not necessarily its need for more data. The three-channel memory controller is probably far more important for servers and will be especially useful in the upcoming 8-core version of Nehalem due out sometime next year. To find out we simply benchmarked Nehalem in a handful of applications with a 4GB/dual channel configuration and a 6GB/triple-channel configuration. Note that none of these tests actually used more than 4GB of memory so the size difference doesn't matter, we kept memory timings the same between all tests.

| Dual Channel DDR3-1066 (9-9-9-20) | Triple Channel DDR3-1066 (9-9-9-20) | |

| Memory Tests - Everest v1547 | ||

| Read Bandwidth | 12859 MB/s | 13423 MB/s |

| Write Bandwidth | 12410 MB/s | 12401 MB/s |

| Copy Bandwidth | 16474 MB/s | 18074 MB/s |

| Latency | 37.2 ns | 44.2 ns |

| Cinebench R10 (Multi-threaded test) | 18499 | 18458 |

| x264 HD Encoding Test (First Pass / Second Pass) | 83.8 fps / 30.3 fps | 85.3 fps / 30.3 fps |

| WinRAR 3.80 - 602MB Folder | 118 seconds | 117 seconds |

| PCMark Vantage | 7438 | 7490 |

| Vantage - Memories | 6753 | 6712 |

| Vantage - TV and Movies | 5601 | 5637 |

| Vantage - Gaming | 10202 | 9849 |

| Vantage - Music | 5378 | 4593 |

| Vantage - Communications | 6671 | 6422 |

| Vantage - Productivity | 7589 | 7676 |

| WinRAR (Built in Benchmark) | 3283 | 3306 |

| Nero Recode - Office Space - 7.55GB | 131 seconds | 130 seconds |

| SuperPI - 32M (mins:seconds) | 11:55 | 11:52 |

| Far Cry 2 - Ranch Medium (1680 x 1050) | 62.1 fps | 62.4 fps |

| Age of Conan - 1680 x 1050 | 51.5 fps | 51.1 fps |

| Company of Heroes - 1680 x 1050 | 136.6 fps | 133.6 fps |

At DDR3-1066 speeds we found no real performance difference between the Core i7-965 running in two channel vs. three channel mode, the added bandwidth is simply not useful for most desktop applications. For some reason we were able to get better latency scores on the dual-channel configuration, but there's a good chance that may be due to the early nature of BIOSes on these boards. In benchmarks were the latency difference was noticeable we saw the dual-channel configuration pull ahead slightly, then in other tests where the added bandwidth helped we saw the triple-channel configuration do better. Honestly, it's mostly a wash between the two.

Our recommendation would be to stick with three channels, but if you have existing memory and can't populate the third channel yet it's not a huge deal, really, two is fine here for the time being.

73 Comments

View All Comments

Kaleid - Monday, November 3, 2008 - link

http://www.guru3d.com/news/intel-core-i7-multigpu-...">http://www.guru3d.com/news/intel-core-i...and-cros...bill3 - Monday, November 3, 2008 - link

Umm, seems the guru3d gains are probably explained by them using a dual core core2dou versus quad core i7...Quad core's run multi-gpu quiet a bit better I believe.tynopik - Monday, November 3, 2008 - link

what about those multi-threading tests you used to run with 20 tabs open in firefox while running av scan while compressing some files while converting something else while etc etc?this might be more important for daily performance than the standard desktop benchmarks

D3SI - Monday, November 3, 2008 - link

So the low end i7s are OC'able?

what the hell is toms hardware talking about lol

conquerist - Monday, November 3, 2008 - link

Concerning x264, Nehalem-specific improvements are coming as soon as the developers are free from their NDA.See http://x264dev.multimedia.cx/?p=40">http://x264dev.multimedia.cx/?p=40.

Spectator - Monday, November 3, 2008 - link

can they do some CUDA optimizations?. im guessing that video hardware has more processors than quad core intel :PIf all this i7 is new news and does stuff xx faster with 4 core's. how does 100+ core video hardware compare?.

Yes im messing but giant Intel want $1k for best i7 cpu. when likes of nvid make bigger transistor count silicon using a lesser process and others manufacture rest of vid card for $400-500 ?

Where is the Value for money in that. Chukkle.

gramboh - Monday, November 3, 2008 - link

The x264 team has specifically said they will not be working on CUDA development as it is too time intensive to basically start over from scratch in a more complex development environment.npp - Monday, November 3, 2008 - link

CUDA Optimizations? I bet you don't understand completely what you're talking about. You can't just optimize a piece of software for CUDA, you MUST write it from scratch for CUDA. That's the reason why you don't see too much software for nVidia GPUs, even though the CUDA concept was introduced at least two years ago. You have the BadaBOOM stuff, but it's far for mature, and the reason is that writing a sensible application for CUDA isn't exactly an easy task. Take your time to look at how it works and you'll understand why.You can't compare the 100+ cores of your typical GPU with a quad core directly, they are fundamentaly different in nature, with your GPU "cores" being rather limited in functionality. GPGPU is a nice hype, but you simply can't offload everything on a GPU.

As a side note, top-notch hardware always carries price premium, and Intel has had this tradition with high-end CPUs for quite a while now. There are plenty of people who need absolutely the fastest harware around and won't hesitate paying it.

Spectator - Monday, November 3, 2008 - link

Some of us want more info.A) How does the integrated Thermal sensor work with -50+c temps.

B) Can you Circumvent the 130W max load sensor

C) what are all those connection points on the top of the processor for?.

lol. Where do i put the 2B pencil to. to join that sht up so i dont have to worry about multiply settings or temp sensors or wattage sensors.

Hey dont shoot the messenger. but those top side chip contacts seem very curious and obviously must serve a purpose :P

Spectator - Monday, November 3, 2008 - link

Wait NO. i have thought about it..The contacts on top side could be for programming the chips default settings.

You know it makes sence.Perhaps its adjustable sram style, rather than burning connections.

yes some technical peeps can look at that. but still I want the fame for suggesting it first. lmao.

Have fun. but that does seem logical to build in some scope for alteration. alot easier to manufacture 1 solid item then mod your stock to suit market when you feel its neccessary.

Spectator.