Imagination Launches Catapult Family of RISC-V CPU Cores: Breaking Into Heterogeneous SoCs

by Ryan Smith on December 6, 2021 11:00 AM EST- Posted in

- SoCs

- CPUs

- Imagination Technologies

- RISC-V

- Catapult

December is here, and with it comes several technical summits ahead of the holiday break. The most notable of which this week is the annual RISC-V summit, which is being put on by the Linux Foundation and sees the numerous (and ever increasing) parties involved in the open source ISA gather to talk about the latest products and advancements in the RISC-V ecosystem. The summit always tends to feature some new product announcements, and this year is no different, as Imagination Technologies is at the show to provide details on their first RISC-V CPU cores, along with announcing their intentions to develop a full suite of CPU cores over the next few years.

The company, currently best known for their PowerVR GPU lineup, has been dipping their toes into the RISC-V ecosystem for the last couple of years with projects like RVfpga. More recently, this past summer the company revealed in an earnings call that they would be designing RISC-V CPU cores, with more details to come. Now at the RISC-V summit they’re providing those details and more, with the formal announcement of their Catapult family of RISC-V cores, as well as outlining a heterogeneous computing-centric roadmap for future development.

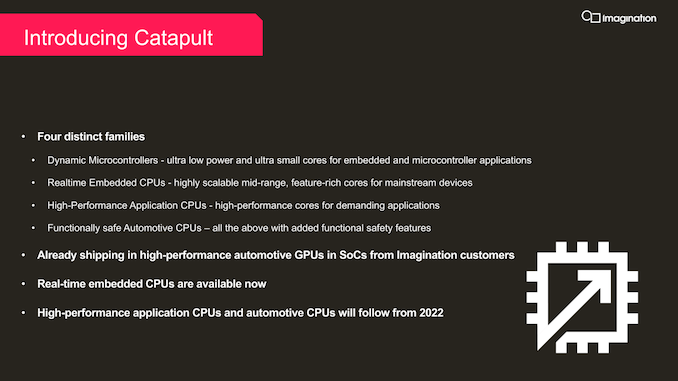

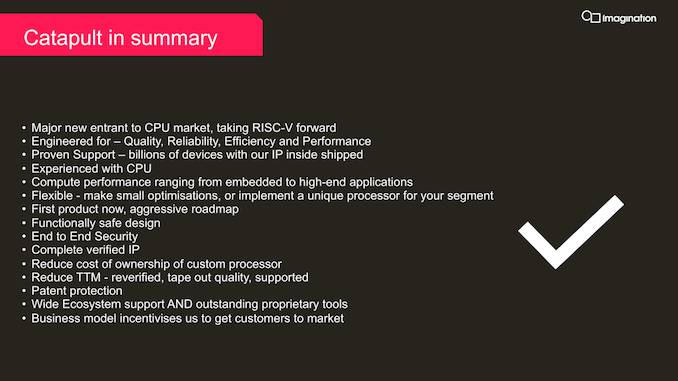

Starting from the top, the Catapult family is Imagination’s overarching name for a complete family of RISC-V CPU cores, the first of which are launching today. Imagination has (and is) designing multiple microarchitectures in order to cover a broad range of performance/power/area (PPA) needs, and the Catapult family is slated to encompass everything from microcontroller-grade processors to high-performance application processors. All told, Imagination’s plans for the fully fleshed out Catapult family look a lot like Arm’s Cortex family, with Imagination preparing CPU core designs for microcontrollers (Cortex-M), real-time CPUs (Cortex-R), high performance application processors (Cortex-A), and functionally safe CPUs (Cortex-AE). Arm remains the player to beat in this space, so having a similar product structure should help Imagination smooth the transition for any clients that opt to disembark for Catapult.

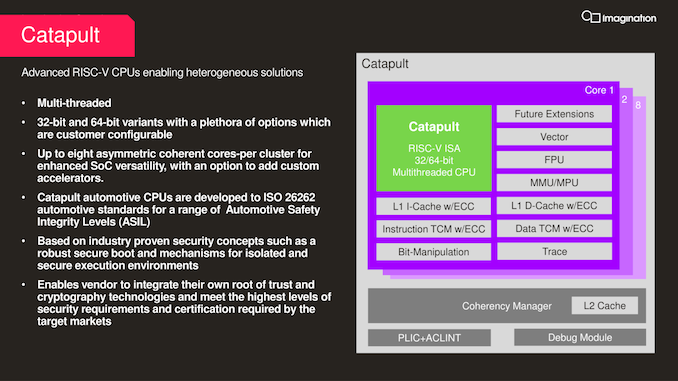

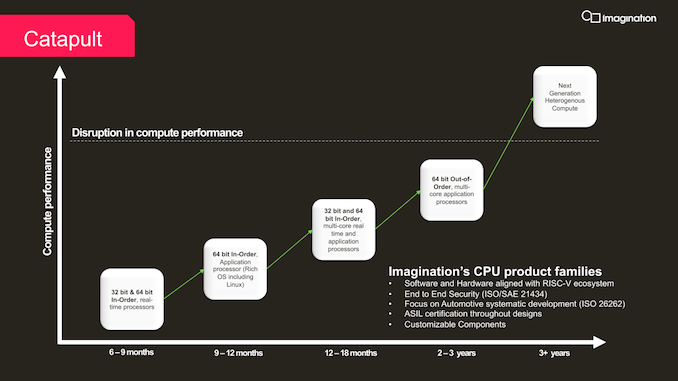

At present, Imagination has finished their first CPU core design, which is a simple, in-order core for 32-bit and 64-bit systems. The in-order Catapult core is being used for microcontrollers as well as real-time CPUs, and according to the company, Catapult microcontrollers are already shipping in silicon as part of automotive products. Meanwhile the real-time core is available to customers as well, though it’s not yet in any shipping silicon.

The current in-order core design supports up to 8 cores in a single cluster. The company didn’t quote any performance figures, though bear in mind this is a simple processor meant for microcontrollers and other very low power devices. Meanwhile, the core is available with ECC across both its L1 and TCM caches, as well as support for some of RISC-V’s brand-new extensions, such as the Vector computing extension, and potentially other extensions should customers ask for them.

Following the current in-order core, Imagination has essentially three more core designs on their immediate roadmap. For 2022 the company is planning to release an enhanced version of the in-order core as an application processor-grade design, complete with support for “rich” OSes like Linux. And in 2023 that will be followed by another, even higher performing in-order core for the real-time and application processor markets. Finally, the company is also developing a much more complex out-of-order RISC-V core design as well, which is expected in the 2023-2024 timeframe. The out-of-order Catapult would essentially be their first take on delivering a high-performance RISC-V application processor, and like we currently see with high-performance cores the Arm space, has the potential to become the most visible member of the Catapult family.

Farther out still are the company’s plans for “next generation heterogeneous compute” designs. These would be CPU designs that go beyond current heterogeneous offerings – namely, just placing CPU, GPU, and NPU blocks within a single SoC – by more deeply combining these technologies. At this point Imagination isn’t saying much more, but they are making it clear that they aren’t just going to stop with a fast CPU core.

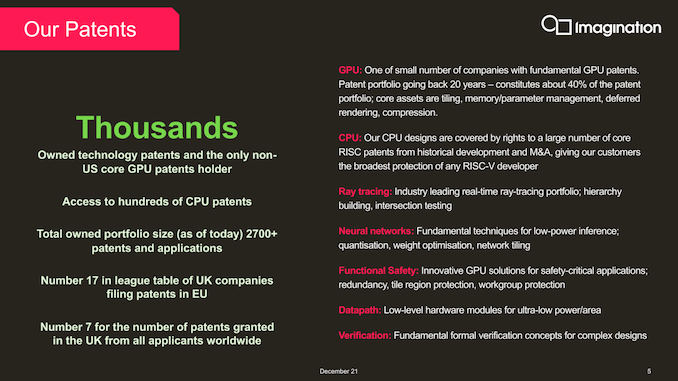

Overall, these are all clean room designs for Imagination. While the company has long since sold off its Meta and MIPS CPU divisions, it still retains a lot of the engineering talent from those efforts – along with ownership of or access to a large number of patents from the area. So although they aren’t reusing anything directly from earlier designs, they are hoping to leverage their previous experience to build better IP sooner.

Of course, CPU cores are just one part of what it will take to succeed in the IP space; besides incumbent Arm, there are also multiple other players in the RISC-V space, such as SiFive, who are all vying for much of the same market. So Imagination needs to both differentiate themselves from the competition, and offer some kind of market edge to customers.

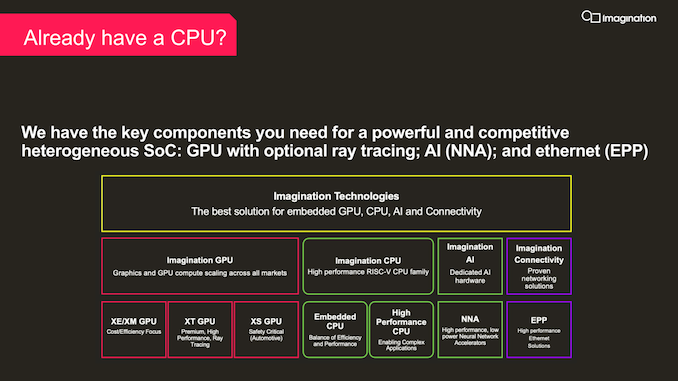

To that end, Imagination is going to be heavily promoting the possibilities for heterogenous computing designs with their IP. Compared to some of the other RISC-V CPU core vendors, Imagination already has well-established GPU and NPU IP, so customers looking to put together something more than just a straight CPU will be able to tap into Imagination’s larger library of IP. This does put the company more in direct competition with Arm (who already has all of these things as well), but then that very much seems to be Imagination’s goal here.

Otherwise, Imagination believes that their other big advantage in this space is the company’s history and location. As previously mentioned, Imagination holds access to a significant number of patents; so for clients who want to avoid extra patent licensing, they can take advantage of the fact that Imagination’s IP already comes indemnified against those patents. Meanwhile for chip designers who are based outside of the US and are weary of geopolitical issues affecting ongoing access to IP, Imagination is naturally positioned as an alternative there since they aren’t based in the US either – and thus access to their IP can’t be cut off by the US.

Wrapping things up, with the launch of their Catapult family of RISC-V CPU IP, imagination is laying out a fairly ambitious plan for the company for the next few years. By leveraging both their previous experience building CPUs as well as their current complementary IP like GPUs and NPUs, Imagination has their sights set on becoming a major player in the RISC-V IP space – and particularly when it comes to heterogeneous compute. Ultimately a lot will need to go right for the company before they can get there, but if they can succeed, then with their diverse collection of IP they would be in a rather unique position among RISC-V vendors.

Source: Imagination Technologies

62 Comments

View All Comments

TeXWiller - Tuesday, December 7, 2021 - link

Take a look at the IBM's A2 cores and the RS64-II for example, or Sun's T-series. I think it's good to think SMT as a larger concept that what Intel's HT was.mode_13h - Wednesday, December 8, 2021 - link

> what Intel's HT was.You mean "is"? AFAIK, the widest Intel ever went with SMT (in x86) is 4-way, in the Knights Landing generation of Xeon Phi.

In their GPUs, they went 7-way for a while (including Gen 9, introduced with Skylake). I forget if it's still 7-way in Gen11, but I'm pretty sure they haven't disclosed how many in Xe.

MrHorizontal - Thursday, December 9, 2021 - link

I think the intention is to get to an OOO design. However, in order vs out of order isn't as important to a RISC ISA vs a CISC ISA - but it will have a small increase in a chip's efficiency. One of the basic paradigms of an OOO design is it effectively acts like a hardware thread scheduler on the CPU so it uses resources more efficiently - therefore far more important to a CISC design like x86. With RISC, it's more a situation of getting the data to the processing pipeline and be done with it, more like in a GPU design, so it's better to parallelize a lot of RISC cores than make them bigger.It goes back to the old comparisons between CISC and RISC. With CISC, fewer bigger cores are necessary. With RISC more simpler cores to spread the load. With RISC designs it's mostly a question of keeping the pipeline as short as possible (it's already magnitudes shorter than CISC, but feature bloat, particularly with variable-width instructions...) and the fact that RISC is much more sensitive to clockspeeds than CISC... there's an argument however that we're in the age where we're at the limits of clockspeeds on silicon irrespective of ISA so the value of CISC vs RISC is mooted. What's far important is small, simple cores and lots and lots of them.

On that basis out-vs-in order rather takes a back seat.

Oxford Guy - Thursday, December 9, 2021 - link

‘What's far important is small, simple cores and lots and lots of them.’Isn’t that quite workload-specific?

mode_13h - Friday, December 10, 2021 - link

Yeah, it depends on what market Imagination has in mind for these. As you can see from slides shown in the article, not all cores are advertised as supporting a "Rich OS". Others are labelled as "real-time processors".In an RTOS, threads are often used as a basic construct for prioritization and service guarantees. That implies applications using them are likely to be more heavily-threaded. Nvidia's latest self-driving SoC (Orin) has 12 ARM cores.

FunBunny2 - Tuesday, December 14, 2021 - link

"Isn’t that quite workload-specific?"whatever happened that machine that would parallelize sequential on the fly, and ship it as many cores as available? fact is, there still aren't all that many embarrassingly parallel problems. yes, in the innterTubes world servicing scads of independent connections is a worthy goal. just not the same thing.

mode_13h - Saturday, December 18, 2021 - link

> whatever happened that machine that would parallelize sequential on the flyYou mean Soft Machines / VISC?

https://www.theregister.com/2016/09/09/intel_soft_...

More: https://www.anandtech.com/show/10025/examining-sof...

> there still aren't all that many embarrassingly parallel problems.

Well, the HTML rendering engines in web browsers seem to have been parallelized for quite a while. I think a lot of apps parallelize rather well, if you can just reduce the communication & synchronization overhead by enough.

mode_13h - Friday, December 10, 2021 - link

> One of the basic paradigms of an OOO design is> it effectively acts like a hardware thread scheduler

Um... a little bit, I suppose. However, unless you're talking about scheduling instructions from different SMT threads, they operate at *completely* different scales.

> It goes back to the old comparisons between CISC and RISC.

I think you're right about one thing, which is that RISC simplifies the decoder, enabling a smaller minimum core size. And yes, that means perf/area should scale better, as you add more of them.

> RISC is much more sensitive to clockspeeds than CISC

Simple RISC uArchs are. When they get sufficiently complex, that stops being true.

> With RISC designs it's mostly a question of keeping the pipeline as short as possible

> (it's already magnitudes shorter than CISC

A few stages shorter, at most. You really shouldn't base so many assumptions on 30+ -year-old orthodoxy -- it will only lead you astray. Please compare specifics of some more modern CPUs.

Zoolook - Monday, December 13, 2021 - link

Back when there was a RISC vs CISC discussion we didn't have multicores, so yeah it feels a bit strange.mode_13h - Friday, December 10, 2021 - link

This week, the Linux Foundation held a RISC-V Summit. Since it's not being reported in Anandtech's news feed, you can see for yourself what it included:https://events.linuxfoundation.org/riscv-summit/pr...