AMD Threadripper Pro Review: An Upgrade Over Regular Threadripper?

by Dr. Ian Cutress on July 14, 2021 9:00 AM EST- Posted in

- CPUs

- AMD

- ThreadRipper

- Threadripper Pro

- 3995WX

CPU Tests: Microbenchmarks

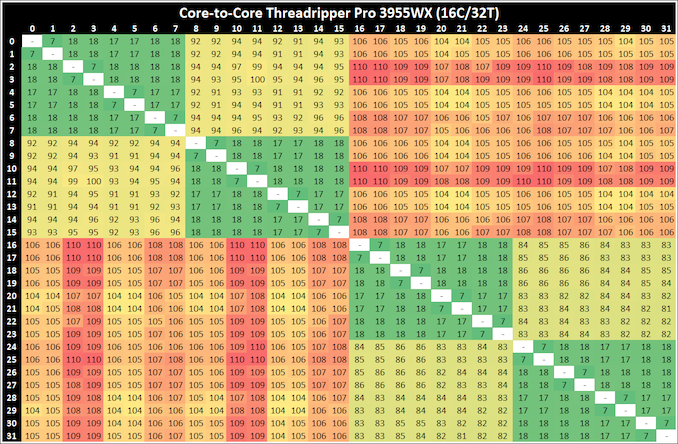

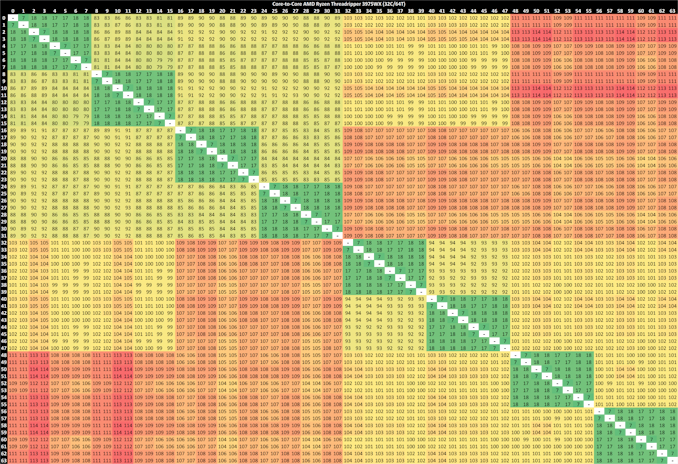

Core-to-Core Latency

As the core count of modern CPUs is growing, we are reaching a time when the time to access each core from a different core is no longer a constant. Even before the advent of heterogeneous SoC designs, processors built on large rings or meshes can have different latencies to access the nearest core compared to the furthest core. This rings true especially in multi-socket server environments.

But modern CPUs, even desktop and consumer CPUs, can have variable access latency to get to another core. For example, in the first generation Threadripper CPUs, we had four chips on the package, each with 8 threads, and each with a different core-to-core latency depending on if it was on-die or off-die. This gets more complex with products like Lakefield, which has two different communication buses depending on which core is talking to which.

If you are a regular reader of AnandTech’s CPU reviews, you will recognize our Core-to-Core latency test. It’s a great way to show exactly how groups of cores are laid out on the silicon. This is a custom in-house test built by Andrei, and we know there are competing tests out there, but we feel ours is the most accurate to how quick an access between two cores can happen.

On all our Threadripper Pro CPUs, we saw:

- a thread-to-thread latency of 7ns,

- a core-to-core in the same CCX latency as 17-18 nanoseconds,

- a core-to-core in a different CCX scale from 80 ns with no IO die hops to 113 with 3 IO die hops

Here we can distinuguish how long it takes for threads to ping back and forth with cores that are different hops across the IO die.

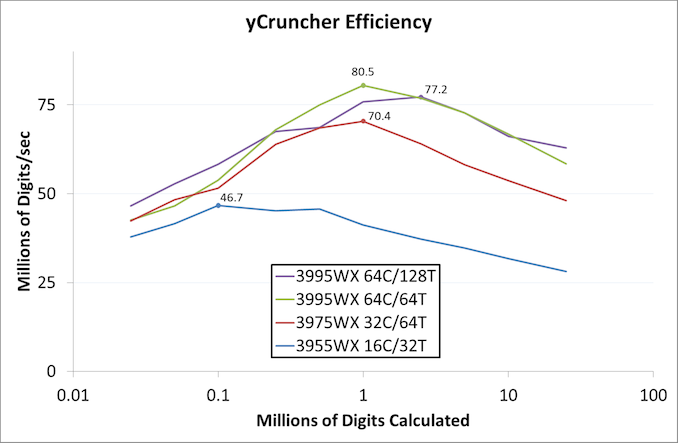

A y-Cruncher Sprint

The y-cruncher website has a large about of benchmark data showing how different CPUs perform to calculate specific values of pi. Below these there are a few CPUs where it shows the time to compute moving from 25 million digits to 50 million, 100 million, 250 million, and all the way up to 10 billion, to showcase how the performance scales with digits (assuming everything is in memory). This range of results, from 25 million to 250 billion, is something I’ve dubbed a ‘sprint’.

I have written some code in order to perform a sprint on every CPU we test. It detects the DRAM, works out the biggest value that can be calculated with that amount of memory, and works up from 25 million digits. For the tests that go up to the ~25 billion digits, it only adds an extra 15 minutes to the suite for an 8-core Ryzen CPU.

With this test, we can see the effect of increasing memory requirements on the workload and the scaling factor for a workload such as this. We're plotting milllions of digits calculated per second.

The 64C/64T processor obtains the peak efficiency here, although as more digits are calculated, the memory requirements come into play.

98 Comments

View All Comments

Rocket_Scientist - Friday, July 16, 2021 - link

I want to know who spends 5 grand on a processor but doesn't spend the few extra dollars to utilize all 8 memory channels!Mikewind Dale - Friday, July 16, 2021 - link

The 3955WX processor "only" costs $1,150, while each stick of 64 GB RAM costs $350.And I wanted to keep some empty slots in case 128 GB RDIMMs became affordable. But I didn't know that using 6 channels would cause so much performance degradation.

mode_13h - Saturday, July 17, 2021 - link

> who spends 5 grand on a processor but doesn't spend> the few extra dollars to utilize all 8 memory channels!

Although I tend to agree, the article did reveal some benchmarks where the additional bandwidth provides negligible benefit.

lmh - Tuesday, July 27, 2021 - link

Can you share what memory bandwidth you actually measured in the 3955WX 8-channel configuration?McFig - Wednesday, July 14, 2021 - link

There’s an error in the table “AMD 32-Core Zen 2 Comparison”: The MSRPs are mixed up.McFig - Wednesday, July 14, 2021 - link

Also: “code bath”; “Undreal” (I’m guessing should be “Unreal”?); “but also the updates” (e.g. could be “but also there were significant updates”)SarahKerrigan - Wednesday, July 14, 2021 - link

I kind of like "Code Bath."Threska - Wednesday, July 14, 2021 - link

" This is part of AMD’s guaranteed supply chain process, allowing OEMs to hard lock processors into certain vendors for supply chain end-to-end security that is requested by specific customers."I ASSUME that's a feature a certain OS vendor can't access.

"Only select vendors seem to have access/licenses to make WRX80 motherboards, and your main options are:"

I've seen the Giga offered as a burn-in special with a bundled processor, making it a better deal. The Asus is nice but I have to wonder if it's worth all the features.

DesireeTR - Wednesday, July 14, 2021 - link

No, It's worse. There's article about AMD Platform Secure Boot Feature (PSB) by servethehome together with Dell EMC. It basically burns permanently a public key of the OEM into the EPYC processor. It creates a guarantee that both motherboard and processor are not tampered. If you move your processor from OEM A that enabled PSB to motherboard of OEM B, AMD Secure Processor considers that as tampering and stops it working. The reverse is true.Some OEM are very strict (Dell EMC does this by hardware burn-in), some are less strict (HPE use

DesireeTR - Wednesday, July 14, 2021 - link

HPE only locks the public key in the firmware, and perform tamper check on BIOS only). And I guess before long, all PRO processor might get the same PSB feature too.