Update: PCI Express 6.0 Draft 0.71 Released, Final Release by End of Year

by Ryan Smith on July 2, 2021 7:00 AM EST- Posted in

- CPUs

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

Update 07/02: Albeit a couple of days later than expected, the PCI-SIG has announced this morning that the PCI Express draft 0.71 specification has been released for member review. Following a minimum 30 day review process, the group will be able to publish the draft 0.9 version of the specficiation, putting them on schedule to release the final version of the spec this year.

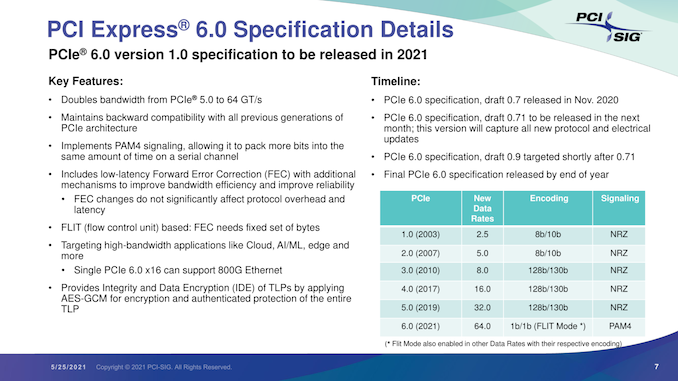

Originally Published 05/25

As part of their yearly developer conference, the PCI Special Interest Group (PCI-SIG) also held their annual press briefing today, offering an update on the state of the organization and its standards. The star of the show, of course, was PCI Express 6.0, the upcoming update to the bus standard that will once again double its data transfer rate. PCI-SIG has been working on PCIe 6.0 for a couple of years now, and in a brief update, confirmed that the group remains on track to release the final version of the specification by the end of this year.

The most recent draft version of the specification, 0.7, was released back in November. Since then, PCI-SIG has remained at work collecting feedback from its members, and is gearing up to release another draft update next month. That draft will incorporate the all of the new protocol and electrical updates that have been approved for the spec since 0.7.

In a bit of a departure from the usual workflow for the group, however, this upcoming draft will be 0.71, meaning that PCIe 6.0 will be remaining at draft 0.7x status for a little while longer. The substance of this decision being that the group is essentially going to hold for another round of review and testing before finally clearing the spec to move on to the next major draft. Overall, the group’s rules call for a 30-day review period for the 0.71 draft, after which the group will be able to release the final draft 0.9 specification.

Ultimately, all of this is to say that PCIe 6.0 remains on track for its previously-scheduled 2021 release. After draft 0.9 lands, there will be a further two-month review for any final issues (primarily legal), and, assuming the standard clears that check, PCI-SIG will be able to issue the final, 1.0 version of the PCIe 6.0 specification.

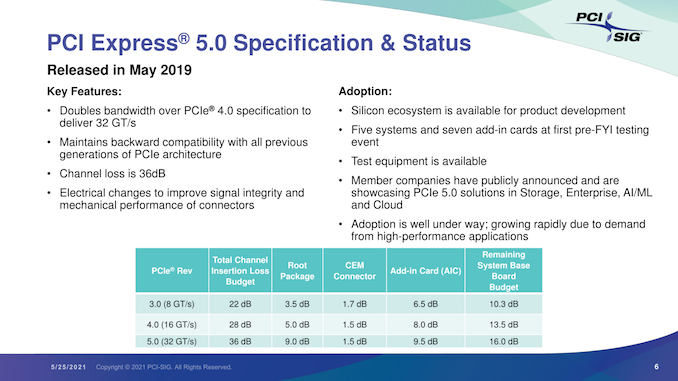

In the interim, the 0.9 specification is likely to be the most interesting from a technical perspective. Once the updated electrical and protocol specs are approved, the group will be able to give some clearer guidance on the signal integrity requirements for PCIe 6.0. All told we’re not expecting much different from 5.0 (in other words, only a slot or two on most consumer motherboards), but as each successive generation ratchets up the signaling rate, the signal integrity requirements have tightened.

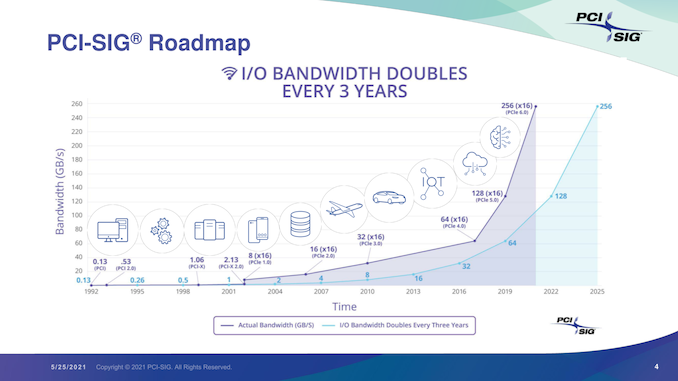

Overall, the unabashedly nerdy standards group is excited about the 6.0 standard, comparing it in significance to the big jump from PCIe 2.0 to PCIe 3.0. Besides proving that they’re once again able to double the bandwidth of the ubiquitous bus, it will mean that they’ve been able to keep to their goal of a three-year cadence. Meanwhile, as the PCIe 6.0 specification reaches completion, we should finally begin seeing the first PCIe 5.0 devices show up in the enterprise market.

103 Comments

View All Comments

Davdoc - Wednesday, July 21, 2021 - link

VESA local bus came before PCI, but, sorry to nitpick, the way you described it is as if VESA local bus came after PCI. Theoretical bandwidth wise VESA can go higher than the lowest iteration of PCI, indeed.I am unfortunately old enough to witness those transitions.

Kamen Rider Blade - Tuesday, May 25, 2021 - link

https://en.wikipedia.org/wiki/PCI_ExpressThe PCIe standards support: ×1, ×2, ×4, ×8, ×12, ×16, & ×32 lane implementations

Yet I don't see nearly as much support for ×2, ×12, & ×32 implementations.

Even in BiFurication of a ×16 port into ×12 + ×4.

I wish more vendors follow the PCIe spec and truly implement support across the board for all lane configs properly, not just the popular ones.

DigitalFreak - Tuesday, May 25, 2021 - link

There's not a need for PCIe x32 outside of servers, where they're used for riser cards. PCIe x2 doesn't really make sense and was only really used for cheap SSDs. x12 might make sense in a BiFurcation situation for x12 GPU and an x4 SSD, but now that both AMD and Intel already have a CPU x4 lane dedicated for SSDs it's not going to happen.Kamen Rider Blade - Tuesday, May 25, 2021 - link

But, the CPU x4 lane should be dedicated as the OS drive.The BiFuricated x12 + x4 = GPU + Game Drive where the Game Drive could have DMA to the GPU's RAM, ergo lowering latency & power requirements for sending data from the game to the GPU.

brucethemoose - Wednesday, May 26, 2021 - link

If you need 2 SSDs, and you need the game ssd directly connected the CPU in the future, the OS drive would be fine hanging off the chipset.If you REALLY need multiple SSDs all directly connected to the CPU, well, that's what HEDT is for.

mode_13h - Wednesday, May 26, 2021 - link

> Even in BiFurication of a ×16 port into ×12 + ×4.Dude, it's just "bifurcation".

https://en.wiktionary.org/wiki/bifurcate

The Von Matrices - Friday, July 2, 2021 - link

PCIe x2 is widespread, just not in slot form. In addition to some SSDs, a lot of integrated chips on motherboards use PCIe x2. For example, the ubiquitous ASMedia USB-C controllers all use PCIe x2.The Von Matrices - Friday, July 2, 2021 - link

x2 and x12 don't make sense in slot form because if you look at the pinout of the PCIe slot, an x2 or x12 card couldn't be made any smaller than an x4 or x16 card, respectively.ballsystemlord - Tuesday, May 25, 2021 - link

Spelling and grammar errors:"Meanwhile, as the PCIe 6.0 specification reaches competition, ..."

Competition, eh? With CXL maybe? I think you meant "completion".

"Meanwhile, as the PCIe 6.0 specification reaches completion, ..."

ballsystemlord - Tuesday, May 25, 2021 - link

Addendum: I didn't read the whole article.