Arm Announces Mobile Armv9 CPU Microarchitectures: Cortex-X2, Cortex-A710 & Cortex-A510

by Andrei Frumusanu on May 25, 2021 9:00 AM EST- Posted in

- SoCs

- CPUs

- Arm

- Smartphones

- Mobile

- Cortex

- ARMv9

- Cortex-X2

- Cortex-A710

- Cortex-A510

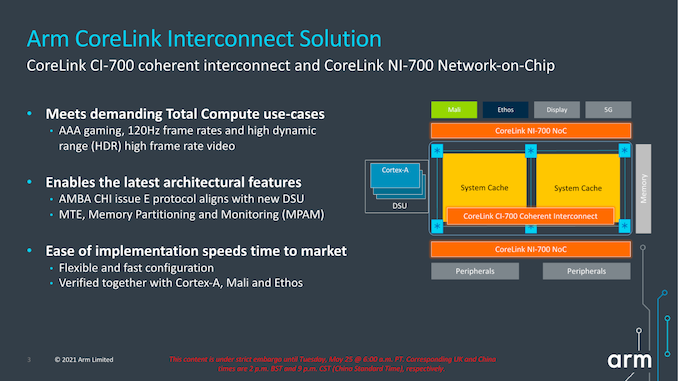

A new CI-700 Coherent Interconnect & NI-700 NoC For SoCs

Finally, the last new announcement of the day is a new interconnect and network-on-chip generation. The last time Arm had announced a mobile/client interconnect was back in in 2015 with the CCI-550. The reason for the large gap between IPs, in Arm’s own words, is that ever since Arm’s introduction of the DSU in its CPU complexes, there really hasn’t been any need for a cache coherent interconnect in the market. While that’s eyebrow-raising from a GPU perspective, it makes perfect sense from a CPU perspective, as coherency between CPU cores was the primary driver for such interconnects until then.

With the advent of new more complex computing platforms, such as NPUs, accelerators, and hopeful more use of GPUs in cache-coherent fashions, Arm saw a need gap in its portfolio and decided to update its client-side interconnect IP.

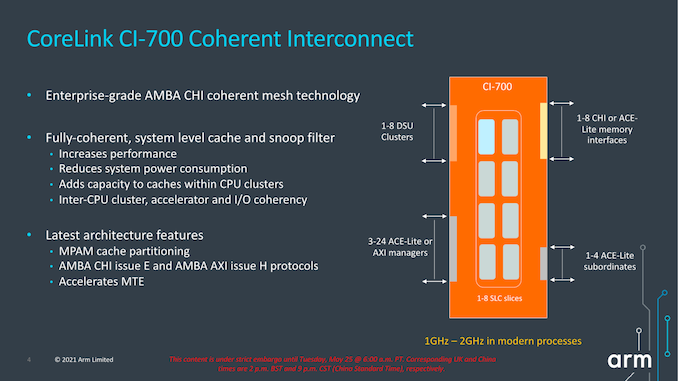

The new CI-700 is a mobile and client optimised variant of Arm’s infrastructure CMN mesh network, implementing important new interoperability with the new IP announced today, such as the new DSU or CPU cores.

The new mesh interconnect scales up from 1 to 8 DSU clusters, and supports up to 8 memory controllers, and also introduces innovations such as a system level cache.

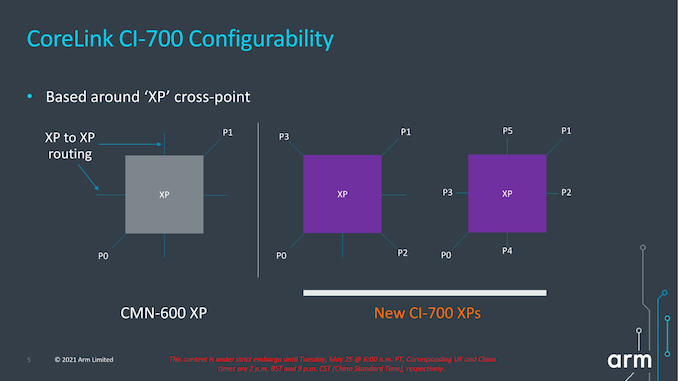

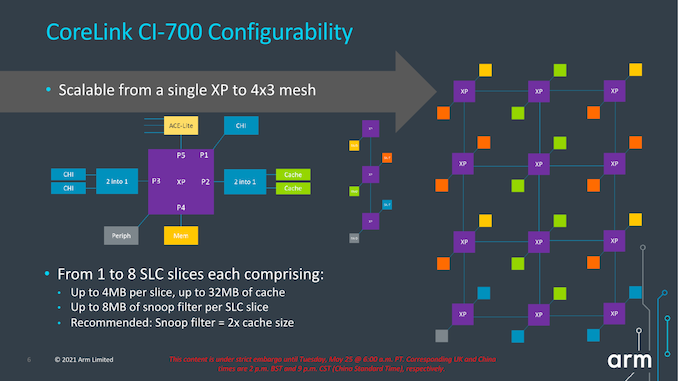

The mesh network topology and building blocks is very similar to what we’ve seen in the CMN infrastructure IP, in that “points” in the mesh are comprised of “cross-points” or “XP”. One differentiation that’s unique to the client mesh implementation is that XPs can have more attached connectivity ports, trading in routing connection paths. The new IP can also be configured as just a sole XP with no real mesh so to speak of, or essentially a 1x1 mesh configuration. This can grow up to a 4x3 mesh in the largest possible configuration.

The mesh supports from 1 to 8 SLC slices, with up to 4MB per slice for a total of 32MB, and snoop filter SRAM with coverage of up to 8MB address space per slice. It’s noted that generally Arm recommends 1.5-2x of coverage of the underlying private cache hierarchies of the mesh clients.

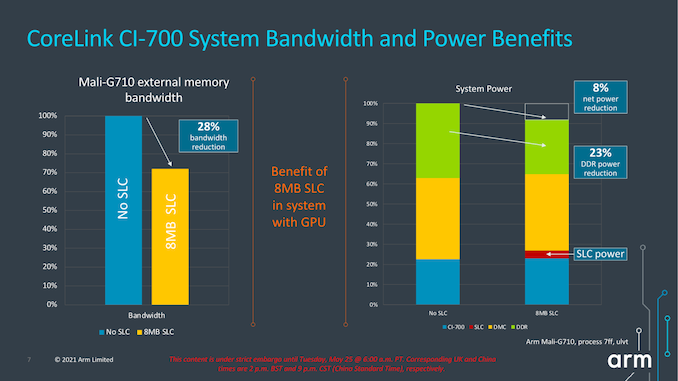

The SLC can server as both a bandwidth amplifier as well as reducing external memory/DRAM transactions, reducing system power reduction.

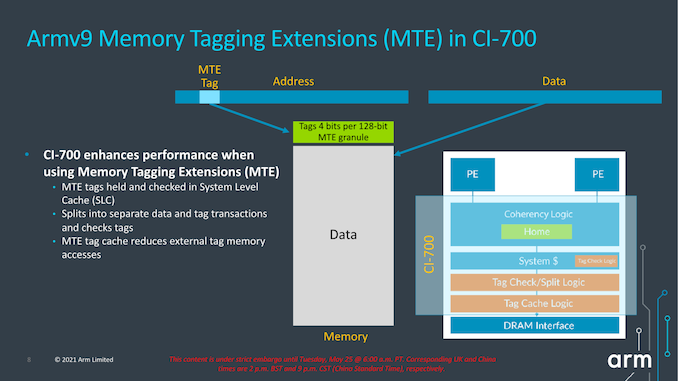

We see a reiteration of the support for MTE, allowing for this generation of IPs to support the feature across the new CPU IP, the DSU, and the new cache coherent interconnect.

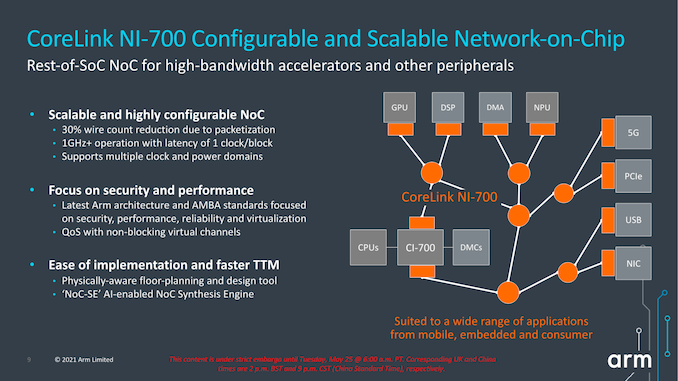

Alongside the new CI-700 coherent interconnect, we’re also seeing a new NI-700 network-on-chip for non-coherent data transfers between a SoC’s various IP blocks. The big new improvements here is the introduction of packetization for data transfers, which leads to a reduction of wires and thus improves area efficiency of the NoC on the SoC.

Overall, the new system IP announced today is very interesting, but the one question that’s one has to ask oneself is exactly who these net interconnects are meant for. Over the last few years, we’ve seen essentially every major mobile vendor roll out their own in-house cache-coherent interconnect IP, such as Samsung’s SCI or MediaTek’s MCSI, and other times we don’t see vendors talk about their in-house interconnects at all (Qualcomm). Due to almost everybody having their own IP, I’m not sure what the likelihood would be that any of the big players would jump back to Arm’s own solutions – if somebody were to adopt it, it would rather be amongst the smaller name vendors and newcomers to the market. From a business and IP portfolio perspective, the new designs make a lot of sense and allows to have the building blocks to create a mostly Arm-only SoC, which is an important item to have on the menu for Arm’s more diverse customer base.

181 Comments

View All Comments

ikjadoon - Tuesday, May 25, 2021 - link

Fair; I'll take a K12 successor as recompense.The business side is good context I forgot, but now in 2021, AMD is in much better straits and surely K12's successor is worth a shot.

https://www.anandtech.com/show/7990/amd-announces-...

Surely there were great ideas in Keller's work, their team's work, in their post-Styx designs

AMD might find a lot of benefit in preparing an Arm roadmap. What's to stop consoles, laptops, desktops from switching to Arm, from AMD"s financial perspective? Hopefully, they have clear eyes on x86's relevance to both consumers & businesses. AMD has a knack for fighting back, so I hope the build on their financial momentum.

TheinsanegamerN - Wednesday, May 26, 2021 - link

Compatibility, performance, and existence.ARM brings compatibility issues with previously existing software. Emulation wont work 100%,a nd compatibility with existing hardware is a minefield

With that emulation/compatibility layer comes performance degregations. Sometimes it may not be so bad, other times it will be horrendous. The overall software market is not as tightly controlled as apple's walled garden approach.

And finally, existence. There is currently no high performance ARM processor in existence. Show me a desktop ARM process ro that could replace a 5900x or a 10900k. How about one that could replace the CPU in the PS5? Currently one does not exist. You could say one exists for laptops, but that is only available for apple.

mode_13h - Thursday, May 27, 2021 - link

> There is currently no high performance ARM processor in existence.There are probably a dozen ARM server processors on the market or still in service that would fit a reasonable definition of high-performance.

> Show me a desktop ARM processor that could replace a 5900x or a 10900k.

I see you stuck that word "desktop" in there. Desktop is probably the last market ARM would penetrate. So, if your point is that you won't take ARM seriously until there's a competitive ARM-based desktop offering, that's like reaching for the fire extinguisher once you're surrounded by flames instead of when you first smell smoke.

I'm eager to see what V1-based CPUs look like. Those cores could make for a viable workstation CPU.

mode_13h - Tuesday, May 25, 2021 - link

And don't forget about Chinese designs (although this one is mentioned as being A72-derived):https://en.wikichip.org/wiki/hisilicon/microarchit...

SarahKerrigan - Tuesday, May 25, 2021 - link

The KP920 core isn't A72 derived. It says "from A72" but all it's saying there is that its predecessor used A72's - it's not saying the core is derived from A72's.That being said, with Phytium and Hisilicon cut off from TSMC, mainland core development may not result in compelling silicon any time soon.

eastcoast_pete - Tuesday, May 25, 2021 - link

Fair point on "no custom cores". However, I don't expect any custom cores from Ampere coming to a smartphone near me anytime soon, and QC seems to want Nuvia's IP mostly for larger systems. Neither strikes me as a source for efficiency cores in the mobile space. QC may incorporate Nuvia's tech into big cores for its SoCs , but I doubt they'd even do that.eastcoast_pete - Tuesday, May 25, 2021 - link

Addendum: ".. anytime soon" to the end of the last sentence. They probably will try big cores for their SoCs, but I'm afraid they'll pair those with A510 LITTLE cores.mode_13h - Wednesday, May 26, 2021 - link

> I'm afraid they'll pair those with A510 LITTLE cores.As opposed to what? We saw nothing to suggest the A510 is *worse* than A55. And if you're doing ARMv9, then there are no other options (except proprietary).

Also, why are you freaking out over A510? It's a little underwhelming, but it's not *bad*.

mode_13h - Wednesday, May 26, 2021 - link

> QC seems to want Nuvia's IP mostly for larger systemsNo. Nuvia said they were building server cores, but Qualcomm's messaging around the acquisition was that Nuvia will build cores showing up in mobile SoCs, first.

They didn't rule out the possibility of larger systems, but that's clearly not their priority.

roboman21 - Tuesday, May 25, 2021 - link

Apple is lightyears ahead and it is due in no small part to this acquisition:https://www.anandtech.com/show/3665/apples-intrins...

This is tough to pull of but it can yield advantages to a competitor with the same ARM core and 7nM semiconductor process.