Arm Announces Mobile Armv9 CPU Microarchitectures: Cortex-X2, Cortex-A710 & Cortex-A510

by Andrei Frumusanu on May 25, 2021 9:00 AM EST- Posted in

- SoCs

- CPUs

- Arm

- Smartphones

- Mobile

- Cortex

- ARMv9

- Cortex-X2

- Cortex-A710

- Cortex-A510

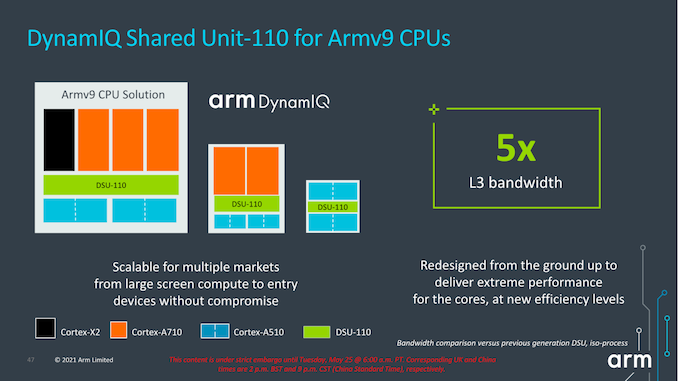

New DSU-110 L3 & Cluster: Massively More Bandwidth

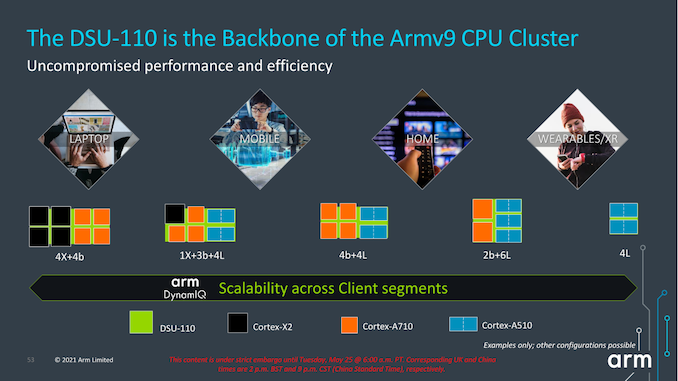

Alongside the new CPU microarchitectures, Arm today is also announcing a new L3 design in the form of the new DSU-110. The “DynamIQ Shared Unit” had been the company’s go-to cluster and “core complex” block ever since it was introduced in 2017 with the Cortex-A75 and Cortex-A55. While we’ve seen small iterative improvements, today’s DSU-110 marks a major change in how the DSU operates and how it promises to scale up in cache size and bandwidth.

The new DSU-110 is a ground-up redesign with an emphasis on more bandwidth and more power efficiency. It continues to be the core building block for all of Arm’s mobile and lower tier market segments.

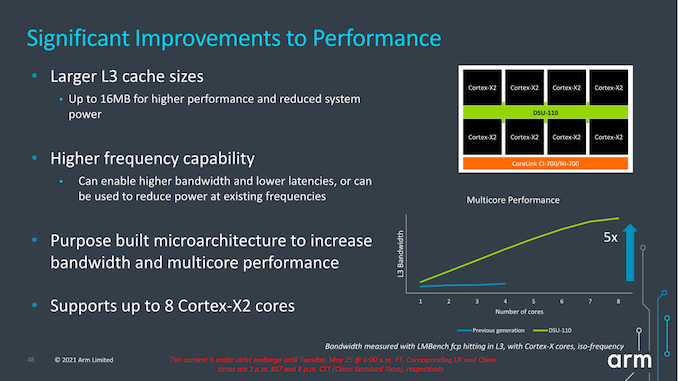

A key metric is of course the increase of L3 cache configuration which will now go up to 16MB this generation. This is of course the high-end of the spectrum and generally we shouldn’t expect such a configuration in a mobile SoC soon, but Arm has had several slides depicting larger form-factor implementations using such a larger design housing up to 8 Cortex-X2 cores. This is undoubtedly extremely interesting for a higher-performance laptop use-case.

The bandwidth increase of the new design is also significant, and applies from single-thread to multi-threaded scenarios. The new DSU-110 promises aggregate bandwidth increases of up to 5x compared to the contemporary design. More interesting is the fact that it also significantly boosts single-core bandwidth, and Arm here actually notes that the new DSU can actually support more bandwidth than what’s actually capable of the new core microarchitectures for the time being.

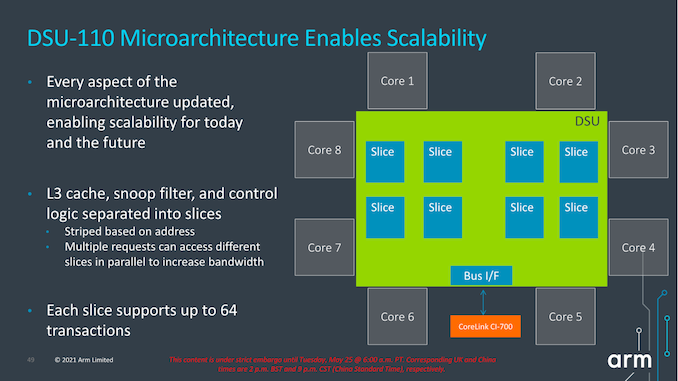

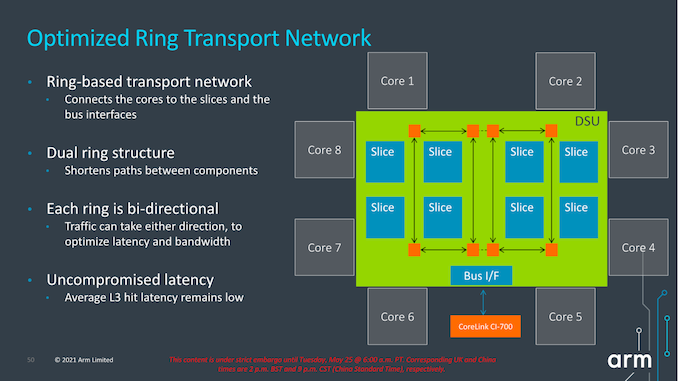

Arm never really disclosed the internal topology of the previous generation DSU, but remarks that with the DSU-110 the company has shifted over to a bi-directional dual-ring transport topology, each with four ring-stops, and now supporting up to 8 cache slices. The dual-ring structure is used to reduce the latencies and hops between ring-stops and in shorten the paths between the cache slices and cores. Arm notes that they’ve tried to retain the same lower access latencies as on the current generation DSU (cache size increases aside), so we should be seeing very similar average latencies between the two generations.

Parallel access increases for bandwidth as well as more outstanding transactions seem to have been also very important in order to improve performance, which seems very exciting for upcoming SoC designs, but also puts into more question the previously presented CPU IPC improvements and exactly how much the new DSU-110 contributes to those numbers.

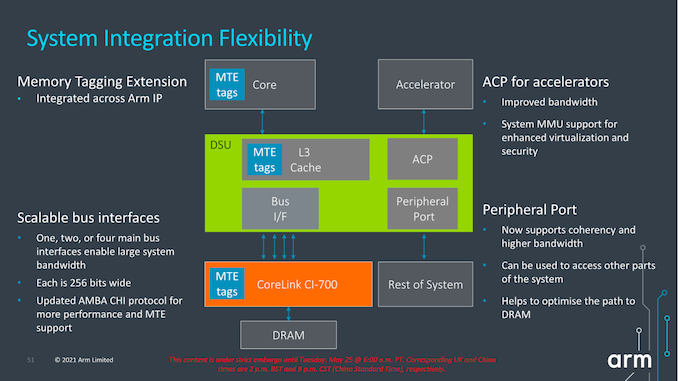

Architecturally, one important change to the capabilities of the DSU-110 is support for MTE tags, a upcoming security and debugging feature promising to greatly help with memory safety issues.

The new DSU can scale up to 4x AMBA CHI ports, meaning we’ll have up to 1024-bit total bi-directional bandwidth to the system memory. With a theoretical DSU clock of around 2GHz this would enable bandwidth of up to 256GB/s reads or writes, or double that when combined, plenty enough to be able to saturate also eventual high-end laptop configurations.

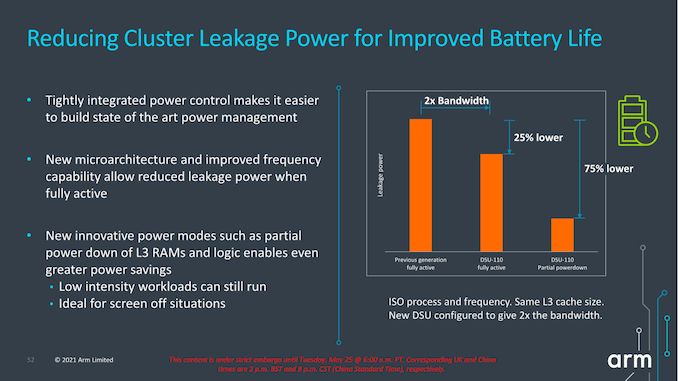

In terms of power efficiency, the new DSU offers more options for low-power operation when in idle situations, implementing partial L3 power-down, able to reduce leakage power of up to 75% compared to the current DSU.

In general idle situations but still having the full L3 powered on, the new design promises up to 25% reduction in leakage power all whilst offering 2x the bandwidth capabilities.

It’s important to note that we’re talking about leakage power here- active dynamic power is expected to generally scale linearly with the bandwidth increase of the new design, meaning 5x the bandwidth would also cost 5x the power. This would be an important factor to note into system power and in general the expected power behaviour of the next-gen SoCs when they’re put under heavy memory workloads.

Arm describes the DSU-110 as the backbone of the Armv9 cluster and that seemingly seems to be an apt description. The new bandwidth capabilities are sure to help out both with single-threaded, but also with multi-threaded performance of upcoming SoCs. Generally, the new 16MB L3 capability, while it’s possible somebody might do a high-end laptop SoC configuration, isn’t as exciting as the now finally expected move to a new 8MB L3 on mobile SoCs, hopefully also enabling higher power efficiency and more battery life for devices.

181 Comments

View All Comments

ikjadoon - Tuesday, May 25, 2021 - link

Fair; I'll take a K12 successor as recompense.The business side is good context I forgot, but now in 2021, AMD is in much better straits and surely K12's successor is worth a shot.

https://www.anandtech.com/show/7990/amd-announces-...

Surely there were great ideas in Keller's work, their team's work, in their post-Styx designs

AMD might find a lot of benefit in preparing an Arm roadmap. What's to stop consoles, laptops, desktops from switching to Arm, from AMD"s financial perspective? Hopefully, they have clear eyes on x86's relevance to both consumers & businesses. AMD has a knack for fighting back, so I hope the build on their financial momentum.

TheinsanegamerN - Wednesday, May 26, 2021 - link

Compatibility, performance, and existence.ARM brings compatibility issues with previously existing software. Emulation wont work 100%,a nd compatibility with existing hardware is a minefield

With that emulation/compatibility layer comes performance degregations. Sometimes it may not be so bad, other times it will be horrendous. The overall software market is not as tightly controlled as apple's walled garden approach.

And finally, existence. There is currently no high performance ARM processor in existence. Show me a desktop ARM process ro that could replace a 5900x or a 10900k. How about one that could replace the CPU in the PS5? Currently one does not exist. You could say one exists for laptops, but that is only available for apple.

mode_13h - Thursday, May 27, 2021 - link

> There is currently no high performance ARM processor in existence.There are probably a dozen ARM server processors on the market or still in service that would fit a reasonable definition of high-performance.

> Show me a desktop ARM processor that could replace a 5900x or a 10900k.

I see you stuck that word "desktop" in there. Desktop is probably the last market ARM would penetrate. So, if your point is that you won't take ARM seriously until there's a competitive ARM-based desktop offering, that's like reaching for the fire extinguisher once you're surrounded by flames instead of when you first smell smoke.

I'm eager to see what V1-based CPUs look like. Those cores could make for a viable workstation CPU.

mode_13h - Tuesday, May 25, 2021 - link

And don't forget about Chinese designs (although this one is mentioned as being A72-derived):https://en.wikichip.org/wiki/hisilicon/microarchit...

SarahKerrigan - Tuesday, May 25, 2021 - link

The KP920 core isn't A72 derived. It says "from A72" but all it's saying there is that its predecessor used A72's - it's not saying the core is derived from A72's.That being said, with Phytium and Hisilicon cut off from TSMC, mainland core development may not result in compelling silicon any time soon.

eastcoast_pete - Tuesday, May 25, 2021 - link

Fair point on "no custom cores". However, I don't expect any custom cores from Ampere coming to a smartphone near me anytime soon, and QC seems to want Nuvia's IP mostly for larger systems. Neither strikes me as a source for efficiency cores in the mobile space. QC may incorporate Nuvia's tech into big cores for its SoCs , but I doubt they'd even do that.eastcoast_pete - Tuesday, May 25, 2021 - link

Addendum: ".. anytime soon" to the end of the last sentence. They probably will try big cores for their SoCs, but I'm afraid they'll pair those with A510 LITTLE cores.mode_13h - Wednesday, May 26, 2021 - link

> I'm afraid they'll pair those with A510 LITTLE cores.As opposed to what? We saw nothing to suggest the A510 is *worse* than A55. And if you're doing ARMv9, then there are no other options (except proprietary).

Also, why are you freaking out over A510? It's a little underwhelming, but it's not *bad*.

mode_13h - Wednesday, May 26, 2021 - link

> QC seems to want Nuvia's IP mostly for larger systemsNo. Nuvia said they were building server cores, but Qualcomm's messaging around the acquisition was that Nuvia will build cores showing up in mobile SoCs, first.

They didn't rule out the possibility of larger systems, but that's clearly not their priority.

roboman21 - Tuesday, May 25, 2021 - link

Apple is lightyears ahead and it is due in no small part to this acquisition:https://www.anandtech.com/show/3665/apples-intrins...

This is tough to pull of but it can yield advantages to a competitor with the same ARM core and 7nM semiconductor process.