Arm Announces Mobile Armv9 CPU Microarchitectures: Cortex-X2, Cortex-A710 & Cortex-A510

by Andrei Frumusanu on May 25, 2021 9:00 AM EST- Posted in

- SoCs

- CPUs

- Arm

- Smartphones

- Mobile

- Cortex

- ARMv9

- Cortex-X2

- Cortex-A710

- Cortex-A510

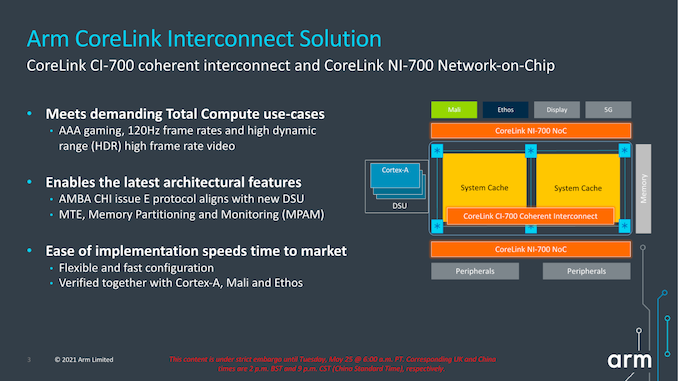

A new CI-700 Coherent Interconnect & NI-700 NoC For SoCs

Finally, the last new announcement of the day is a new interconnect and network-on-chip generation. The last time Arm had announced a mobile/client interconnect was back in in 2015 with the CCI-550. The reason for the large gap between IPs, in Arm’s own words, is that ever since Arm’s introduction of the DSU in its CPU complexes, there really hasn’t been any need for a cache coherent interconnect in the market. While that’s eyebrow-raising from a GPU perspective, it makes perfect sense from a CPU perspective, as coherency between CPU cores was the primary driver for such interconnects until then.

With the advent of new more complex computing platforms, such as NPUs, accelerators, and hopeful more use of GPUs in cache-coherent fashions, Arm saw a need gap in its portfolio and decided to update its client-side interconnect IP.

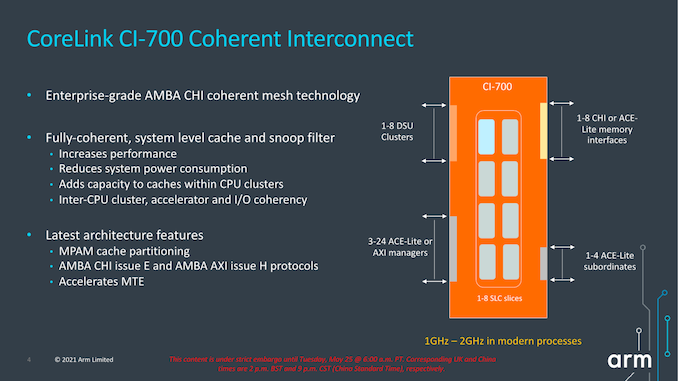

The new CI-700 is a mobile and client optimised variant of Arm’s infrastructure CMN mesh network, implementing important new interoperability with the new IP announced today, such as the new DSU or CPU cores.

The new mesh interconnect scales up from 1 to 8 DSU clusters, and supports up to 8 memory controllers, and also introduces innovations such as a system level cache.

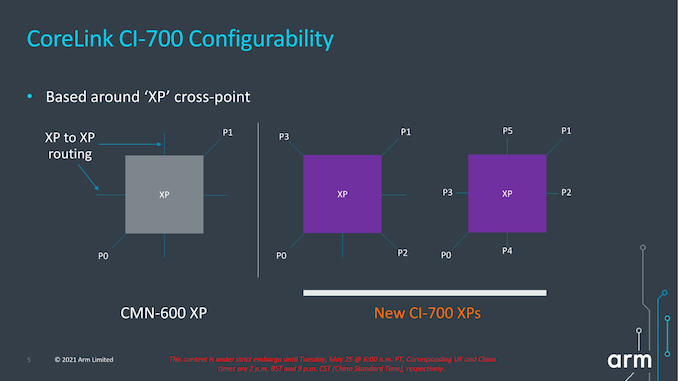

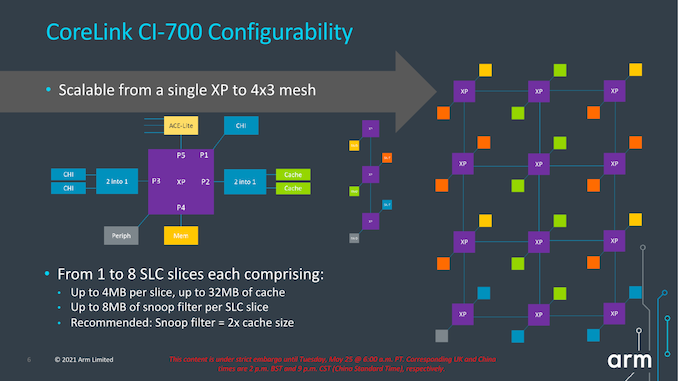

The mesh network topology and building blocks is very similar to what we’ve seen in the CMN infrastructure IP, in that “points” in the mesh are comprised of “cross-points” or “XP”. One differentiation that’s unique to the client mesh implementation is that XPs can have more attached connectivity ports, trading in routing connection paths. The new IP can also be configured as just a sole XP with no real mesh so to speak of, or essentially a 1x1 mesh configuration. This can grow up to a 4x3 mesh in the largest possible configuration.

The mesh supports from 1 to 8 SLC slices, with up to 4MB per slice for a total of 32MB, and snoop filter SRAM with coverage of up to 8MB address space per slice. It’s noted that generally Arm recommends 1.5-2x of coverage of the underlying private cache hierarchies of the mesh clients.

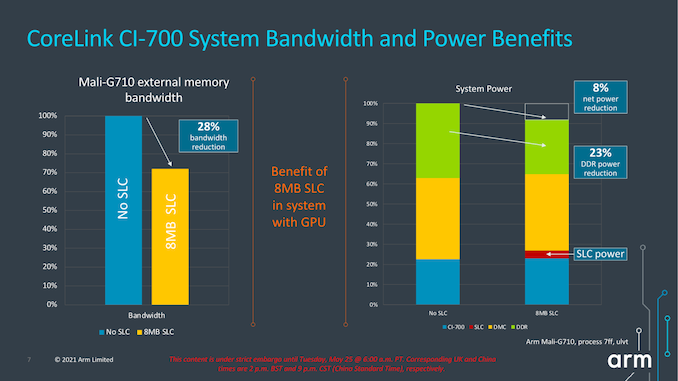

The SLC can server as both a bandwidth amplifier as well as reducing external memory/DRAM transactions, reducing system power reduction.

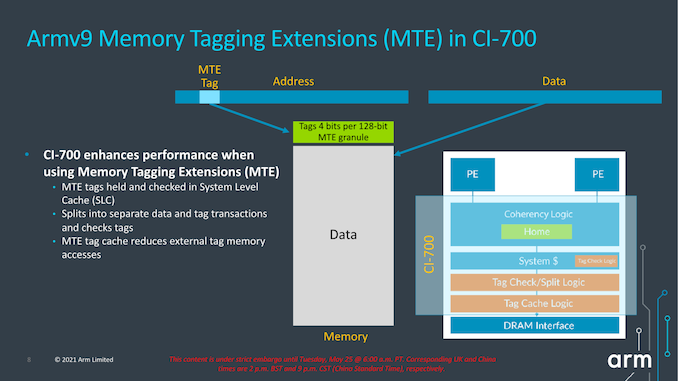

We see a reiteration of the support for MTE, allowing for this generation of IPs to support the feature across the new CPU IP, the DSU, and the new cache coherent interconnect.

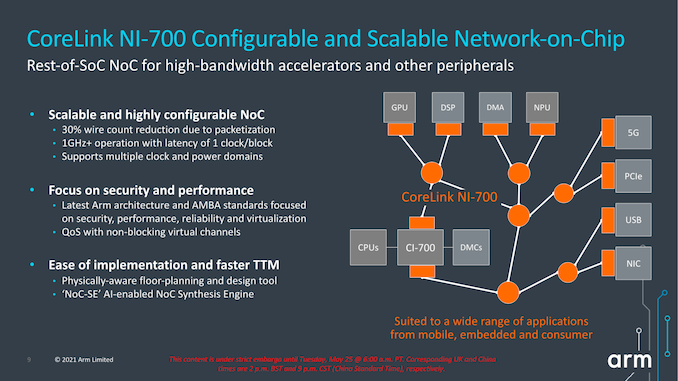

Alongside the new CI-700 coherent interconnect, we’re also seeing a new NI-700 network-on-chip for non-coherent data transfers between a SoC’s various IP blocks. The big new improvements here is the introduction of packetization for data transfers, which leads to a reduction of wires and thus improves area efficiency of the NoC on the SoC.

Overall, the new system IP announced today is very interesting, but the one question that’s one has to ask oneself is exactly who these net interconnects are meant for. Over the last few years, we’ve seen essentially every major mobile vendor roll out their own in-house cache-coherent interconnect IP, such as Samsung’s SCI or MediaTek’s MCSI, and other times we don’t see vendors talk about their in-house interconnects at all (Qualcomm). Due to almost everybody having their own IP, I’m not sure what the likelihood would be that any of the big players would jump back to Arm’s own solutions – if somebody were to adopt it, it would rather be amongst the smaller name vendors and newcomers to the market. From a business and IP portfolio perspective, the new designs make a lot of sense and allows to have the building blocks to create a mostly Arm-only SoC, which is an important item to have on the menu for Arm’s more diverse customer base.

181 Comments

View All Comments

dotjaz - Wednesday, May 26, 2021 - link

Where do you even get expensive 32bit phones? There is no REAL shift other than Play Store policy which doesn't even affect end users.mode_13h - Wednesday, May 26, 2021 - link

Look up you phone specs on a site like gsmarena and see what cores it has. If any are ARM Cortex-A35, A5x, or A7x, then you already have a 64-bit phone.Most phones sold for the past 5 years have been 64-bit.

RSAUser - Wednesday, May 26, 2021 - link

Anything launched with lollipop or higher is most probably 64bit, so shouldn't be an issue.SarahKerrigan - Tuesday, May 25, 2021 - link

A55, But Wider And More Dozery was not what I expected.Still, it looks quite decent. Excited to see A710 and A510 in silicon. Not sure how to feel about X2.

The fun begins immediately! Or in about seven months, as the case may be!

eastcoast_pete - Tuesday, May 25, 2021 - link

I had a somewhat different reaction: the X2 makes some sense, it's a continuation of the X1 performance over efficiency approach, the 710 is the next big "A" core, and the 510 is, as Andrei wrote, a bit underwhelming. To me, it looks like ARM didn't even consider using their A65 design (OOO) and come up with a true contender for the perf/W crown for efficiency cores. Apple remains light years ahead here, and anyone in the non-iOS space is stuck with this attempt to inject some Bulldozer design features into the tired in-order A55 lineage. With no custom ARM-derived cores on the horizon (doubt if Google will surprise us with their custom SoC), what's next? RISC-V?SarahKerrigan - Tuesday, May 25, 2021 - link

No custom cores on the horizon? What about Nuvia and Ampere's cores?mode_13h - Tuesday, May 25, 2021 - link

There remains the outside possibility that AMD or Intel decides to enter the ARM race.ikjadoon - Tuesday, May 25, 2021 - link

I will not yet forgive AMD for binning Jim Keller's K12 design. Qualcomm, Arm, Apple all needed more competition in the perf-watt battle.mode_13h - Tuesday, May 25, 2021 - link

> I will not yet forgive AMD for binning Jim Keller's K12 design.It costs money to bring a chip to market, and AMD was deep in debt. Lisa Su barely managed to keep the lights on, with that Chinese licensing deal. And the market for ARM servers just wasn't ripe.

Assuming they really couldn't afford to do both (at least, without significant compromises), they definitely made the right call by going with x86.

mode_13h - Tuesday, May 25, 2021 - link

BTW, I agree that I'd love to see how well it compared to other ARM cores of its day, but we can't ignore the practical and business realities.I hope AMD will one day reveal more about the K12. That definitely won't happen as long as a potential successor is in the works!