Arm Announces Mobile Armv9 CPU Microarchitectures: Cortex-X2, Cortex-A710 & Cortex-A510

by Andrei Frumusanu on May 25, 2021 9:00 AM EST- Posted in

- SoCs

- CPUs

- Arm

- Smartphones

- Mobile

- Cortex

- ARMv9

- Cortex-X2

- Cortex-A710

- Cortex-A510

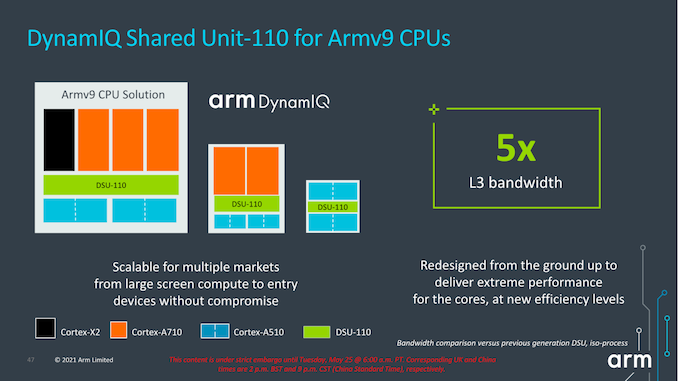

New DSU-110 L3 & Cluster: Massively More Bandwidth

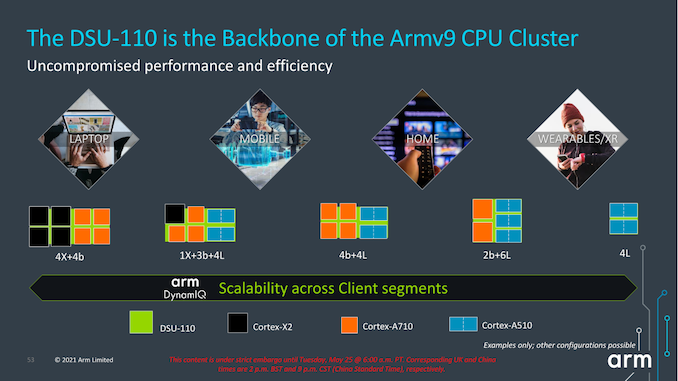

Alongside the new CPU microarchitectures, Arm today is also announcing a new L3 design in the form of the new DSU-110. The “DynamIQ Shared Unit” had been the company’s go-to cluster and “core complex” block ever since it was introduced in 2017 with the Cortex-A75 and Cortex-A55. While we’ve seen small iterative improvements, today’s DSU-110 marks a major change in how the DSU operates and how it promises to scale up in cache size and bandwidth.

The new DSU-110 is a ground-up redesign with an emphasis on more bandwidth and more power efficiency. It continues to be the core building block for all of Arm’s mobile and lower tier market segments.

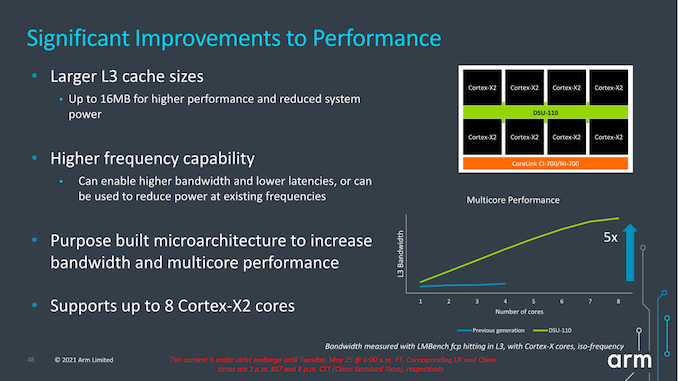

A key metric is of course the increase of L3 cache configuration which will now go up to 16MB this generation. This is of course the high-end of the spectrum and generally we shouldn’t expect such a configuration in a mobile SoC soon, but Arm has had several slides depicting larger form-factor implementations using such a larger design housing up to 8 Cortex-X2 cores. This is undoubtedly extremely interesting for a higher-performance laptop use-case.

The bandwidth increase of the new design is also significant, and applies from single-thread to multi-threaded scenarios. The new DSU-110 promises aggregate bandwidth increases of up to 5x compared to the contemporary design. More interesting is the fact that it also significantly boosts single-core bandwidth, and Arm here actually notes that the new DSU can actually support more bandwidth than what’s actually capable of the new core microarchitectures for the time being.

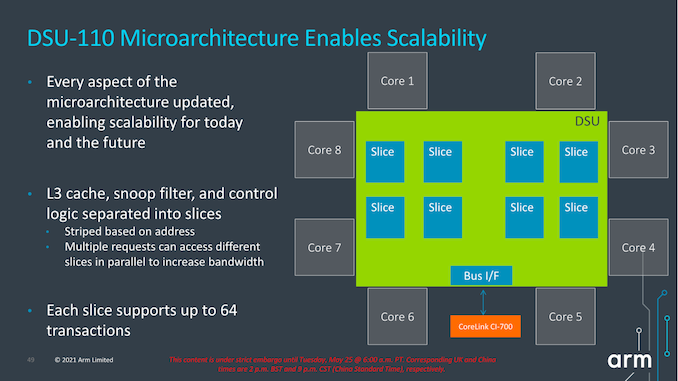

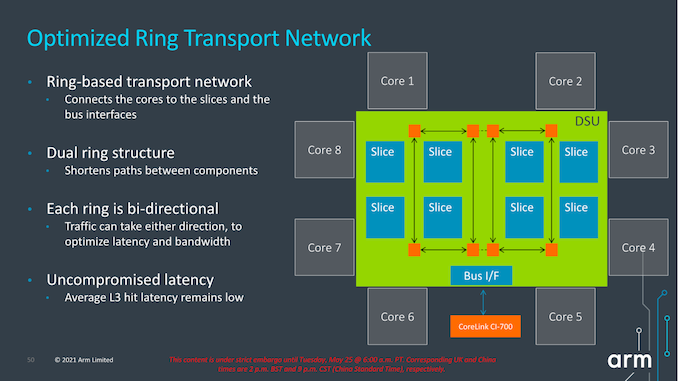

Arm never really disclosed the internal topology of the previous generation DSU, but remarks that with the DSU-110 the company has shifted over to a bi-directional dual-ring transport topology, each with four ring-stops, and now supporting up to 8 cache slices. The dual-ring structure is used to reduce the latencies and hops between ring-stops and in shorten the paths between the cache slices and cores. Arm notes that they’ve tried to retain the same lower access latencies as on the current generation DSU (cache size increases aside), so we should be seeing very similar average latencies between the two generations.

Parallel access increases for bandwidth as well as more outstanding transactions seem to have been also very important in order to improve performance, which seems very exciting for upcoming SoC designs, but also puts into more question the previously presented CPU IPC improvements and exactly how much the new DSU-110 contributes to those numbers.

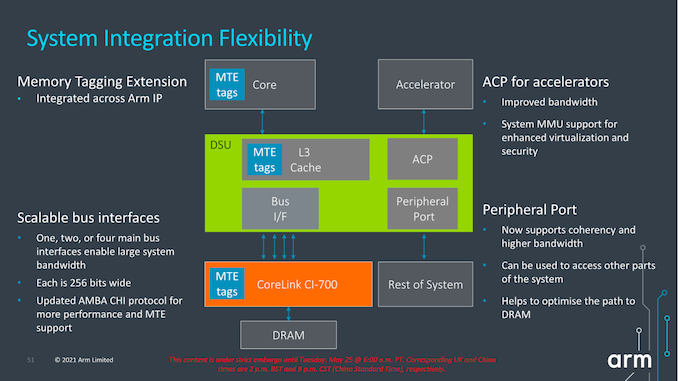

Architecturally, one important change to the capabilities of the DSU-110 is support for MTE tags, a upcoming security and debugging feature promising to greatly help with memory safety issues.

The new DSU can scale up to 4x AMBA CHI ports, meaning we’ll have up to 1024-bit total bi-directional bandwidth to the system memory. With a theoretical DSU clock of around 2GHz this would enable bandwidth of up to 256GB/s reads or writes, or double that when combined, plenty enough to be able to saturate also eventual high-end laptop configurations.

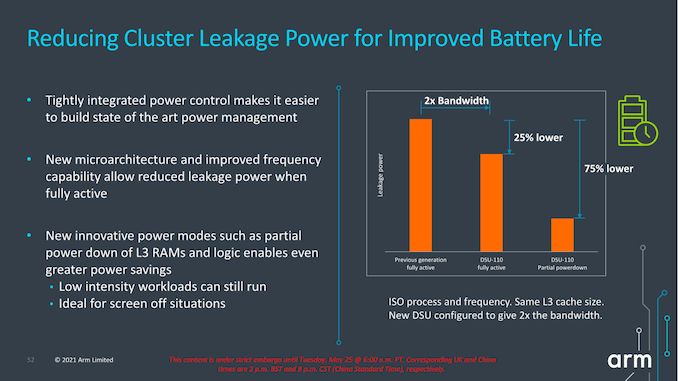

In terms of power efficiency, the new DSU offers more options for low-power operation when in idle situations, implementing partial L3 power-down, able to reduce leakage power of up to 75% compared to the current DSU.

In general idle situations but still having the full L3 powered on, the new design promises up to 25% reduction in leakage power all whilst offering 2x the bandwidth capabilities.

It’s important to note that we’re talking about leakage power here- active dynamic power is expected to generally scale linearly with the bandwidth increase of the new design, meaning 5x the bandwidth would also cost 5x the power. This would be an important factor to note into system power and in general the expected power behaviour of the next-gen SoCs when they’re put under heavy memory workloads.

Arm describes the DSU-110 as the backbone of the Armv9 cluster and that seemingly seems to be an apt description. The new bandwidth capabilities are sure to help out both with single-threaded, but also with multi-threaded performance of upcoming SoCs. Generally, the new 16MB L3 capability, while it’s possible somebody might do a high-end laptop SoC configuration, isn’t as exciting as the now finally expected move to a new 8MB L3 on mobile SoCs, hopefully also enabling higher power efficiency and more battery life for devices.

181 Comments

View All Comments

ChrisGX - Thursday, May 27, 2021 - link

Yes, @melgross, @mattbe and @mode_13h are absolutely right. Apple has an architectural license from ARM, viz. a license for the ARM ISA rather than any physical IP. Not deterred by that some individuals commenting here seem to want to suggest that Apple has infringed on ARM's IP or somehow by nefarious means has acquired crucial information about proprietary tech found in ARM chips without stumping up the cash for it. These suggestions are pathetic. If a patent infringement is being alleged please tell us the patent number so that we can determine for ourselves whether there really has been a patent infringement. Or, is a criminal conspiracy with other parties to steal trade secrets from ARM being asserted? There is an obvious problem with that idea. Does anyone seriously suppose that ARM would fail to have Apple before a court demanding a huge settlement for theft of trade secrets, if it had any reason to think that Apple had been engaged in such an exercise? Uninformed individuals are just making up things that chime with their sense of how things must be. Hmm...here's a thought. If you know so little about a topic that you wouldn't be willing to stake your reputation on it or swear to in a court, say, then perhaps saying nothing on the topic would be a better choice than pretending to possess knowledge that you so obviously don't possess.mode_13h - Saturday, May 29, 2021 - link

> Uninformed individuals are just making up things that chime with> their sense of how things must be.

Welcome to the world of internet comment forums.

> If you know so little about a topic that you wouldn't be willing to stake your reputation on it

We don't do "reputation". Everybody is on equal footing, here. Just challenge them with facts, references, and sound logic.

jeremyshaw - Tuesday, May 25, 2021 - link

Thanks SarahKerrigan, igor velky. I was mostly thinking of configurations we didn't commonly see. We have seen 4xLITTLE, 2xbig.4xLITTLE, etc even the 8xA78C. The slides on page 5 cover setups we have seen before. Mostly curious if the fabric is tied to specific configs like was implied at the 8xA78C launch, or if it's flexible enough to have, say, two X2, two A710, four A510, or something like one X2 with four A510 (like Intel's Lakefield), etc. IMO, there are a lot of embedded controllers that don't need a lot of CPU throughput, but can benefit from one faster core for UI.Kangal - Saturday, May 29, 2021 - link

I'm more interested in seeing a 3+5 design.The "Large Cores" just aren't good on a phone, a tablet maybe, not on a phone. We're already getting throttling on the "Medium Cores" (eg Cortex A78/A710). And most tasks on Android are handled great in Dualcore mode, and very few in Quad-core mode, when looking at the schedulers. So Three Medium Cores will offer 95% of the performance of your regular flagship processor. Extending the Small Cores to a group of five, also can help efficiency by having more performance in the lower zone, reducing the amount of times the large cores need to be stressed.

However, with what was announced today, we can actually expect a REDUCTION in 2022 ARM processors compared to 2021 ARM processors. I mean we're talking about 10% gains in X2, 10% gains in A710, and 1% gains in A510, when compared to a design that should be on a better node with better cache. That's not guaranteed with the continuing Chip Shortage. IN FACT most chipmakers are willing to "cheap out" and simply use the marketing of "running on ARMv9" to justify the higher cost and lower performance.

They stuffed up with the naming scheme btw. And they really stuffed up by not removing 32-bit support completely. And they stuffed up with not doing a blank-sheet approach, for a revolutionary ARMv9 design. We're going to see the smallest gains in Android Phones, just like it happened when people were comparing the QSD 800/801/805 to the QSD 808/810 (Cortex A57) back in 2015. Which hopefully means ARMs other divisions in UK/France can pick the slack and come with a proper successor. This would be the Cortex A72 to their Cortex A57, a la, 2022 A710 versus the 2023 A730. Though I doubt the little cores will get any improvement besides a 10% bump due to the node lithography improvements.

psychobriggsy - Monday, June 21, 2021 - link

Theoretically this should support 16 A510s (8 clusters), as each cluster shares a port on the interconnect.We may see 2X 4B 4L configurations (10 cores) one day, but in the main I guess we're stuck with 1X 3B 4L (8L?) options. I see budget chips using 4L+4L (wider FP on some).

Wonder if there's room for an A310 chip (4 int cores per cluster, 1 shared FP, 2-wide).

docola - Tuesday, May 25, 2021 - link

does the shift to 64 bit cpus and apps mean that todays phone will startbecoming obsolete starting next year?

iphonebestgamephone - Tuesday, May 25, 2021 - link

If you are on a 32 bit phone yeahdocola - Tuesday, May 25, 2021 - link

fun... so this means i shouldnt buy an expensive phone for another 1 or 2 years,because this is gonna be one of those rare REAL shift in tech... sigh....

supdawgwtfd - Tuesday, May 25, 2021 - link

Current phones support 64bit instructions...No need to delay.

docola - Tuesday, May 25, 2021 - link

great thanks! i know i sound ignorant in here oh well