Arm Announces Mobile Armv9 CPU Microarchitectures: Cortex-X2, Cortex-A710 & Cortex-A510

by Andrei Frumusanu on May 25, 2021 9:00 AM EST- Posted in

- SoCs

- CPUs

- Arm

- Smartphones

- Mobile

- Cortex

- ARMv9

- Cortex-X2

- Cortex-A710

- Cortex-A510

The Cortex-A710: More Performance with More Efficiency

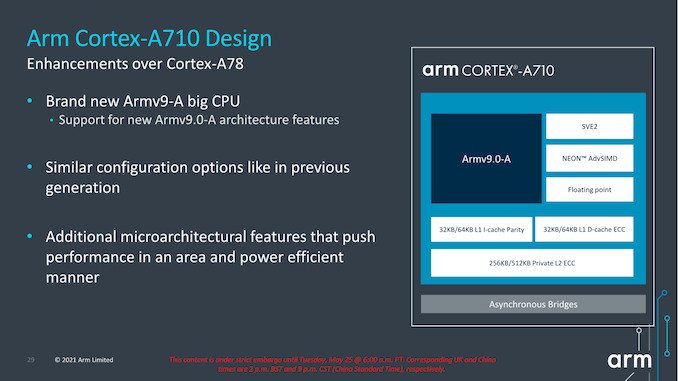

While the Cortex-X2 goes for all-out performance while paying the power and area penalties, Arm's Cortex-A710 design goes for a more efficient approach.

First of all, the new product nomenclature now is self-evident in regards to what Arm will be doing going forward- they’re skipping the A79 designation and simply starting fresh with a new three-digit scheme with the A710. Not very important in the grand scheme of things but an interesting marketing tidbit.

The Cortex-A710, much like the X2, is an Armv9 core with all new features that come with the new architecture version. Unlike the X2, the A710 also supports EL0 AArch32 execution, and as mentioned in the intro, this was mostly a design choice demanded by customers in the Chinese market where the ecosystem is still slightly lagging behind in moving all applications over to AArch64.

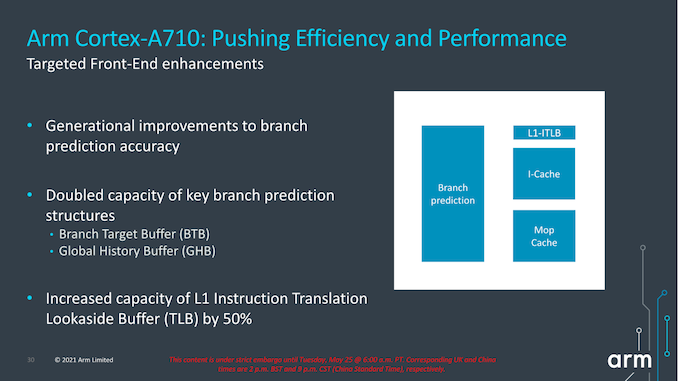

In terms of front-end enhancements, we’re seeing the same branch prediction improvements as on the X2, with larger structures as well as better accuracy. Other structures such as the L1I TLB have also seen an increase from 32 entries to 48 entries. Other front-end structures such as the macro-OP cache remain the same at 1.5K entries (The X2 also remains at 3K entries).

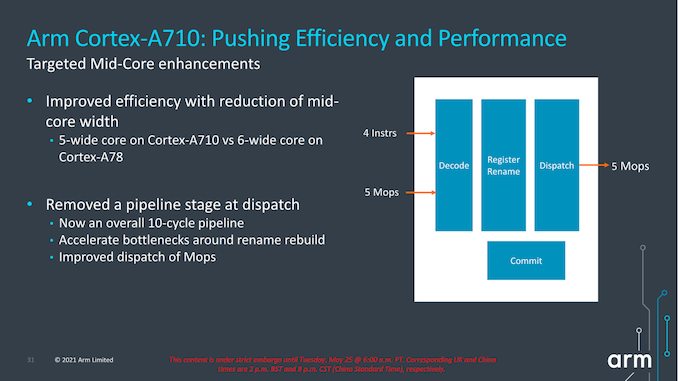

A very interesting choice for the A710 mid-core is that Arm has reduced the macro-OP cache and dispatch stage throughputs from 6-wide to 5-wide. This was mainly a targeted power and efficiency optimization for this generation, as we’re seeing a more important divergence between the Cortex-A and Cortex-X cores in terms of their specializations and targeted use-cases for performance and power.

The dispatch stage also features the same optimizations as on the X2, removing 1 cycle from the pipeline towards an overall 10-cycle pipeline design.

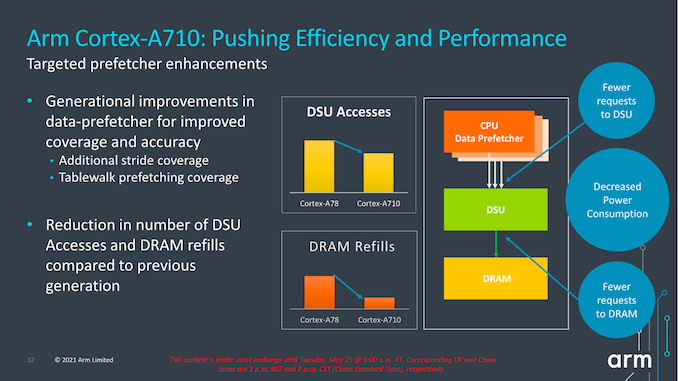

Arm also focuses on core improvements that affect the uncore parts of the system, which take place thanks to the new improvements in the prefetcher designs and how they interact with the new DSU-110 (which we’ll cover later). The new combination of core and DSU are able to reduce access from the core towards the L3 cache, as well as reducing the costly DRAM accesses thanks to the more efficiency prefetchers and larger L3 cache.

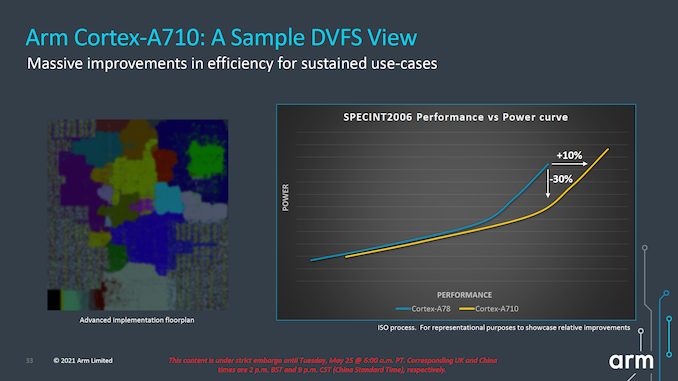

In terms of IPC, Arm advertises +10%, but again the issue with this figure here is that we’re comparing an 8MB L3 cache design to a 4MB L3 cache design. While this is a likely comparison for flagship SoCs next year, because the Cortex-A710 is also a core that would be used in mid-range or lower-end SoCs which might use much smaller L3 caches, it’s unlikely we’ll be seeing such IPC improvements in that sector unless the actual SoCs really do also improve their DSU sizes.

More important than the +10% improvement in performance is that, when backing off slightly in frequency, we can see that the power reduction can be rather large. According to Arm, at iso-performance the A710 consumes up to 30% less power than the Cortex-A78. This is something that would greatly help with sustained performance and power efficiency of more modestly clocked “middle” core implementations of the Cortex-A710.

In general, both the X2 and the A710’s performance and power figures are quite modest, making them the smallest generation-over-generation figures we’ve seen from Arm in quite a few years. Arm explains that due to this generation having made larger architectural changes with the move to Armv9, there has been an impact in regards to the usual efficiency and performance improvements that we’ve seen in prior generations.

Both the X2 and the A710 are also the fourth generation of this Austin microarchitecture family, so we’re hitting a wall of diminishing returns and maturity of the design. A few years ago we were under impression that the Austin family would only go on for three generations before handing things over to a new clean-sheet design from the Sophia team, but that original roadmap has been changed, and now we'll be seeing the new Sophia core with larger leaps in performance being disclosed next year.

181 Comments

View All Comments

Fulljack - Wednesday, May 26, 2021 - link

that's why it's called DynamIQ, you know... as in "dynamic".phoenix_rizzen - Tuesday, May 25, 2021 - link

Interesting. Wonder if Samsung and/or Qualcomm will be using the A510 as the basis for a smartwatch SoC. A pair of these should provide a huge performance increase over the A7-based SoCs, but use much less power than anything using a "big" core (wasn't there a Samsung watch SoC that used a big core?).EthiaW - Tuesday, May 25, 2021 - link

An ideal mobile SoC configuration should be 2xX2+4xA710+2xA510. There is only so much background work to do and as many as four little cores do not make sense.Fulljack - Wednesday, May 26, 2021 - link

I'm thinking of 1×X2 + 3×A710 + 2×A510, and gives more room for GPU.docola - Tuesday, May 25, 2021 - link

question: does this mean if i buy a mobile phone today,that starting within a year from now it will eventually be useless because all

apps will be moving to 64 bit, which my phone wont support?

Or will my phone have access to plenty of the man 32 bit apps for 3-4 years to come?

(if thats the cas then i think i'll buy a stupidly cheap phone till next year)

thanks~

phoenix_rizzen - Tuesday, May 25, 2021 - link

Android phones have supported 64-bit OSes and apps since the Snapdragon 810, many many years ago.Android stopped accepting new 32-bit apps into the Play Store in 2019.

Android has essentially been 64-bit only for over 2 years now.

mode_13h - Wednesday, May 26, 2021 - link

> Android phones have supported 64-bit OSes and apps since the Snapdragon 810,> many many years ago.

You mean 8xx. I got a Nexus 5X in like 2015 that had a Snapdragon 808 with 2x A57 and 4x A53.

docola - Tuesday, May 25, 2021 - link

does the shift to 64 bit apps mean that todays phonewill start being unable to run apps next year?

Wilco1 - Tuesday, May 25, 2021 - link

No. Pretty much all phones are 64-bit today and thus support 64-bit apps already.Silver5urfer - Tuesday, May 25, 2021 - link

What's the use when all of these end up in planned obsolescence devices which have a max life of 2-3 years. They should make this "Days charging" whatever into reality by making the phones with removable batteries.As for laptops, same thing but different skin. Most of the BGA laptops will die fast because of their Heatsink and non replaceable components and high heat due to thin and light designs (mostly for x86) and then the Batteries for all those machines after market there's no way anyone can make use of their HW for more years, esp if the HW is all soldered. For eg an MXM laptop can take many generations of the GPUs it used to be the case for most machines until now since nowadays Turing based GPUs Quadro cards are also non standard.

So all in all get excited for same performance benefits that user will see, my SD835 phone is quick and fast and reliable yeah SD888 would be definitely faster but how much it would impact in the normal tasks of Maps / Browser / Videos / Music ? Games maybe but I don't play on smartphones. I presume it is same for all those SD855, 865 phones. Even the iPhones from A11 and up.

Bonus we don't get to control even 1 bit with hardcore locks on phones from OS level Filesystem nerfs from Goolag to the HW side of having no 3.5mm jacks and SD slots. But yea people love to get excited for new shiny stuff.