Updated! IDF Spring 2005 Day 1 - 65nm Multi-Core Demos and more

by Anand Lal Shimpi on March 1, 2005 4:10 PM EST- Posted in

- Trade Shows

Update: We got some more information about presler and other dual core items we mentioned below.

First, we have die sizes and transistor counts for the Pentium D (Smithfield) and the new dual core Pentium Extreme Edition chips:

- 206 mm^2 90nm die

- 230M transistors

Note that the sizes and transistor counts we're talking about here is basically on the level with the announced Cell microprocessor, also built on a 90nm process (but with SOI). Also note that the number 4 has been dropped from the name, the new dual core processors will simply be called the Pentium D and the Pentium Extreme Edition.

While the Pentium D and the dual core Pentium EE are basically two Prescott 1M cores glued together, their 65nm successor (presler) is a bit different. presler appears to have two physically separate cores (two pieces of silicon), each with a 2MB L2 cache (for a total of 4MB of L2 cache). As we mentioned below, presler is also HT enabled for a total of 4 thread simultaneous execution. The reason for making presler two separate pieces of silicon is a matter of yields, since a single dual core silicon would have a larger die surface area than two separate cores.

It is possible to, in both the 90nm and 65nm dual core chips, to cut away or disable (respectively) a non-working core in order to make the chip single-core.

Intel has revealed a bit about future plans, saying that they will be at 8 threads (per chip or per core?) by the end of the decade. The other interesting note is with regards to Intel Xeon platforms, more specifically the upcoming Truland 4S platform.

Truland 4S supports Intel's dual independent bus architecture, meaning that each CPU in a two socket configuration will have its own 1066MHz FSB, as opposed to the shared 667MHz FSB that they have to contend for right now. The other interesting feature is its quad channel DDR2-400 support to match up with the added FSB bandwidth.

More information as we get it, the original article is below as it was originally written.

Unfortunately the NVIDIA keynote on nForce for Intel was pretty much useless as it was basically a rehash of all of the features of nForce4 SLI. NVIDIA did have a working demo and we will try to get a closer view of it at the Technology Showcase later today.

Luckily all is not lost, Intel had some very interesting demos in their Multi-Core Zone. The first thing that attracted our attention was a running demo of the upcoming 65nm presler processor. presler will be the second desktop dual core processor (after Smithfield) to be released sometime in 2006. There's not too much to talk about with presler, but the fact that Intel had a demo up and running on a 65nm process was pretty impressive.

The chip was running on an Intel 955X motherboard, as were all of the dual core desktop platforms in the pavillion.

All of the dual core desktop demos used this motherboard

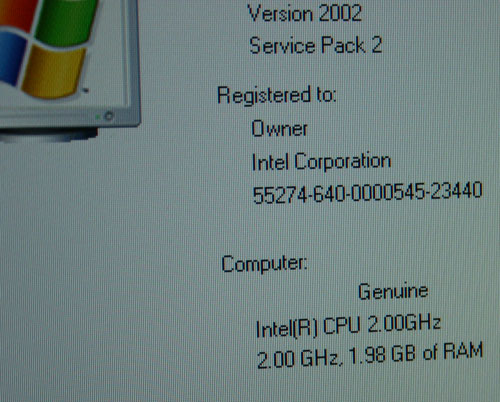

We managed to get a few screenshots before they pulled the keyboard off of the system:

It looks like the chip was running at 2.0GHz, which isn't too impressive in itself, until you remember that we're talking about a 65nm processor here whose launch is over a year away.

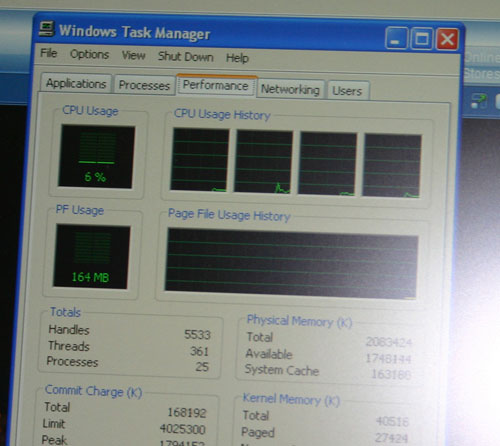

The chip also appears to have Hyper Threading enabled as task manager showed four logical CPUs present:

The first desktop dual core chips will be the Pentium 4 D and the Extreme Edition, both of which will be 90nm chips.

21 Comments

View All Comments

mikecel79 - Tuesday, March 1, 2005 - link

#5 I noticed it to.AtaStrumf - Tuesday, March 1, 2005 - link

Ups, this is a NEW article. Darn it, I sure messed up this time - LOL.coldpower27 - Tuesday, March 1, 2005 - link

Were also quite a bit away from the 65nm process still, so we still don't know what may happen in between that time frame.Doormat - Tuesday, March 1, 2005 - link

Yes, current leakage due to the smaller manufacturing process will increase at 65nm over 90nm, SOI helps, and strained Si increases the amount of current the processor uses (so transistors can be switched quicker, the chip clocked higher). Leakage has been increasing forever, every process shrink caused it to go up, but the problem is that it seems to be governed by an exponential function. It was small for a while, but now its increasing at a drastic rate. When Intel expected 4.5GHz out of a 90nm processor, now they're stuck at 3.8GHz, mostly because of leakage (and the way the P4 is designed didnt help much). The mobile core is better, but it was designed to not consume lots of power. Look at that HSF unit on the 65nm Jonah processor. You arent getting that into a notebook anytime soon (Jonah is a decendant of Banias, so thats why I put that in the frame of reference of a notebook PC).And AMD isnt in much better of a boat, since the new TDP of the newest stepping of the Opteron is 90W (2.6GHz). AMD's dual cores may top out at 2GHz.

AtaStrumf - Tuesday, March 1, 2005 - link

It seems quiet because posts are getting deleted as article gets updated. - LOLWe had a first post and a stupid russian joke when I was last here.

And there was this, let's say, interesting Moore's Law picture, that I was surprised nobody commented on. Let's just say that it looked like the guy had got an erection on the 65nm process - LOL.

Questar - Tuesday, March 1, 2005 - link

#2,65nm is a new manufaturing process. What part of new is it you don't get?

Sure is quiet in here. AMD fanbois gone licking their wounds?

Phiro - Tuesday, March 1, 2005 - link

Hey, is it just me or is the site kinda acting weird? I have to frequently refresh pages to get the body of articles to show up, and with the last two articles the text is invisible until I highlight it.overclockingoodness - Tuesday, March 1, 2005 - link

Dang! AnandTech is really doing live reporting from the show floor. Another update in the next two hours...WOW!SocrPlyr - Tuesday, March 1, 2005 - link

#2first offIntel's 65nm is supposed to include SOI, something the 90nm doesn't include, so that should help. (correct me if i am wrong)

Next there are advantages for smaller processes. First off you can pack more transistors into the same size chip, also those transistors can run faster because of the reduced delay times (mainly from the reduced parasitic capacitances from the transistor size)

Josh

sprockkets - Tuesday, March 1, 2005 - link

since 90nm has more leakage, and 65nm is just going to be worse, what's the big deal or the hype or the happy expectation of a processor that will leak and waste even more power?