Intel’s New 224G PAM4 Transceivers

by Dr. Ian Cutress on August 21, 2020 3:00 PM EST

One battleground in the world of FPGAs is the transceiver – the ability to bring in (or push out) high speed signals onto an FPGA at low power. In a world where FPGAs offer the ultimate ability in re-programmable logic, having multiple transceivers to bring in the bandwidth is a key part of design. This is why SmartNICs and dense server-to-server interconnect topologies all rely on FPGAs for initial deployment and adaptation, before perhaps moving to an ASIC. As a result, the key FPGA companies that play in this space often look at high-speed transceiver adoption and design as part of the product portfolio.

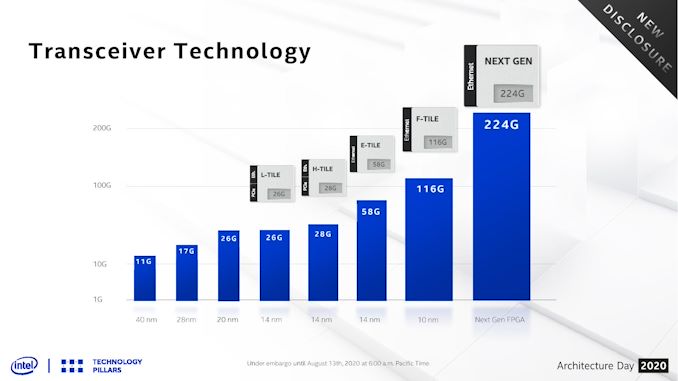

In recent memory, Xilinx and Altera (now Intel), have been going back and forth, talking about 26G transceivers, 28G transceivers, 56G/58G, and we were given a glimpse into the 116G transceivers that Intel will implement as an option for its M-Series 10nm Agilex FPGAs back at Arch Day 2018. The Ethernet based 116G ‘F-Tile’ is a separate chiplet module connected to the central Agilex FPGA through an Embedded Multi-Die Interconnect Bridge (EMIB), as it is built on a different process to the main FPGA.

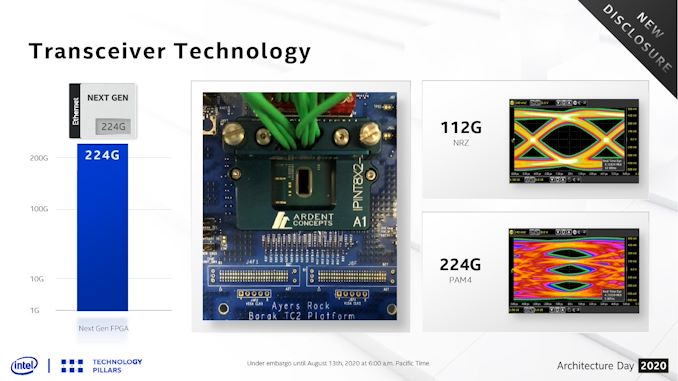

As part of Intel’s Architecture Day 2020, the company announced that it is now working on a new higher speed module, rated at 224G. This module is set to support both 224G in a PAM4 mode (4-bits) and 112G in an NRZ mode (2-bits). This should enable future generations of the Ethernet protocol stack, and Intel says it will be ready in late 2021/2022 and will be backwards compatible with the Agilex hardened 100/200/400 GbE stack. Intel didn’t go into any detail about bit-error rates or power at this time, but did show a couple of fancy eye diagrams.

Related Reading

- Intel Launches Stratix 10 TX: Leveraging EMIB with 58G Transceivers

- Hot Chips 2020 Live Blog: Intel 10nm Agilex FPGAs (8:30am PT)

- Intel’s EMIB Now Between Two High TDP Die: The New Stratix 10 GX 10M FPGA

- Xilinx Announces World Largest FPGA: Virtex Ultrascale+ VU19P with 9m Cells

- Intel Agilex: 10nm FPGAs with PCIe 5.0, DDR5, and CXL

_carousel_thumb.jpg)

_carousel_thumb.jpg)

11 Comments

View All Comments

back2future - Wednesday, August 26, 2020 - link

for example Agilex I-Series IP shows for F-Tile"Transceiver channel count :- 4 channels at 116 Gbps (PAM4) / 58 Gbps (NRZ)- 16 channels at 32 Gbps (NRZ) /12 channels at 58 Gbps (PAM4) - RS & KP FEC"

(probably one channel is two differential signal lanes, full duplex?)