Intel Alder Lake: Confirmed x86 Hybrid with Golden Cove and Gracemont for 2021

by Dr. Ian Cutress on August 14, 2020 1:05 PM EST- Posted in

- CPUs

- Intel

- Alder Lake

- Hybrid

- Intel Arch Day 2020

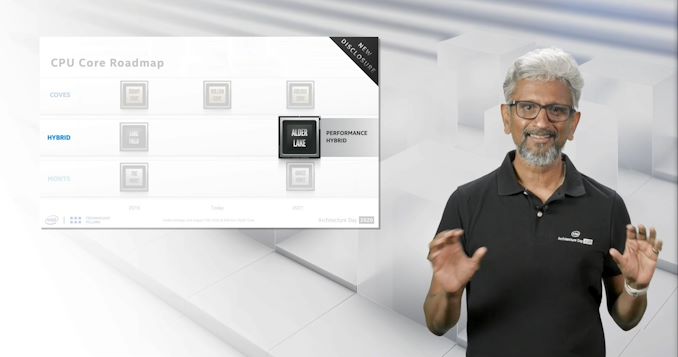

Following leaks is often a game of cat and mouse – what is actually legitimate and what might not be. Traditionally AnandTech shies away from leaks for that very reason, and we prefer to have multiple sources that are saying the same thing, rather than addressing every potential rumor on the blogosphere. Nonetheless, hints towards a new product from Intel, Alder Lake, have been cropping up over the past few months, including getting a small mention in Intel’s Q2 2020 earnings. The leaks have suggested that it would offer a mixed Hybrid x86 environment similar to Intel’s current Lakefield product that uses high-performance cores paired with high-efficiency cores. As part of Intel’s Architecture Day 2020, the company officially announced Alder Lake as a hybrid x86 product on its roadmaps.

In the roadmap and as part of the discussions, Intel’s Raja Koduri confirms that Alder Lake will be a combination of the Golden Cove high performance computing core and the Gracemont high efficiency core, and the goal of this chip is to offer a ‘Performance Hybrid’ option into the portfolio. Raja explained to the audience that the company has learned a lot due to building Lakefield, its current hybrid x86 chip for thin and light notebooks, and while Lakefield was focused on battery life, Alder Lake will focus instead on performance.

Alder Lake will involve Intel’s next generation hardware scheduler, which we are told will be able to leverage all cores for performance and make it seamless to any software package. Intel claims that Alder Lake will be Intel’s best (ever? 2021?) performance-per-watt processor.

If leaks are to be believed, then Alder Lake looks set to offer an 8+8 design, although that has not been confirmed. Intel did not go into detail if Alder Lake will involve any next generation packaging, such as Foveros (which Lakefield does) – but in the Q2 2020 financial disclosures, it was said to be positioned for mobile and desktops. We expect Intel to discuss Golden Cove and Gracemont at some point next year, and then Alder Lake as an extension to those – we have already seen Intel documents regarding new instructions for each of these cores. My prediction is to come back this time next year, where we should have more to talk about.

Related Reading

- Intel Updates ISA Manual: New Instructions for Alder Lake, also BF16 for Sapphire Rapids

- Intel Roadmap Update: Alder Lake In H2’21, Ice Lake-SP Late This Year

- Intel’s 11th Gen Core Tiger Lake SoC Detailed: SuperFin, Willow Cove and Xe-LP

- The Intel Xe-LP GPU Architecture Deep Dive: Building Up The Next Generation

- The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

89 Comments

View All Comments

nandnandnand - Saturday, August 15, 2020 - link

4 big+8 little might be able to match the multi-threaded performance of a normal 8-core. Same with 8 big+8 little vs. a normal 12-core.Cancel out the big cores and it comes down to: can 8 "Gracemont" Atom cores perform as well as 4 big cores? Maybe, if all of them are being used, the clock speeds aren't very low, and other conditions are right.

ksec - Saturday, August 15, 2020 - link

Lots of talk. It reads to me Intel is trying to do damage control, hyping up some of their future product roadmap.We need to see how well Tigerlake execute and its volume. No use if you cant actually deliver anything.

Quantumz0d - Saturday, August 15, 2020 - link

Exactly. All they do is talk now. Rubbish Xe and this joke of a tech in Desktops, it's only made for that SMT loss against Ryzen, we already know how Zen absolutely kills SKL and all its successors in HT/SMT performance. With unified 8C CCDs in Zen 3 it's going to break havoc on Intel for sure.It's like they want to get that SMT performance, I beleive that's the only reason to add those in Desktop, adding a small x86 Atom cores will net some performance in the loss of more cores and SMT. Zen 3 is going big with 8C CCDs and unified Cache. It's going to be crazy fast with the 3300X as proof of that.

Intel really cannot do more than 10C on SKL, so RKL is 8C tops from the rumors and this is also looking same, past 8C no more ring bus, and perhaps on this +2 cores will result in high power consumption, if they axe ring bus they will lose gaming performance and SMT. Only way is to cram more x86 cores for that SMT/Physical cores loss.

Tomatotech - Saturday, August 15, 2020 - link

I'm quite keen on adding small cores to desktops. Most desktops spend most of their time doing nothing, so it makes sense to have a few small cores to take care of checking email, tidying up the SSD, running backups and other background operations. Good for the environment and reducing power bills. It will mean much of the low power code can be removed from the big cores, freeing up space on them for the high-power circuits.nandnandnand - Saturday, August 15, 2020 - link

These Atom cores should be about 25% the die area, but what, 50-70% the performance?Beyond an initial 8 or so big cores, adding many small Atom cores makes sense. They could put 40 cores (8+32) in a die area similar to a normal 16-core.

JayNor - Sunday, August 16, 2020 - link

\Perhaps the real competition is Gracemont + Golden Cove vs AMD SMT pair.Meteor2 - Monday, August 17, 2020 - link

Given how low Intel Core cores can clock down and how much silicon they can simply shut down, with power draws dropping <1W, power-savings from including Mont cores will be effectively invisible.JayNor - Sunday, August 16, 2020 - link

Perhaps they will do the dual ring bus on Rocket Lake, as on Tiger Lake.Santoval - Saturday, August 15, 2020 - link

Alder Lake will not compete against Zen 3 based parts but against Zen 4 ones. The Zen 3 generation will bring no core increases but the Zen 4 one will, along with the introduction of AVX-512, DDR5 and probably PCIe 5.0 and CXL as well. Alder Lake should support DDR5 -and probably PCIe 5.0- as well, since Tiger Lake-U will already support LPDDR5.AMD should retain the chiplet scheme with their Zen 4 launch, I don't think that is going away. Zen 3 will unify the L3 cache, thus the two 4-core CCXs will be merged, so each 8-core chiplet will be monolithic, not split in 2 CCXs. Perhaps with Zen 4 they are going to re-introduce CCXs but with a 6-core CCX as a base (for 12-core chiplets)? I don't know, wouldn't that be a step backwards? Perhaps it would be best to make monolithic 12-core chiplets and use 6 cores as a base for their Zen 4 APUs, up to maybe 12 cores.

It's also unclear whether AMD will introduce a big-little scheme or not. From an energy efficiency point of view it would make sense. From a performance one it might not. It is still unclear if the Golden Cove cores of Alder Lake will need to be handicapped in order to match the features of the Gracemont cores or not.

nandnandnand - Saturday, August 15, 2020 - link

I don't think they need to respond to big/small right now. If Intel was pitting a 40-core (8+32) against AMD's 16-core, that would be crazy and could deserve a response. But the leaks say it tops out at 8+8, which might be comparable to AMD's 12-core.I think they might stick to the 8-core chiplet, and just use three of them for up to 24 cores, maybe four for 32 cores in a later generation. Games will mostly be using 8 cores due to XSX/PS5. Let games hog a full 8-core chiplet for the best performance, and use the defective chiplets with cores disabled for background tasks.

The most interesting feature could be L4 cache stacked on the I/O die. If they pull it off, certain games and workloads will benefit big time.