Qualcomm Announces New Snapdragon Wear 4100 & 4100+: 12nm A53 Smartwatches

by Andrei Frumusanu on June 30, 2020 11:00 AM EST- Posted in

- Wearables

- Qualcomm

- Snapdragon Wear

- Snapdragon Wear 4100

Today Qualcomm is making a big step forward in its smartwatch SoC offerings by introducing the brand-new Snapdragon Wear 4100 and Wear 4100+ platforms. The new chips succeed the aging two 2018 originating Wear 3100 platforms and significantly upgrading the hardware specifications, bringing to the table all new IPs for CPU, GPU and DSPs, all manufactured on a newer lower power process node.

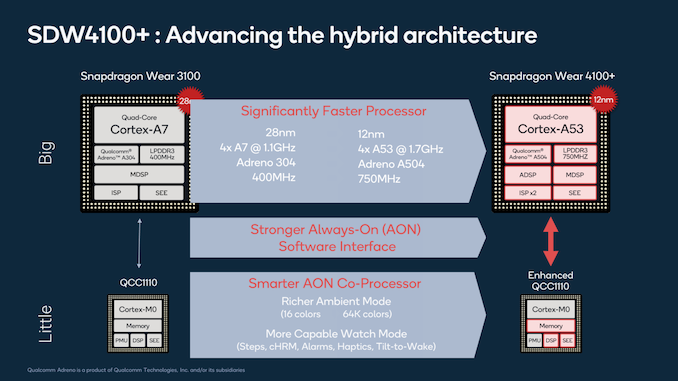

Smartwatch products over the last few years had always one big criticism to them, and that was the fact that the SoCs powering them were always seemingly underpowered compared to what we’re seeing from the like of vertically integrated vendors such as Apple and their own smartwatch SoCs. Qualcomm’s new Wear 4100 SoC now finally abandons the Cortex-A7 cores and 28nm process in favour of Cortex-A53 cores and a 12nm process – whilst certainly not bleeding edge, it’s a big jump in performance and power efficiency.

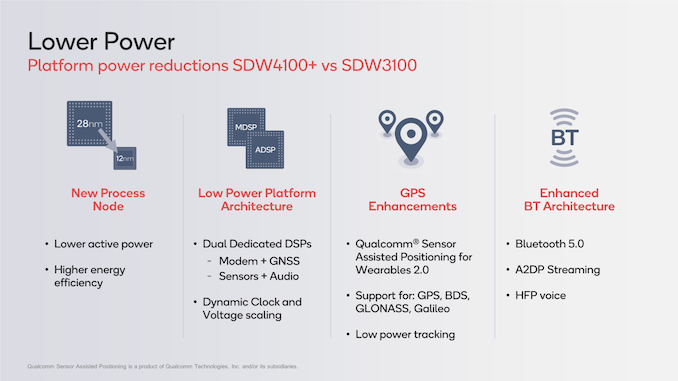

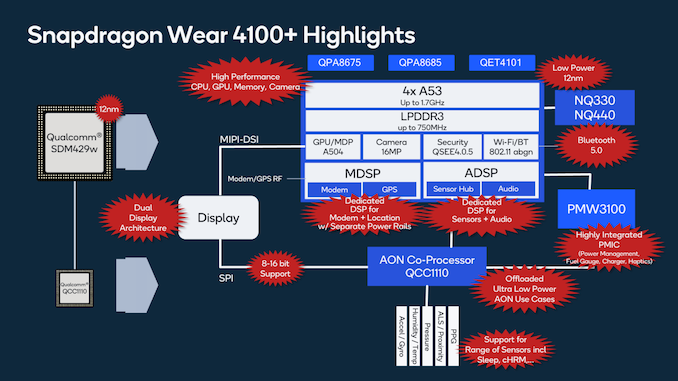

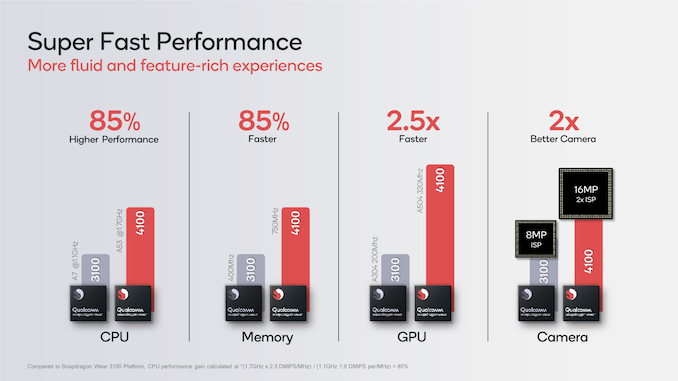

The new SoC is a complete overhaul in terms of design. As mentioned, instead of the quad-core A7 cores at 1.1GHz, the new chip now features quad A53 cores at up to 1.7GHz. The chip still relies on LPDDR3 as its memory technology but the clock rates have been upped from 400MHz to 750Mhz. The GPU has seen a giant leap in performance as it sees the jump of 2 architectural generations from an Adreno 304 to a new Adreno 504. The chipset also seen its DSP capabilities expanded as it now features a second dedicated audio DSP for actual application side processing (Alongside the modem DSP) that previously didn’t exist on the Wear 3100 chip.

An interesting addition to the SoC is a second ISP. The new chip is able to now handle dual 16MP cameras – some of Qualcomm’s customers have ideas for smartwatch products which would deploy two cameras.

The main SoC is now manufactured on a newer 12nm process node at TSMC – it’s certainly not the newest node given a new platform like this, but Qualcomm probably made their cost-performance calculations when choosing this design aspect.

It's to be noted that it looks like Qualcomm did recycle the design from the Snapdragon 429 - although it's possible the Wear variant here might be specifically binned for low power usage.

Connectivity wise, the chip still employs a LTE category 4 modem with up to 150Mbps down and 50Mbps up speeds, but the new RF system includes optimisations for power usage, such as the new addition of eDRX (Extended discontinuous reception) for much better power efficiency. Bluetooth connectivity has been upgraded to the 5.0 standard.

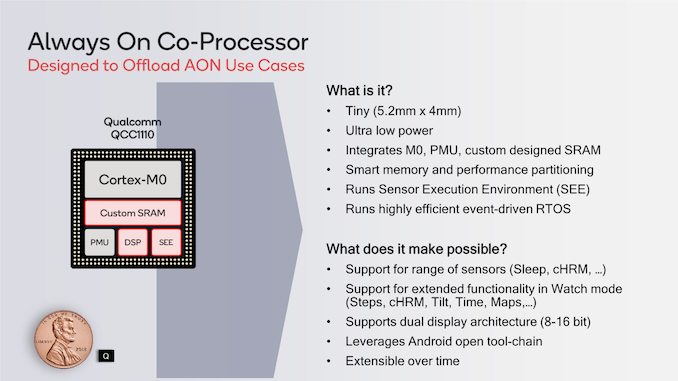

Qualcomm continues to use a main SoC + co-processor architecture for its smartwatch platforms. The aforementioned Wear 4100 serves as the main processor chip during active and interactive usage of the device, whilst a secondary co-processor serves as the always-on silicon that is able to enable ambient non-interactive device use-cases (Essentially, powering on the screen with static / low-updating information).

The co-processor has a similar design to the QCC1110 that was bundled with the Wear 3100 platform, but has been enhanced in terms of some of its capabilities such as having richer colour depth rendering ability for up to 16 bit (64K colours).

The key aspect for using both a main SoC and a co-processor in the same device is the dual display architecture of the system, where the display is connected to both chip and can receive signals from both. The reason for Qualcomm to not have implemented a single monolithic chip is rationalised by design efforts and cost-opportunity; while they haven’t announced any products yet, they envision the possibility to use the QCC1110 as a standalone system in a device, and likewise, one can use the Wear 4100 without a co-processor.

The co-processor can serve as the sensor hub collecting data from your typical smartwatch sensors, all whilst the main SoC is powered off.

The overall improvements of the platforms bring a -20% decrease in power usage, all whilst increasing CPU performance by 85%, GPU performance by a massive factor of 2.5x. In terms of workload efficiency, you’ll be seeing significant increases – all needed in wearable devices as battery life is key.

The Snapdragon Wear 4100 platform represents the main SoC and surrounding essential components, whilst the Wear 4100+ platform also includes the co-processor for augmented always-on operation. The new platforms are available and shipping to vendors now.

Related Reading:

- Qualcomm Launches Snapdragon Wear 3100 Platform for Smartwatches

- Qualcomm Announces Snapdragon Wear 2100 IoT SoC

- Qualcomm Announces Snapdragon Wear 1200 SoC: LTE Categories M1 & NB1 for Wearables & Smart Trackers

- Qualcomm Announces Snapdragon Wear 1100 SoC For Wearables

- Apple Announces The Apple Watch 4: Fully Custom SiP

33 Comments

View All Comments

unrulycow - Tuesday, June 30, 2020 - link

This is a nice improvement over the terrible last gen, but they should have used A55 cores to at least pretend to be a modern chipMarlin1975 - Tuesday, June 30, 2020 - link

This is just a under clocked Snapdragon 429. Either they made to many or they are so cheap to make they just had more made for this re-naming.The 429 is from late 2018. So about 2 years old so easy to produce and little to no bugs.

Frenetic Pony - Wednesday, July 1, 2020 - link

Why do that when you can just keep letting Apple dominate smartwatches because its the only vendor with modern silicon designed for the product category?Jon Tseng - Tuesday, June 30, 2020 - link

Surely a typo. For a moment I thought you were saying Qualcomm were launching a power-critical 2020 consumer part on 12nm!Oh...

dotjaz - Friday, July 10, 2020 - link

There's nothing wrong with using 12nm for "power-critical" part. In fact I would prefer 12nm over 7nm. There's a reason literally nobody wants to use 10nm and below for those low-energy parts. And they never will. The leakage is just too high. Samsung's 10nm is probably fine because of it's lower density.Apple didn't confirm it's S series process node, bot the first chip launched in 2015 was using 2013's 28HKMG. I would actually believe S5 is still on 12nm.

dotjaz - Friday, July 10, 2020 - link

Or even better, 22nm.dotjaz - Friday, July 10, 2020 - link

In fact ALL foundries offer ULP nodes based on larger "nm" nodes. Intel's 22FFL, TSMC's 22ULP/ULL and future 12FFC+ULL, Samsung's 28FDS and future 18FDS/8LPU, GloFo's 22FDX-ULL, UMC's 22uLPThese are ALL 2019 and beyond processes. None of them went below 10nm, the most aggressive is Samsung who labels 8LPU (still part of their 10nm platform) as ULP.

jeremyshaw - Tuesday, June 30, 2020 - link

So are they targeting the older tech (process and CPU arch) for low cost and lack of market, or are they going there for something like...? Low leakage? Maturity?WithoutWeakness - Tuesday, June 30, 2020 - link

Qualcomm has thrown in the towel on warables. Low volume and low margin for them compared to smartphone, tablet, and 2-in-1 SOCs. They make their money on their wireless technology and patents and have carved out a monopoly in the high-end Android SOC space for every manufacturer except Huawei. They have no reason to throw the best cores and latest lithography at this chip because there is no incentive for them to spend the money on it.MrSpadge - Tuesday, June 30, 2020 - link

Cost is surely a reason.