Arm's New Cortex-A78 and Cortex-X1 Microarchitectures: An Efficiency and Performance Divergence

by Andrei Frumusanu on May 26, 2020 9:00 AM EST- Posted in

- SoCs

- CPUs

- Arm

- Smartphones

- Mobile

- GPUs

- Cortex

- Cortex A78

- Cortex X1

- Mali G78

The Cortex-X1 Micro-architecture: Bigger, Fatter, More Performance

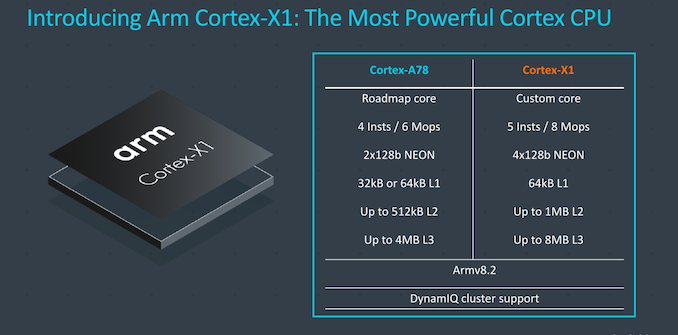

While the Cortex-A78 seems relatively tame in its performance goals, today’s biggest announcement is the far more aggressive Cortex-X1. As already noted, Cortex-X1 is a significant departure from Arm's usual "balanced" design philosophy, with Arm designing a core that favors absolute performance, even if it comes at the cost of energy efficiency and space efficiency.

At a high level, the design could be summed up as being a ultra-charged A78 – maintaining the same functional principles, but increasing the structures of the core significantly in order to maximize performance.

Compared to an A78, it’s a wider core, going up from a 4- to a 5-wide decoder, increasing the renaming bandwidth to up to 8 Mops/cycle, and also vastly changing up some of the pipelines and caches, doubling up on the NEON unit, and double the L2 and L3 caches.

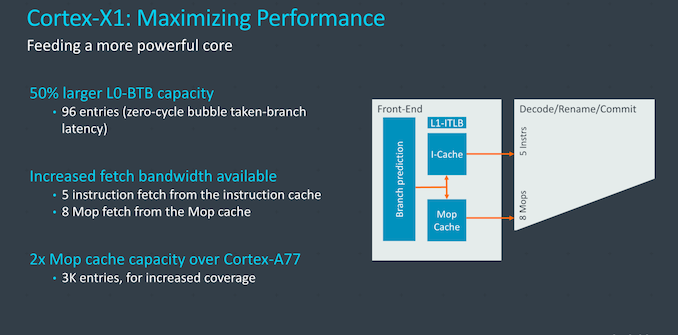

On the front-end (and valid the rest of the core as well), the Cortex-X1 adopts all the improvements that we’ve already covered on the Cortex-A78, including the new branch units. On top of the changes the A78 introduced, the X1 further grows some aspects of the blocks here. The L0 BTB has been upgraded from 64 entries on the Cortex-A77 and A78, to up to 96 entries on the X1, allowing for more zero latency taken branches. The branch target buffers are still of a two-tier hierarchy with the L0 and L2 BTBs, which Arm in previous disclosures referred to as the nanoBTB and mainBTB. The microBTB/L1 BTB was present in the A76 but had been subsequently discontinued.

The macro-op cache has been outright doubled from 1.5K entries to 3K entries, making this a big structure amongst the publicly disclosed microarchitectures out there, bigger than even Sunny Cove’s 2.25K entries, but shy of Zen2’s 4K entry structure - although we do have to make the disambiguation that Arm talks about macro-ops while Intel and AMD talk about micro-op caches.

The fetch bandwidth out of the L1I has been bumped up 25% from 4 to 5 instructions with a corresponding increase in the decoder bandwidth, and the fetch and rename bandwidth out of the Mop-cache has seen a 33% increase from 6 to 8 instructions per cycle. In effect, the core can act as a 8-wide machine as long as it’s hitting the Mop cache.

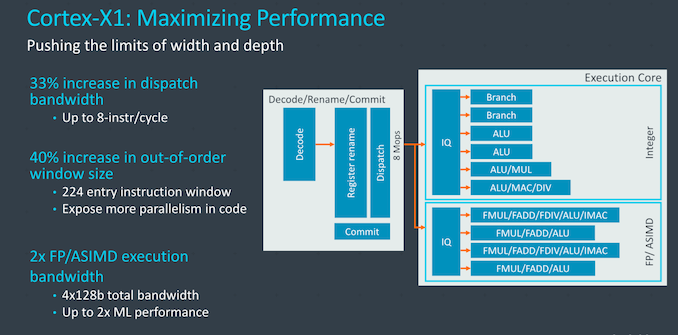

On the mid-core, Arm here again talks about increasing the dispatch bandwidth in terms of Mops or instructions per cycle, increasing it by 33% from 6 to 8 when comparing the X1 to the A78. In µops terms the core can handle up to 16 dispatches per cycle when cracking Mops fully into smaller µops, in that regard, representing a 60% increase compared to the 10µops/cycle the A77 was able to achieve.

The out-of-order window size has been increased from 160 to 224 entries, increasing the ability for the core to extract ILP. This had always been an aspect Arm had been hesitant to upgrade as they had mentioned that performance doesn’t scale nearly as linearly with the increased structure size, and it comes at a cost of power and area. The X1 here is able to make those compromises given that it doesn’t have to target an as wide range of vendor implementations.

On the execution side, we don’t see any changes on the part of the integer pipelines compared to the A78, however the floating point and NEON pipelines more significantly diverge from past microarchitectures, thanks to the doubling of the pipelines. Doubling here can actually be taken in the literal sense, as the two existing pipelines of the A77 and A78 are essentially copy-pasted again, and the two pairs of units are identical in their capabilities. That’s a quite huge improvement and increase in execution resources.

In effect, the Cortex-X1 is now a 4x128b SIMD machine, pretty much equal in vector execution width as some desktop cores such as Intel’s Sunny Cove or AMD’s Zen2. Though unlike those designs, Arm's current ISA doesn't allow for individual vectors to be larger than 128b, which is something to be addressed in a next generation core.

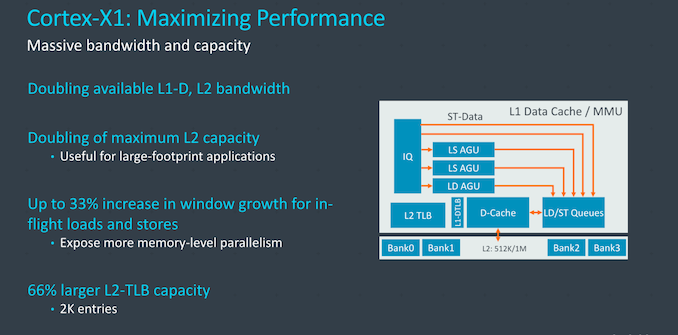

On the memory subsystem side, the Cortex-X1 also sees some significant changes – although the AGU setup is the same as that found on the Cortex-A78.

On the part of the L1D and L2 caches, Arm has created new designs that differ in their access bandwidth. The interfaces to the caches here aren’t wider, but rather what’s changed is the caches designs themselves, now implementing double the memory banks. What this solves is possible bank conflicts when doing multiple concurrent accesses to the caches, it’s something that we may have observed with odd “zig-zag” patterns in our memory tests of the Cortex-A76 cores a few years back, and still present in some variations of that µarch.

The L1I and L1D caches on the X1 are meant to be configured at 64KB. On the L2, because it’s a brand new design, Arm also took the opportunity to increase the maximum size of the cache which now doubles up to 1MB. Again, this actually isn’t the same 1MB L2 cache design that we first saw on the Neoverse-N1, but a new implementation. The access latency is 1 cycle better than the 11-cyle variant of the N1, achieving 10 cycles on the X1, regardless of the size of the cache.

The memory subsystem also increases the capability to support more loads and stores, increasing the window here by 33%, adding even more onto the MLP ability of the core. We have to note that this increase not merely refers to the store and load buffers but the whole system’s capabilities with tracking and servicing requests.

Finally, the L2 TLB has also seen a doubling in size compared to the A78 (66% increase vs A77) with 2K entries coverage, serving up to 8MB of memory at 4K pages, which makes for a good fit for the envisioned 8MB L3 cache for target X1 implementations.

The doubling of the L3 cache in the DSU doesn’t necessarily mean that it’s going to be a slower implementation, as the latency can be the same, but depending on partner implementations it can mean a few extra cycles of latency. Likely what this is referring to is likely the option for banking the L3 with separated power management. To date, I haven’t heard of any vendors using this feature of the DSU as most implementers such as Qualcomm have always had the 4MB L3 fully powered on all the time. It is possible that with a 8MB DSU that some vendors might look into power managing this better, for example it having being only partially powered on as long as only little cores are active.

Overall, what’s clear here about the Cortex-X1 microarchitecture is that it’s largely consisting of the same fundamental building blocks as that of the Cortex-A78, but only having bigger and more of the structures. It’s particularly with the front-end and the mid-core where the X1 really supersizes things compared to the A78, being a much wider microarchitecture at heart. The arguments about the low return on investment on some structures here just don’t apply on the X1, and Arm went for the biggest configurations that were feasible and reasonable, even if that grows the size of the core and increases power consumption.

I think the real only design constraints the company set themselves here is in terms of the frequency capabilities of the X1. It’s still a very short pipeline design with a 10-cycle branch mispredict penalty and a 13-stage deep frequency design, and this remains the same between the A78 and X1, with the latter’s bigger structures and wider design not handicapping the peak frequencies of the core.

192 Comments

View All Comments

Andrei Frumusanu - Wednesday, June 3, 2020 - link

> The choice to switch to LLVM was stupid at the time, but even more so today since GCC has since moved further ahead of LLVM...GCC's problem is its license. Apple nor Google would be able to integrate it into the IDE like Xcode/Android Studio. In the grand scheme of things, going LLVM is a much better choice, even if it's slower than GCC.

ksec - Tuesday, May 26, 2020 - link

The 40-45% figure assumes X-1 could run at 3Ghz within its TDP budget.And even with that in mind the figures Anandtech put up shows it is still behind A13.

Not bad for the rest of the ARM ecosystem. But still not quite there yet.

MarcGP - Tuesday, May 26, 2020 - link

Behind the A13 ?, you missed the estimation chart where it shows the X1 reaching the A13 performance (a bit lower in integer performance and a bit higher in floating poing performance) at a much lower power consumption.ksec - Wednesday, May 27, 2020 - link

Behind in IPC. The chart put the X1 with an 5nm node with 15% clock speed increase against a 7nm Node A13 with non sustainable 2.63 Ghz Clock.Also worth noting this is 7nm+ not 7nm EUV from TSMC. So if you put the node aside those number would likely still put it under A13.

dotjaz - Tuesday, May 26, 2020 - link

You understand INCORRECTLY. 30% is for the same frequency and 20% is the same power. you DID read it wrong.dotjaz - Tuesday, May 26, 2020 - link

With the same baseline, A77@2.6GHz, then A78@3GHz is +20%, X1@3GHz is +50%ZolaIII - Wednesday, May 27, 2020 - link

Nope you are wrong. First off all given constant power delta for something which goes into phone the A78 will be a rather significant improvement over A77 with same performance at half the power budget. A77 already had a lead over Apple big core's regarding the performance/W metric & and this means more than brute force approach. Yes Apple big core's are supperio but on something that has power budget of a laptop. On the other hand X1 is a direct take on those apple core's & it should be up to 2x faster than A78 in tasks which are optimised and utilities FP SIMDs basically SMP tasks. This is more relevant to server tasks and not so much for mobile space, still I would like to see more advanced SIMD blocks and their inclusion on smaller core's with SMT as SIMDs are hard to feed optimally and front end expansion there for is a must but it can be done in a more elegant manner like for instance MIPS did with VMT. ARM desperately needs power efficient basic OoO core a successor of A73 if you like with DynamiQ integration as an A55 replacement. Their is a A65AE but we didn't seen any implementation of it in any space so far.Santoval - Friday, May 29, 2020 - link

It is not even an apples for apples comparison, since A78 has +20% *sustained* performance over A77, while X1 has +30% *peak* performance. Therefore the sustained performance lead of X1 over A77 might be in the +25% ballpark. Is a mere extra 5 - 10% performance over A78 really worth a 30% larger die area and quite higher TDP? Unless Arm can increase the performance lead of X1 over A78 at least another 20% I don't see the former being an attractive (or even a sane) licence and purchasing option.ChrisGX - Monday, July 6, 2020 - link

The X1 exhibits 22% performance advantage over the A78 when process and frequency are controlled factors. So, yes, X1 performance is 1.22xA78. The performance improvement of the A78 over the A77 however includes a process node and frequency change, 20% all up. So, the performance of the X1 is: (A77 * 1.2) * 1.22 or 1.46xA77.ChrisGX - Monday, July 6, 2020 - link

Please note Andrei seems to have made assumptions something like this in his calculations with A77 SPECspeed/performance at 2.6GHz being something in the order of 32 (which seems reasonable).