PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

by Ryan Smith on October 15, 2019 10:30 AM EST

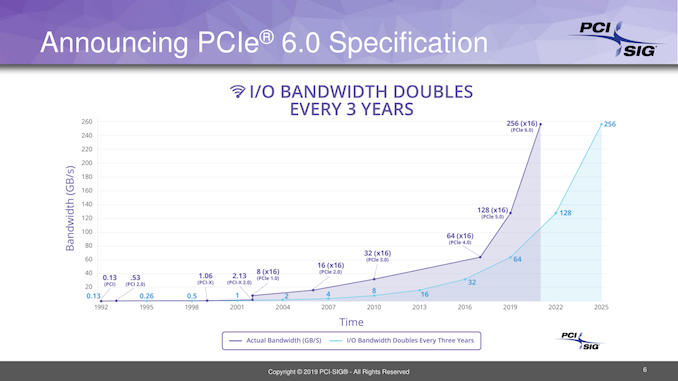

Having wrapped up their work on the PCI-Express 5.0 specification earlier this year, the PCI-SIG wasted no time in getting to work on the next version of the specification, PCIe 6.0. That specification, which is expected to be finished in 2021, will once again double PCIe’s bandwidth to 64 GigaTransfers/second – or roughly 128GB/sec (each direction) for a x16 slot – thanks to some high-end encoding technologies like PAM4.

At the time that PCIe 6.0 was first announced, the group was just beginning work on the specification. And now a few scant months later, the group has released a brief update, announcing that they have already completed version 0.3 of the new spec.

The announcement itself is light on technical details, as the design goals and major underlying technologies for PCIe 6.0 were announced at the very start of the project. However the organization is keen to ensure that PCIe development continues moving at a steady pace, to avoid repeating the long gap between 3.0 and 4.0.

And the group’s members will certainly be busy. Even with the 0.3 specification in hand, it’s going to be nearly another two years before the specification is done, reflecting on the fact that there’s a lot of work left to be done to solve the technical challenges in developing PCIe 6.0, and bringing new signaling standards into the specification while maintaining backwards compatibility.

Source: PCI-SIG

45 Comments

View All Comments

PeachNCream - Wednesday, October 16, 2019 - link

No I didn't make any assumptions. I described an alternative approach that I personally use with respect to playing video games on a PC. There are no assumptions, but simply statements that support a perspective that you find personally threatening to such an extent that you found it necessary to attempt to respond by discrediting and then using a bandwagon fallacy.rpg1966 - Wednesday, October 16, 2019 - link

Well then he also described an approach. If he was making assumptions, so were you. Or you both weren't. See? Pedantic, isn't it.PeachNCream - Thursday, October 17, 2019 - link

It's fun to watch you try, at least.CaedenV - Wednesday, October 16, 2019 - link

I am running an ancient i7 2600 with a gtx 1080, and the benchmarks and real world results I get for 4k gaming on a 55" display are only 1 to 2 frames lower than what is claimed on many benchmarking sites.... Point being that the bottleneck these days is not the cpu or the interconnect, it is still on the GPU and SSD where it has been for about a decade now. The same can be said about server applications where most of the bottleneck is on storage, ram, and encryption.CaedenV - Wednesday, October 16, 2019 - link

Well, that is just my point. The end user world is still running at a pcie2 level even if we have faster connections available.My question really is "what crazy amazing options and applications is this new tech opening up?" it clearly isn't in the consumer space, so I would like to see where it is being used

r3loaded - Tuesday, October 15, 2019 - link

> Is the point just to have fewer but faster lanes available?Yep, partially.

> Or to use as a cpu core interconnect? Or is there some amazing real world application that truly needs this kind of speed that we just are not hearing about yet?

The likes of CXL, Gen-Z, CCIX etc which are all based on PCIe 5.0 are working towards cache coherency between CPUs, GPUs, FPGAs, neural network accelerators and other kinds of processing cores. This will make it much easier to develop software that can do seamless heterogeneous computing without having to worry about transferring data between these cores. So, yes!

rpg1966 - Wednesday, October 16, 2019 - link

" without having to worry about transferring data between these cores"Can you clarify that for a dummy? Doesn't cache coherency involve moving data between the various caches anyway?

Kenshiro70 - Wednesday, October 16, 2019 - link

I suspect what he meant to say was:"without having to worry about [the additional latency penalty that currently impacts] transferring data between these cores"

In other words, you're correct about cache coherency, but over time maintaining coherency has become one of the biggest bottlenecks to parallel computing as other areas have been optimized.

CaedenV - Wednesday, October 16, 2019 - link

Very cool!You may be the only person that u derstood the point of my question lol

Now I have some things to google

guycoder - Tuesday, October 15, 2019 - link

Fortunately the PCI sig group is not working to upgrade your personal PC. PCIe is used in many places, especially the data center, where extra bandwidth and performance is needed. Upcoming challenges of integrating heterogeneous architectures will require a very large jump in bandwidth and reduced latency and we seem to be standardizing on the PCIe physical layer to connect all these devices together. Your local desktop and graphics card / nvme SSD are probably not primary use cases for this upgrade but help drive adoption and cost reduction. Think AI/Machine Learning accelerators running in the cloud processing more and more data that ends up as some new feature on your phone or Facebook.