The Ice Lake Benchmark Preview: Inside Intel's 10nm

by Dr. Ian Cutress on August 1, 2019 9:00 AM EST- Posted in

- CPUs

- Intel

- GPUs

- 10nm

- Core

- Ice Lake

- Cannon Lake

- Sunny Cove

- 10th Gen Core

Gaming Results (15W and 25W)

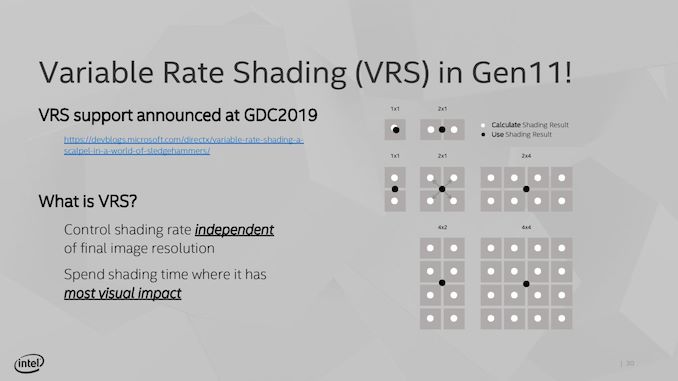

One of the biggest changes to the Ice Lake design is in the integrated graphics – Intel is now giving more focus and more die area to graphics, something it has arguably been neglecting for several years now. With Ice Lake, we move to a Gen11 graphics architecture, which is almost like the previous Gen9.5 but now with added support for variable rate shading (VRS), moving from 24 EUs to 64 EUs, and memory support up from LPDDR3-2133 to LPDDR4X-3733.

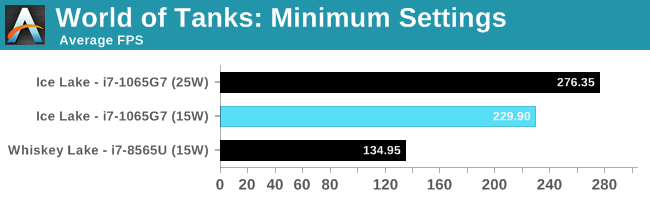

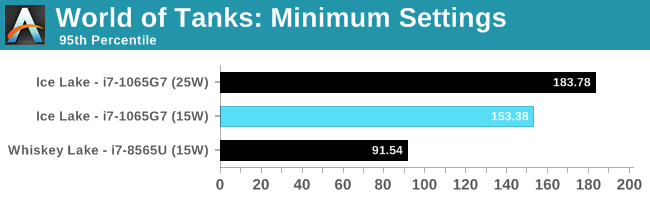

World of Tanks is a very CPU driven benchmark, and having the extra frequency of the 25W processor does help here. We're getting a sizeable uplift from Whiskey Lake, due to the extra EUs and memory frequency.

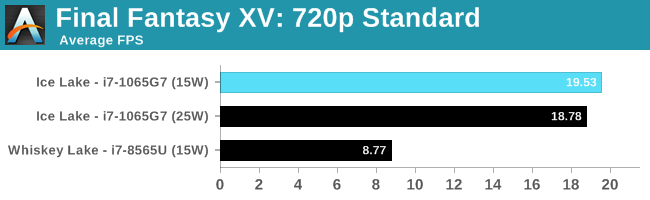

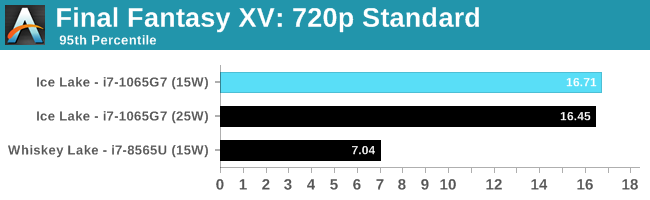

Our Final Fantasy test seemed to regress in 25W mode, although still within the noise. This test is still GPU bound, so adding the extra TDP to the CPU didn't actually help much. However, comparing to the Whiskey Lake integrated graphics, we've got over a 2x speedup.

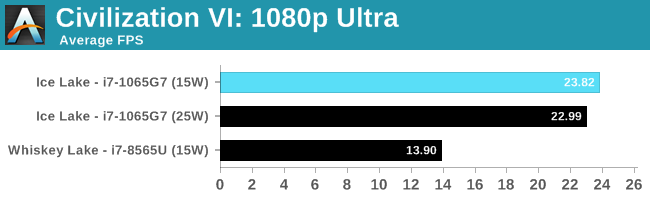

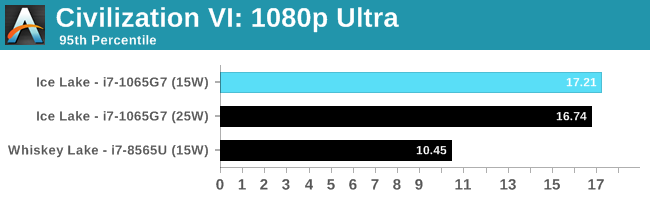

Similarly with Civilization, with what is normally our 'IGP' settings, we are still GPU limited here.

One of Intel's newest features is Variable Rate Shading.

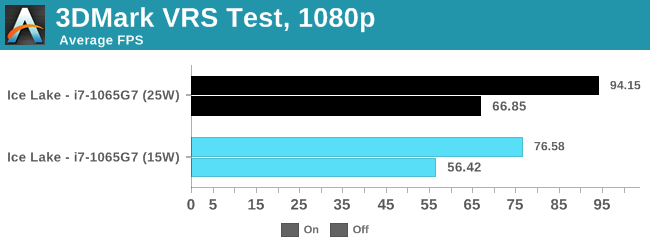

If developers add the option, soon to be an easy checkbox in Unity and Unreal, the game can decide to control the rate at which it shades pixels, from calculating every pixel down using one result across a 4x4 grid, to save compute power. Currently the only way to test this is with the 3DMark functional demo.

The new VRS test in 3DMark is designed as a feature test to show the potential uplift effect from enabling variable rate shading within a game. In both 15W and 25W modes, the data saw a good uplift, and we seemed to get more out of the 25W mode than the 15W mode.

261 Comments

View All Comments

tamalero - Monday, August 5, 2019 - link

the 3d mark VRS test graph is very confusing.MASSAMKULABOX - Tuesday, August 6, 2019 - link

These chips are priced quite high esp the i3's the Dualcore is outrageous (20$ discount for half the cores and threads?).They will only sell in limited qtys at such high prices . Bring on the 14nm equiv at sane prices.what discrete gfx does the IGPU equate to? gt1030 vs 2200g vs 3400ge??

Zhentar - Tuesday, August 6, 2019 - link

The bit per cycle throughput of REP STOS is really only half of the picture - the startup latency matters a lot too! On my Skylake, I've measured a minimum latency of 29 cycles* (any REP STOS from 1 byte to 128 bytes takes 29 cycle, then it starts going up from there). Some compilers make heavy use of it even for small stores/copies (VC6, first and foremost, but also the .NET JIT for stack zeroing), so it can be pretty important to performance in some scenarios.*I am no Agner Fog... nor anywhere close to him, this measurement should be taken with a grain of salt ;-)

ballsystemlord - Wednesday, August 7, 2019 - link

@Ian

Sunny Cove SIMD chart and others have many asterisks, why?

"POPCNT Microcode 50% faster than SW (under L1-D size)"

What does this mean? The CPU uses microcode and HW, not SW, AFAIK, much less use it to implement the POPCNT instruction.

ballsystemlord - Thursday, August 8, 2019 - link

Spelling and grammar errors:Insert: I've been commenting corrections for at least 1 year now, if you guys want me to change the format, or have any request regarding phrasing, etc., just ask. Thanks for your work!

"L3 latencies look similar, however we'll dwell into that just in a bit."

I think you ment delve:

"L3 latencies look similar, however we'll delve into that just in a bit."

"IPC increases against the mobile Skylake are 33 and 38% in the integer and fp suites, though we also have to keep in d mind these figures go beyond just the Sunny Cove architecture and also include improvements through the new LPDDR4X memory controllers."

Missing percent sign and stray "d".

"IPC increases against the mobile Skylake are 33% and 38% in the integer and fp suites, though we also have to keep in mind these figures go beyond just the Sunny Cove architecture and also include improvements through the new LPDDR4X memory controllers."

"...which did not go down to well."

You mean "too" not "to":

"...which did not go down too well."

"...we actually see a number of key microarchitectural improvements bubble up through in our SPEC testing."

Excess "in":

"...we actually see a number of key microarchitectural improvements bubble up through our SPEC testing."

alysdexia - Thursday, November 28, 2019 - link

I think you mean Baalsystemlord or Bàqhàlsýstemlord.Grammar is a barbarism of ghrammatics, another word for composition or handwriting, font, format, spacing, the looks, whereas you meant diction/lecsis or register, vocabulary, declension, placement, spelling, the meaning.

you guys -> ye

nils_ - Monday, August 19, 2019 - link

I noticed on Intel Ark that Ice Lake CPUs do not have TSX instructions enabled / available. THis is interesting, since I believe TSX has also been used for some of the spectre attacks.ikjadoon - Thursday, September 12, 2019 - link

On 'Gaming Results (15W and 25W)', the graph is colored incorrectly. "On" and "Off" have the same color...and the legend colors are somehow not related to the graphic?