The Ice Lake Benchmark Preview: Inside Intel's 10nm

by Dr. Ian Cutress on August 1, 2019 9:00 AM EST- Posted in

- CPUs

- Intel

- GPUs

- 10nm

- Core

- Ice Lake

- Cannon Lake

- Sunny Cove

- 10th Gen Core

Section by Andrei Frumusanu

SPEC2017 and SPEC2006 Results (15W)

SPEC2017 and SPEC2006 is a series of standardized tests used to probe the overall performance between different systems, different architectures, different microarchitectures, and setups. The code has to be compiled, and then the results can be submitted to an online database for comparsion. It covers a range of integer and floating point workloads, and can be very optimized for each CPU, so it is important to check how the benchmarks are being compiled and run.

We run the tests in a harness built through Windows Subsystem for Linux, developed by our own Andrei Frumusanu. WSL has some odd quirks, with one test not running due to a WSL fixed stack size, but for like-for-like testing is good enough. SPEC2006 is deprecated in favor of 2017, but remains an interesting comparison point in our data. Because our scores aren’t official submissions, as per SPEC guidelines we have to declare them as internal estimates from our part.

For compilers, we use LLVM both for C/C++ and Fortan tests, and for Fortran we’re using the Flang compiler. The rationale of using LLVM over GCC is better cross-platform comparisons to platforms that have only have LLVM support and future articles where we’ll investigate this aspect more. We’re not considering closed-sourced compilers such as MSVC or ICC.

clang version 8.0.0-svn350067-1~exp1+0~20181226174230.701~1.gbp6019f2 (trunk)

clang version 7.0.1 (ssh://git@github.com/flang-compiler/flang-driver.git

24bd54da5c41af04838bbe7b68f830840d47fc03)-Ofast -fomit-frame-pointer

-march=x86-64

-mtune=core-avx2

-mfma -mavx -mavx2

Our compiler flags are straightforward, with basic –Ofast and relevant ISA switches to allow for AVX2 instructions. Despite ICL supporting AVX-512, we have not currently implemented it, as it requires a much greater level of finesse with instruction packing. The best AVX-512 software uses hand-crafted intrinsics to provide the instructions, as per our 3PDM AVX-512 test later in the review.

For these comparisons, we will be picking out CPUs from across our dataset to provide context. Some of these might be higher power processors, it should be noted.

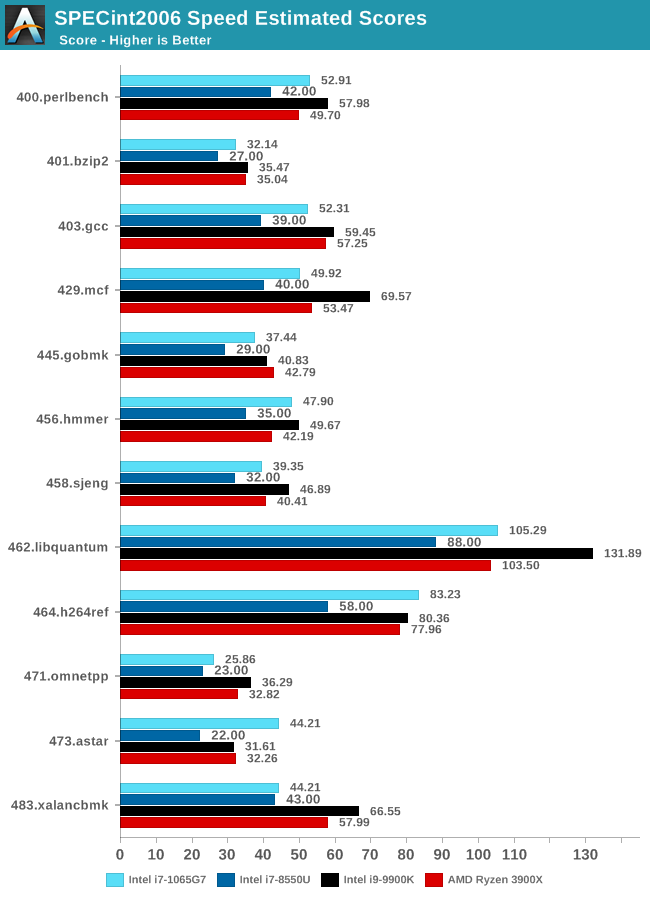

SPECint2006

Amongst SPECint2006, the one benchmark that really stands out beyond all the rest is the 473.astar. Here the new Sunny Cove core is showcasing some exceptional IPC gains, nearly doubling the performance over the 8550U even though it’s clocked 100MHz lower. The benchmark is extremely branch misprediction sensitive, and the only conclusion we can get to rationalise this increase is that the new branch predictors on Sunny Cove are doing an outstanding job and represent a massive improvement over Skylake.

456.hmmer and 464.h264ref are very execution bound and have the highest actual instructions per clock metrics in this suite. Here it’s very possible that Sunny Cove’s vastly increased out-of-order window is able to extract a lot more ILP out of the program and thus gain significant increases in IPC. It’s impressive that the 3.9GHz core here manages to match and outpace the 9900K’s 5GHz Skylake core.

Other benchmarks here which are limited by other µarch characteristics have various increases depending on the workload. Sunny Cove doubled L2 cache should certainly help with workloads like 403.gcc and others. However because we’re also memory latency limited on this platform the increases aren’t quite as large as we’d expect from a desktop variant of ICL.

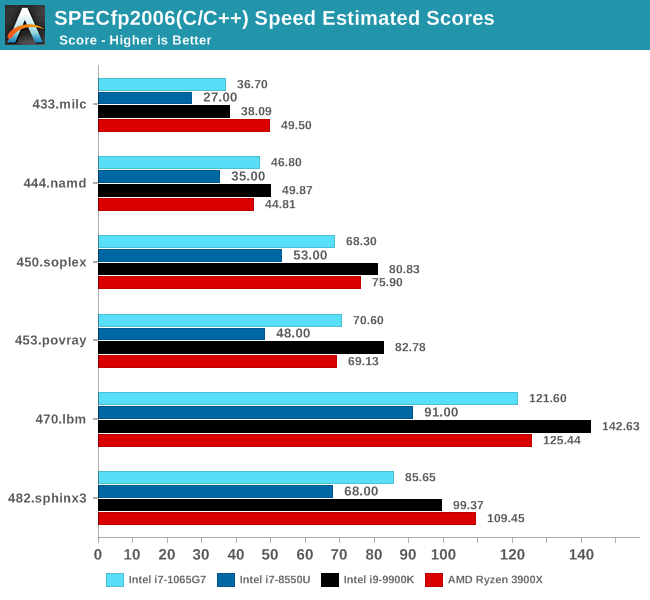

In SPECfp2006, Sunny Cove’s wider out-of-order window can again be seen in tests such as 453.povray as the core is posting some impressive gains over the 8550U at similar clocks. 470.lbm is also instruction window as well as data store heavy – the core’s doubled store bandwidth here certainly helps it.

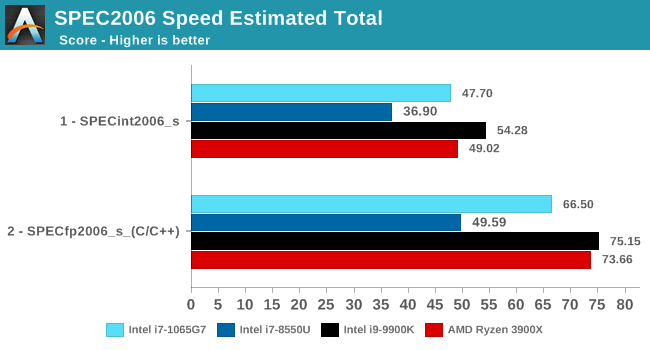

Overall in SPEC2006, the new i7-1065G7 beats a similarly clocked i7-8550U by a hefty 29% in the int suite and 34% in the fp suite. Of course this performance gap will be a lot smaller against 9th gen mobile H-parts at higher clocks, but these are also higher TDP products.

The 1065G7 comes quite close to the fastest desktop parts, however it’s likely it’ll need a desktop memory subsystem in order to catch up in total peak absolute performance.

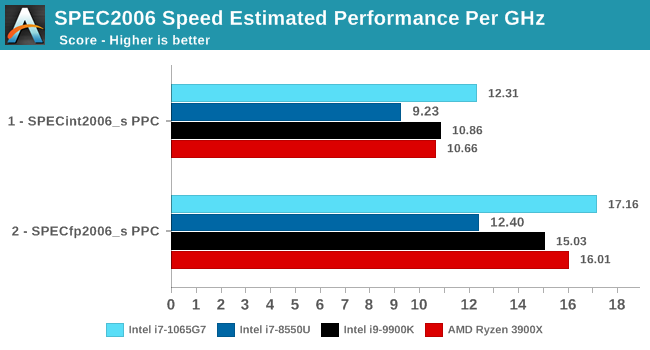

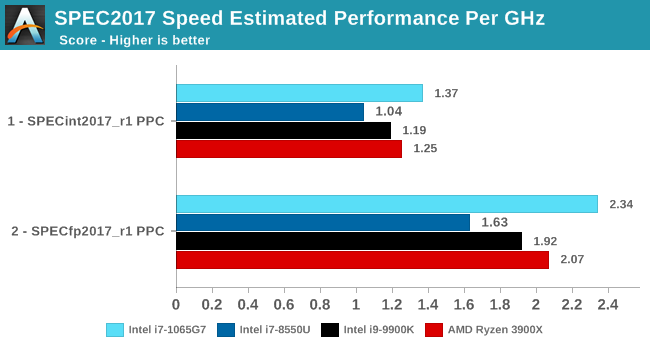

Performance per clock increases on the new Sunny Cove architecture are outstandingly good. IPC increases against the mobile Skylake are 33 and 38% in the integer and fp suites, though we also have to keep in d mind these figures go beyond just the Sunny Cove architecture and also include improvements through the new LPDDR4X memory controllers.

Against a 9900K, although apples and oranges, we’re seeing 13% and 14% IPC increases. These figures likely would be higher on an eventual desktop Sunny Cove part.

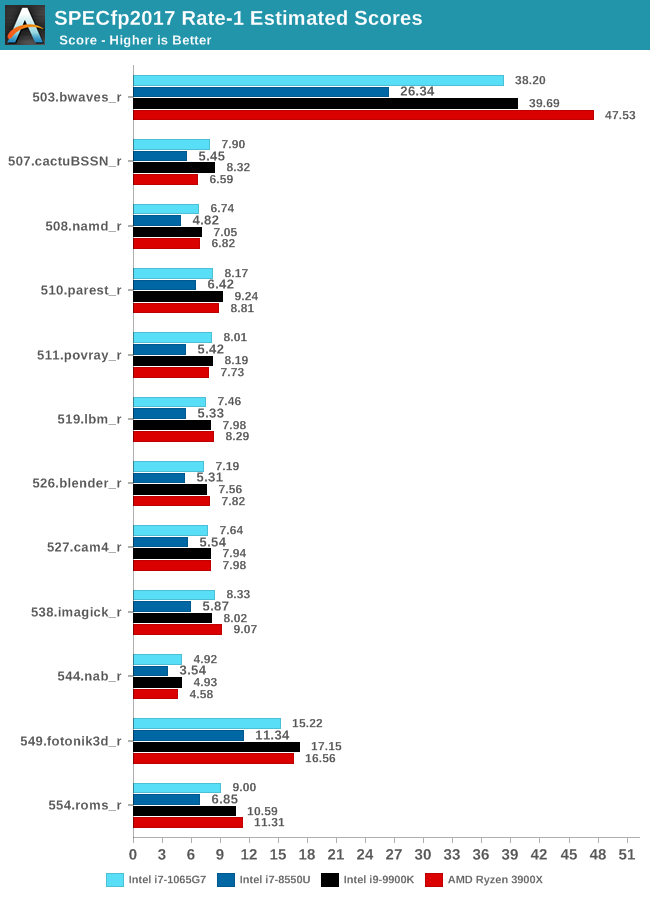

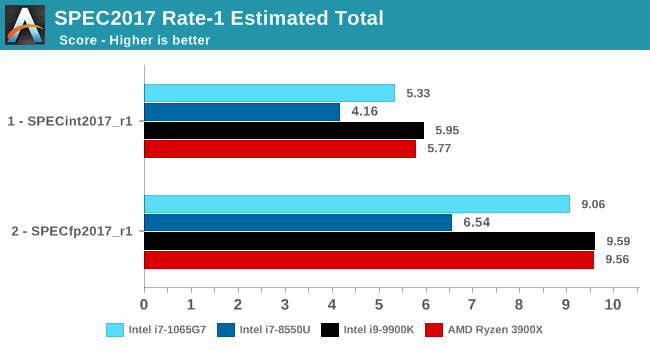

SPEC2017

The SPEC2017 results look similar to the 2006 ones. Against the 8550U, we’re seeing grand performance uplifts, just shy of the best desktop processors.

Here the IPC increase also look extremely solid. In the SPECin2017 suite the Ice Lake part achieves a 14% increase over the 9900K, however we also see a very impressive 21% increase in the fp suite.

Overall in the 2017 suite, we’re seeing a 19% increase in IPC over the 9900K, which roughly matches Intel’s advertised metric of 18% IPC increase.

261 Comments

View All Comments

Xyler94 - Sunday, August 4, 2019 - link

Slower in games, faster in almost everything else (when the R7 1800X came out, the i7 at the time was the i7 7700k)Just like today, the Ryzen 9 3900x is slightly slower in most games (beating it in others) while smashing the i9 9900k in almost any other task. Funny how now we have two CPUs for two different things, huh? Competition is good~

Thunder 57 - Sunday, August 4, 2019 - link

No point in trying to talk sense into a grade A troll. You would think AMD beat him with a belt as a kid or something.Korguz - Friday, August 2, 2019 - link

um HStewart, " Big difference is power difference 0 series are 9V while U is 15/28 and also 28." 9 volts??? again.. do you NOT not know the difference between WATTS and VOLTS ?? i guess by YOUR logic, U uses 15 and 28 VOLTS ????quadibloc - Friday, August 2, 2019 - link

It's easy to focus on AMD and say that the reason Intel didn't do a pure "tick" release this time was because it couldn't afford to pass up any opportunity for improvement in a more competitive environment. But this forgets another factor: during the years of the "tick-tock" strategy, Dennard Scaling was operative, so a process shrink of itself brought a major performance improvement.Now, without Dennard Scaling, even without serious competition from AMD, if Intel had brought out a process shrink without architectural improvements, people would have said "What's the point?".

0ldman79 - Friday, August 2, 2019 - link

Ignore the whiners.Good tech preview.

Looking forward to a full on review.

The SPEC numbers vs the 3900x are pretty insane. Is that single thread or what? Are the benches short enough to run within the max turbo power envelope?

I'm trying to understand how a 15W Ice Lake and 15W Whiskey Lake are comparable to a 9900K or 3900x.

Alistair - Friday, August 2, 2019 - link

Of course it is single threaded (Hence Ian saying words like IPC in that section). There are 0 reasons you'd pick this CPU to compete against the 3900x in multi core workloads.Phynaz - Friday, August 2, 2019 - link

Show me a laptop with a 3900x.Thought so.

Idiot.

Alistair - Saturday, August 3, 2019 - link

Are you dumb? Single core performance is equal, not multicore (it is 1/3 the speed).Xyler94 - Sunday, August 4, 2019 - link

Show me a laptop with an i9 9900ks which can handle the insane tdp it needs.Thought so,

Idiot

R6E7980XE - Saturday, August 3, 2019 - link

“For Sunny Cove this has increased, but it gets a bit more complicated. In one clock Sunny cove can perform 2x64-byte reads and either 1x64-byte write, or 1x32-byte write, or 2x16-byte writes.”@Ian Cuttress Please correct me if I’m remember wrong.

Sunny Cove Microarchitect consisted 2 x 64 Byte / cycle Load and 2 x 64 Byte / cycle Store.

according to https://en.wikichip.org/wiki/File:sunny_cove_block...